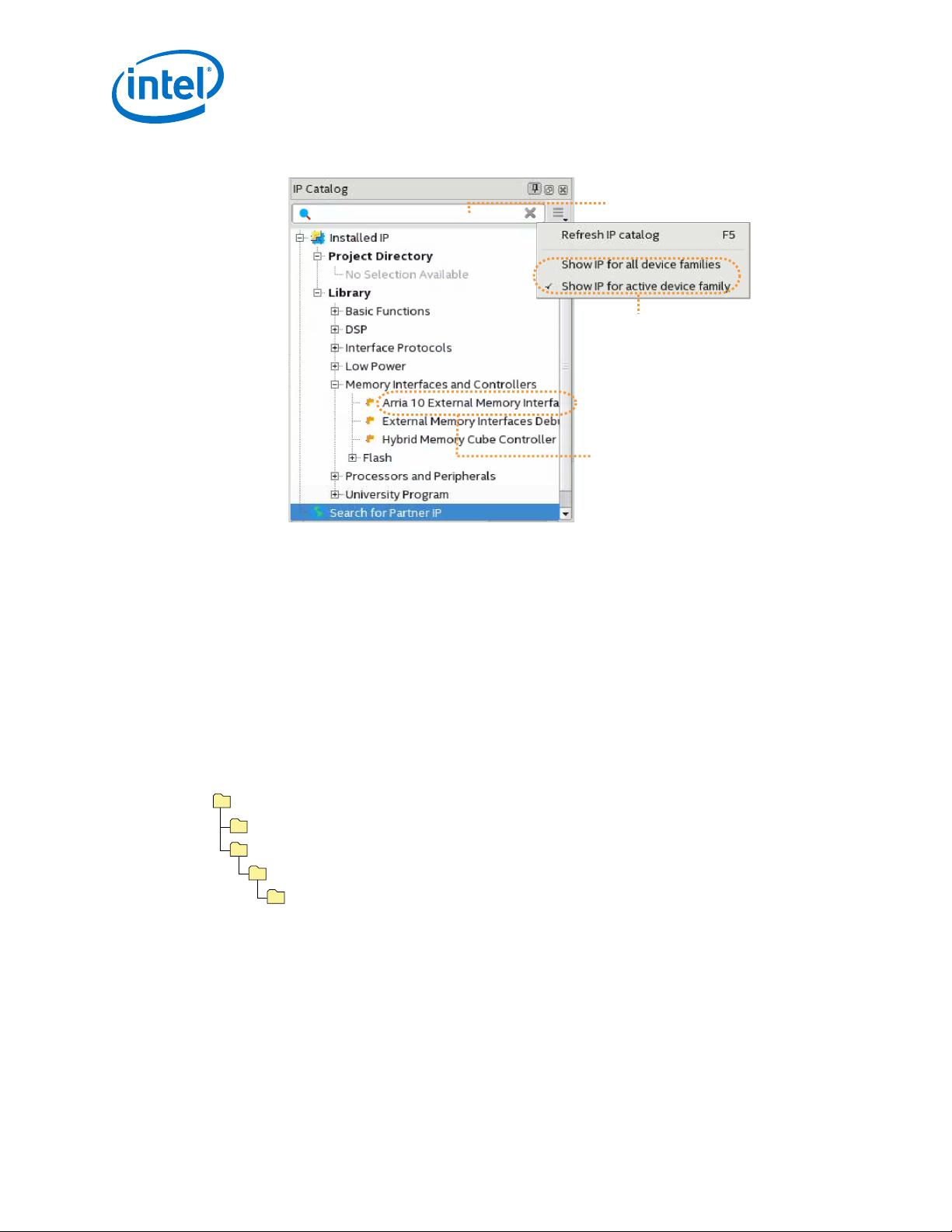

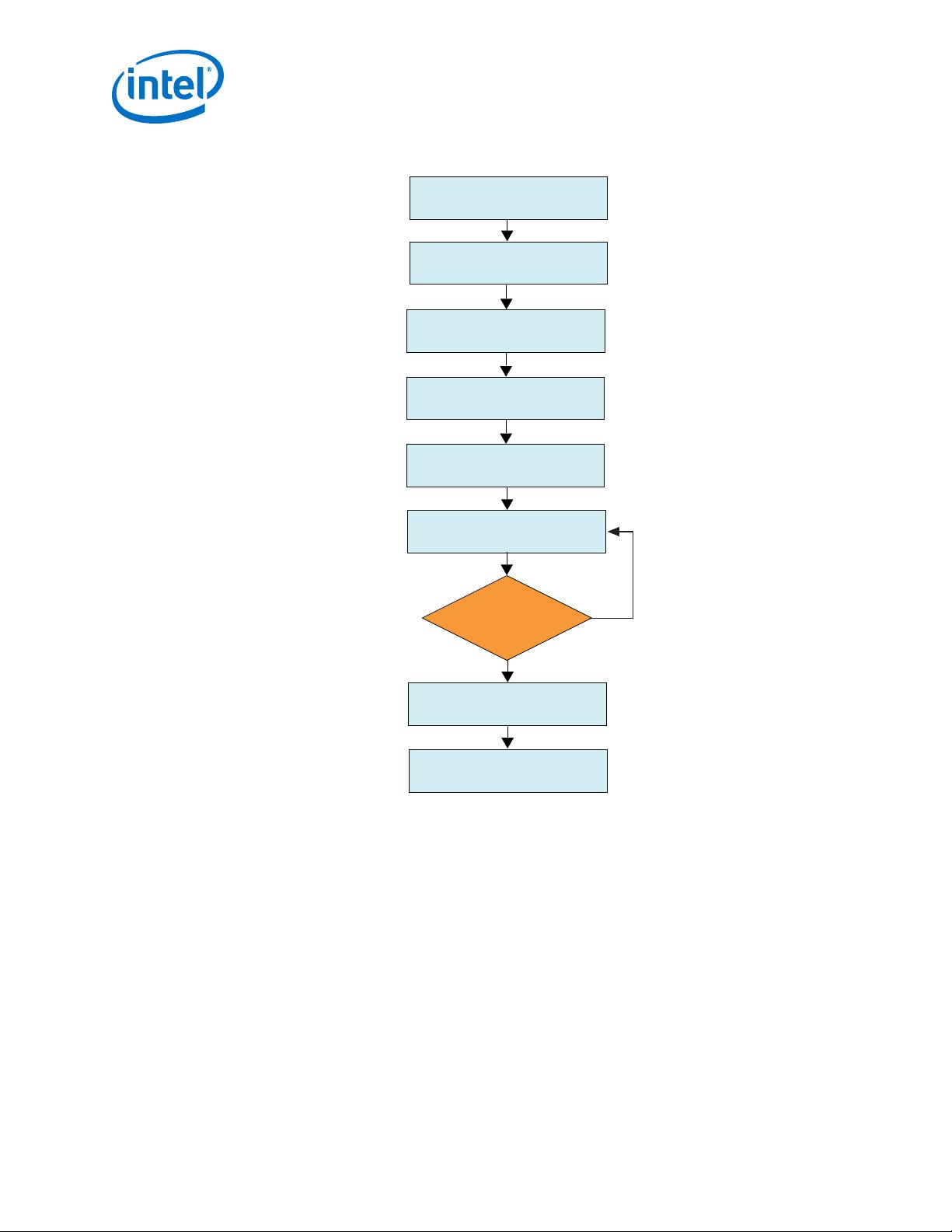

本资源是Altera FPGA的JESD204B IP核用户手册,适用于Intel Quartus Prime Design Suite 17.1版本。JESD204B是一种先进的高速串行电气信号接口标准(SerDes),专用于模拟数字转换器(ADC)和数字模拟转换器(DAC)之间的数据传输,特别适用于需要高带宽和低时延应用的领域,如通信系统、图像处理和数据中心接口。 在手册的第1部分,"JESD204B IP Core Quick Reference"提供了一个快速指南,概述了核心功能和特性。这部分可能包括接口速率、数据格式支持以及主要功能模块的简要介绍。 用户手册的第2章详细阐述了JESD204B IP Core的各个方面。首先,"Data Path Modes"解释了核心的不同工作模式,可能涉及单通道、双通道或多通道配置,以及它们各自的应用场景。接下来,"IP Core Variation"讨论了核心的不同变体,可能涉及不同的功能特性和性能优化。 "JESD204B IP Core Configuration"是关键章节,讲述了如何在运行时进行配置,包括设置数据速率、采样率、位深度等参数。此外,手册还涵盖了"Channel Bonding"技术,即如何在多个通道上并行传输数据以提高带宽。 性能和资源利用率在"Performance and Resource Utilization"部分被详细分析,帮助用户了解设计的效率和对FPGA资源的需求。这对于优化硬件设计和选择合适的FPGA型号至关重要。 "Getting Started"部分是新手的向导,包括如何安装和许可Intel FPGA IP Core,使用Intel FPGA IPEvaluation Mode进行评估,以及升级IP Core的方法。此外,手册还指导用户如何在Quartus Prime环境中创建项目、参数化IP Core、编译设计和下载到FPGA设备。 "Design Considerations"深入探讨了如何在平台设计者工具中集成JESD204B IP Core,如何正确分配pin,以及是否需要添加外部时钟发生器。对于输入时钟的定时约束也给出了重要建议,确保信号完整性。 "JESD204B IP Core Parameters"列出了所有可配置的参数及其作用,允许用户根据具体应用调整性能和行为。这部分内容对于精确控制IP Core的功能和性能至关重要。 本用户手册提供了关于Altera FPGA的JESD204B IP Core全面的指南,包括其工作原理、配置选项、集成策略以及使用过程中的注意事项,是设计人员进行高速串行数据传输接口设计的宝贵参考资料。

剩余115页未读,继续阅读

- 粉丝: 2

- 资源: 5

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- IPQ4019 QSDK开源代码资源包发布

- 高频组电赛必备:掌握数字频率合成模块要点

- ThinkPHP开发的仿微博系统功能解析

- 掌握Objective-C并发编程:NSOperation与NSOperationQueue精讲

- Navicat160 Premium 安装教程与说明

- SpringBoot+Vue开发的休闲娱乐票务代理平台

- 数据库课程设计:实现与优化方法探讨

- 电赛高频模块攻略:掌握移相网络的关键技术

- PHP简易简历系统教程与源码分享

- Java聊天室程序设计:实现用户互动与服务器监控

- Bootstrap后台管理页面模板(纯前端实现)

- 校园订餐系统项目源码解析:深入Spring框架核心原理

- 探索Spring核心原理的JavaWeb校园管理系统源码

- ios苹果APP从开发到上架的完整流程指南

- 深入理解Spring核心原理与源码解析

- 掌握Python函数与模块使用技巧

信息提交成功

信息提交成功