没有合适的资源?快使用搜索试试~ 我知道了~

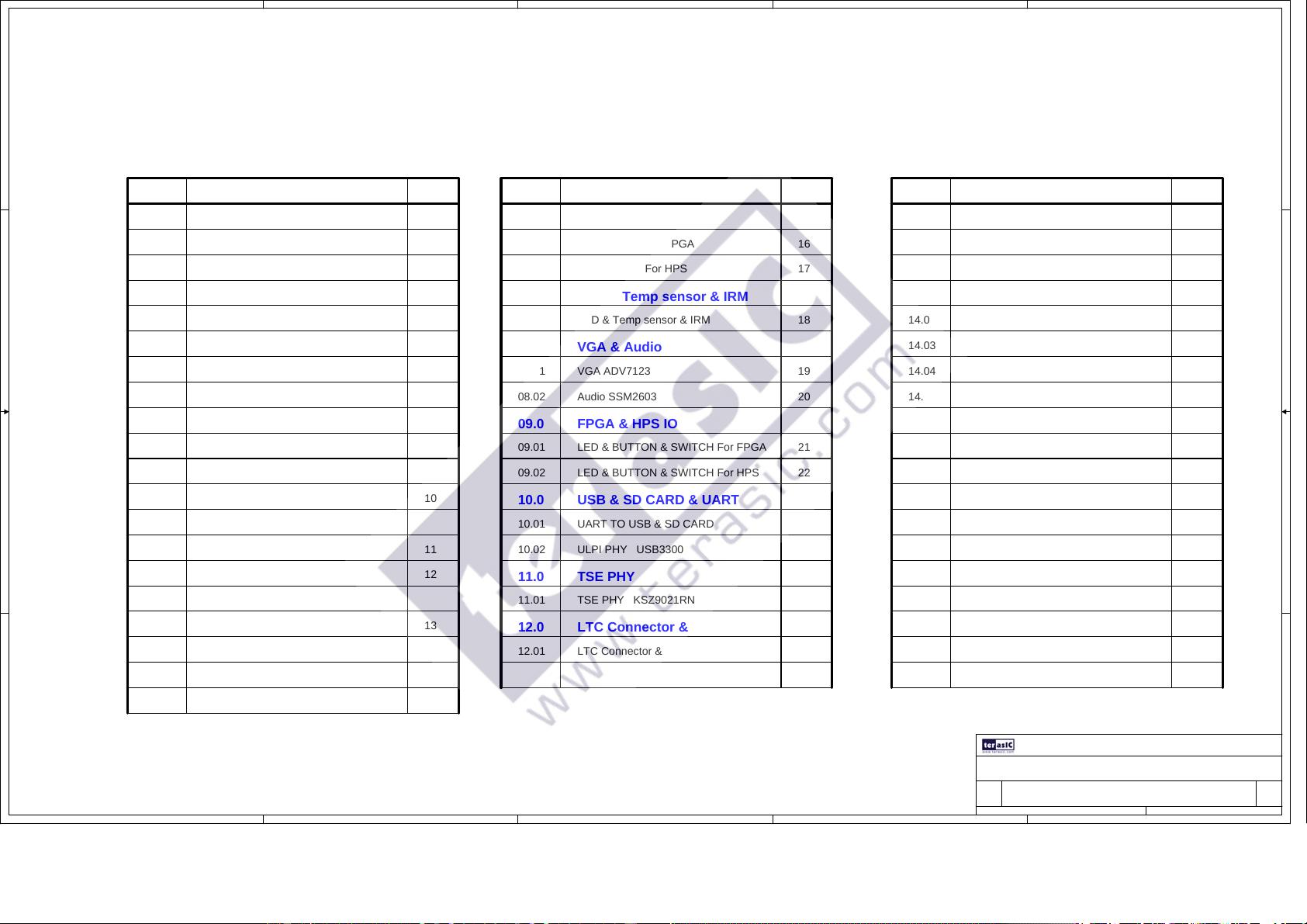

首页Cyclone V开发板原理图

资源详情

资源评论

资源推荐

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

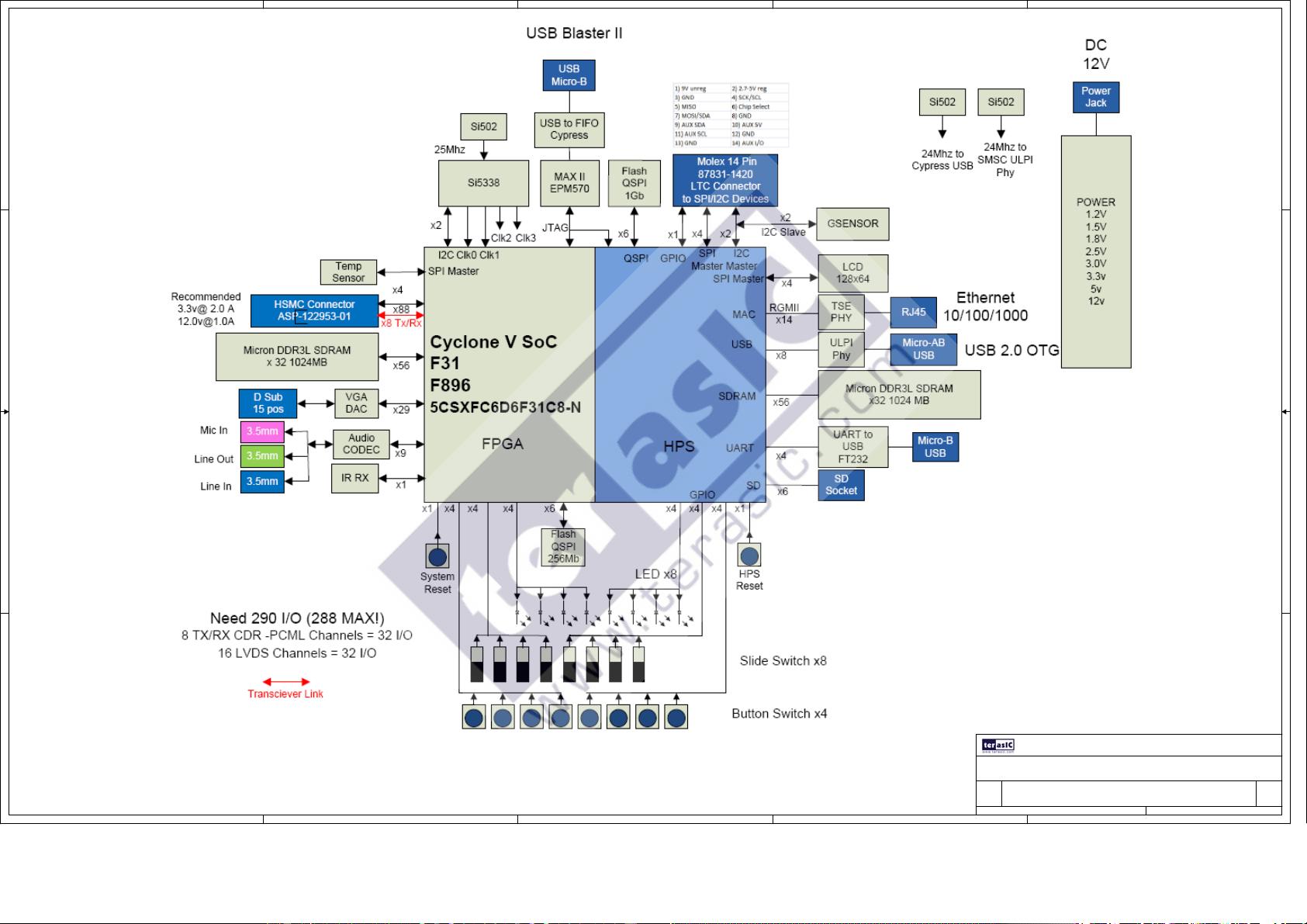

SoCKit

9V & 5V

1.1V & 1.2V

3.3V & 2.5V

1.5V

28

29

14.03

14.04

HSMC_VCCIO14.05

30

31

12

02.01

02.05 Transceiver

802.06

03.01

03.02

USB Blaster II

JTAG Chain

04.01

03.0

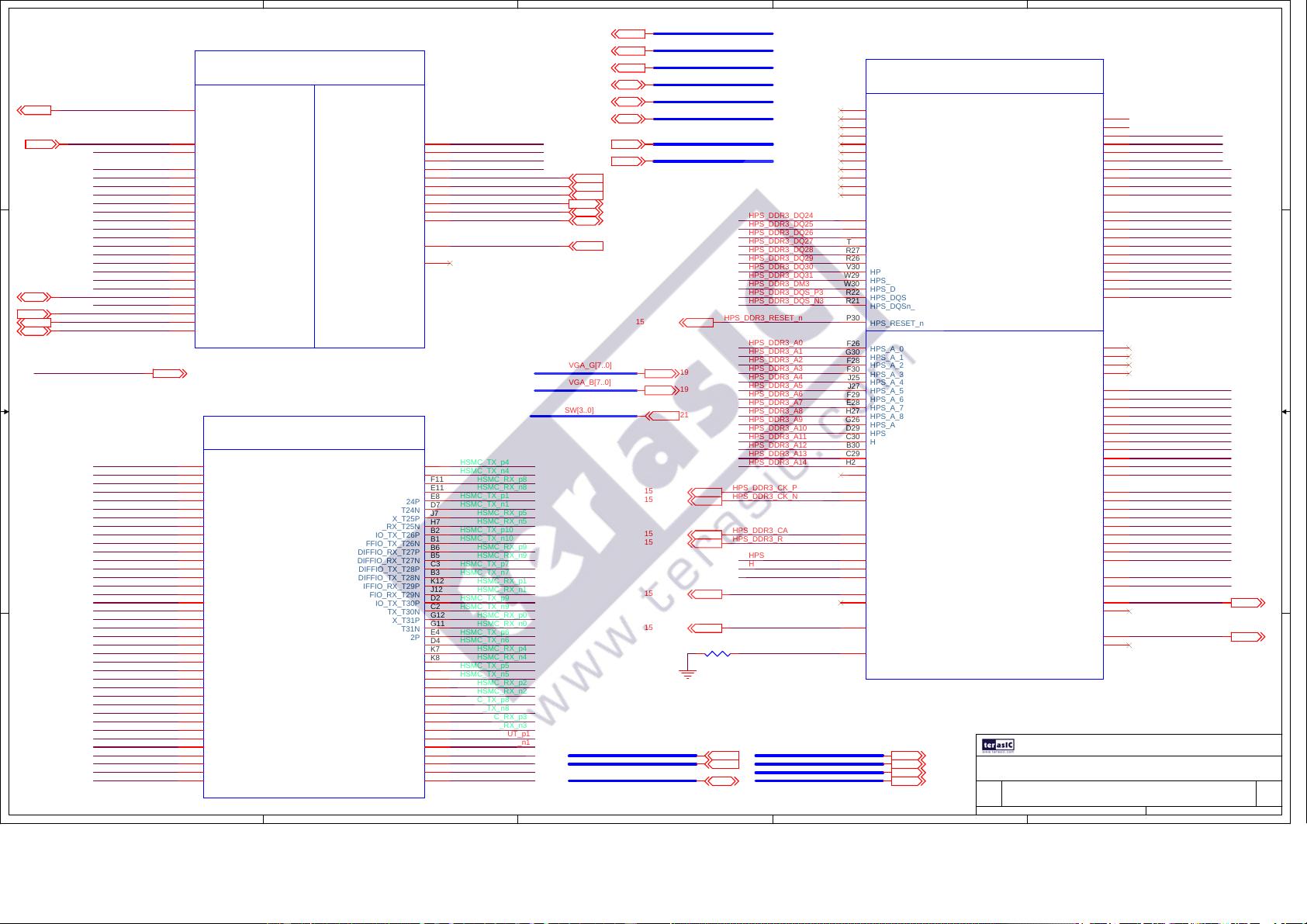

HSMC

1

Page

JTAG

15

11

02.0

01.0

Title

Cover Page

Section

Block Diagram

1.01

2

Design Introduction

4

3

1.02

6

5

7

Cyclone V EP5CSXFC6DF31

BANK5 & BANK6 & BANK802.02

BANK3 & BANK4

02.04

02.03 BANK7

Clock & GND

Config

04.0 Expansion Port

05.0 Memory

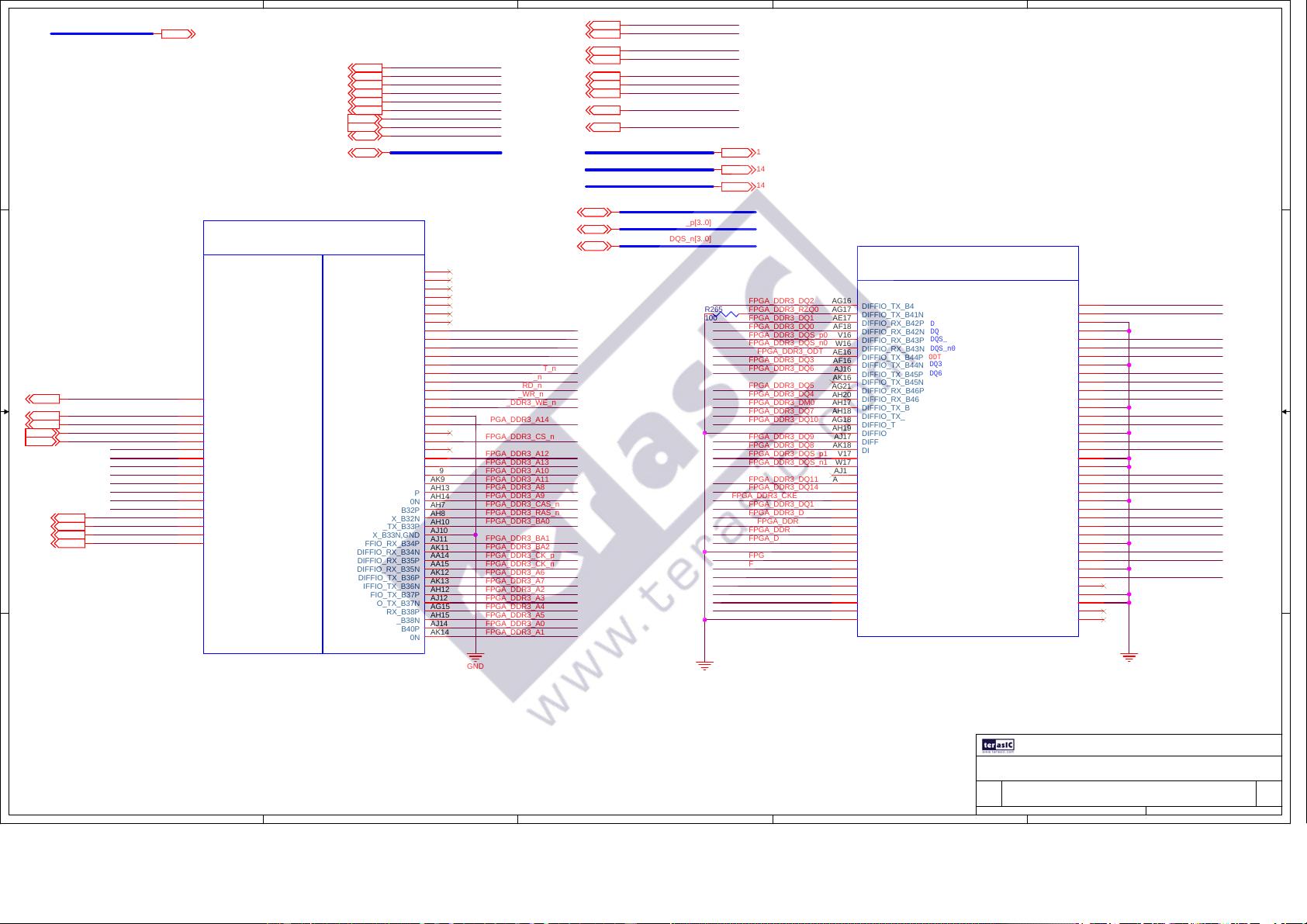

05.01 DDR3L SDRAM For FPGA

05.02 DDR3L SDRAM For HPS

07.01

20

08.01

08.02

LED & BUTTON & SWITCH For HPS

VGA ADV7123

09.02

Audio SSM2603

09.01

08.0

LED & BUTTON & SWITCH For FPGA

Page

VGA & Audio

22

23

24

07.0

06.0

Title

QSPI FLASH For FPGA

Section

QSPI FLASH For HPS

06.01 16

Memory 2

1706.02

19

18

LCD & Temp sensor & IRM

LCD & Temp sensor & IRM

09.0 FPGA & HPS IO

10.0 USB & SD CARD & UART

10.01 UART TO USB & SD CARD

10.02 ULPI PHY USB3300

11.0 TSE PHY

TSE PHY KSZ9021RN11.01

12.01

12.0 LTC Connector & G Sensor

LTC Connector & G Sensor

13

14

25

21

Page

14.0

TitleSection

System Power

14.01

14.02

26

27

Power

Decoupling

02.07

02.08

9

10

Soft ADC & DAC

13.0 ADC & DAC

13.01

32

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page D

SoCKit Board

B

132Wednesday, May 21, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page D

SoCKit Board

B

132Wednesday, May 21, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page D

SoCKit Board

B

132Wednesday, May 21, 2014

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram D

SoCKit Board

B

232Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram D

SoCKit Board

B

232Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram D

SoCKit Board

B

232Monday, December 09, 2013

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ22

DQ21

DQ20

DQ23

DQ26

DQ25

DQ24

DQ27

DQ30

DQ29

DQ28

DQS_p0

DQS_n0

DQS_p1

DQS_n1

DQS_p2

DQS_n2

DQS_p3

DQS_n3

ODT

DM0

DM1

DM3

DM2

DQ31

3.3V 1.5V 1.5V

VGA_R5

VGA_R7

VGA_R6

VGA_R0

VGA_R4

VGA_R3

VGA_R2

VGA_R1

FPGA_DDR3_RZQ0

USB_FULL

USB_EMPTY

USB_SCL

USB_SDA

USB_B2_CLK

USB_RESET_n

USB_OE_n

USB_RD_n

USB_WR_n

FPGA_DDR3_A1

FPGA_DDR3_A0

FPGA_DDR3_A5

FPGA_DDR3_A4

FPGA_DDR3_A3

FPGA_DDR3_A2

FPGA_DDR3_A7

FPGA_DDR3_A6

FPGA_DDR3_CK_n

FPGA_DDR3_CK_p

FPGA_DDR3_BA2

FPGA_DDR3_BA1

FPGA_DDR3_BA0

FPGA_DDR3_RAS_n

FPGA_DDR3_CAS_n

FPGA_DDR3_A9

FPGA_DDR3_A8

FPGA_DDR3_A11

FPGA_DDR3_A10

FPGA_DDR3_A13

FPGA_DDR3_A12

FPGA_DDR3_CS_n

FPGA_DDR3_WE_n

FPGA_DDR3_A14

FPGA_DDR3_DQ22

FPGA_DDR3_DQ19

FPGA_DDR3_RESET_n

FPGA_DDR3_DQS_n2

FPGA_DDR3_DQ18

FPGA_DDR3_DQ15

FPGA_DDR3_DM1

FPGA_DDR3_DQ12

FPGA_DDR3_DQ13

FPGA_DDR3_CKE

FPGA_DDR3_DQ14

FPGA_DDR3_DQ11

FPGA_DDR3_DQS_n1

FPGA_DDR3_DQS_p1

FPGA_DDR3_DQ8

FPGA_DDR3_DQ10

FPGA_DDR3_DQ7

FPGA_DDR3_DM0

FPGA_DDR3_DQ4

FPGA_DDR3_DQ5

FPGA_DDR3_DQ6

FPGA_DDR3_DQ3

FPGA_DDR3_ODT

FPGA_DDR3_DQS_n0

FPGA_DDR3_DQS_p0

FPGA_DDR3_DQ0

FPGA_DDR3_DQ2

FPGA_DDR3_DQ1

FPGA_DDR3_DQ9

FPGA_DDR3_DQ17

FPGA_DDR3_DQ16

FPGA_DDR3_DQS_p2

FPGA_DDR3_DQ21

FPGA_DDR3_DQ20

FPGA_DDR3_DM2

FPGA_DDR3_DQ23

FPGA_DDR3_DQ25

FPGA_DDR3_DQ24

FPGA_DDR3_DQS_p3

FPGA_DDR3_DQS_n3

FPGA_DDR3_DQ27

FPGA_DDR3_DQ30

FPGA_DDR3_DQ29

FPGA_DDR3_DQ28

FPGA_DDR3_DM3

FPGA_DDR3_DQ31

FPGA_DDR3_DQ26

USB_B2_DATA7

USB_B2_DATA4

USB_B2_DATA3

USB_B2_DATA2

USB_B2_DATA1

USB_B2_DATA0

USB_B2_DATA5

USB_B2_DATA6

GND

GND

GND

VGA_R[7..0]

19

VGA_VS

19

VGA_HS

19

VGA_SYNC_n

19

VGA_BLANK_n

19

TEMP_CS_n

18

TEMP_DIN

18

TEMP_DOUT

18

IRDA_RXD

18

TEMP_SCLK

18

FPGA_DDR3_DQ[31..0]

14

FPGA_DDR3_DQS_p[3..0]

14

FPGA_DDR3_DQS_n[3..0]

14

FPGA_DDR3_DM[3..0]

14

FPGA_DDR3_A[14..0]

14

FPGA_DDR3_CK_p

14

FPGA_DDR3_CK_n

14

FPGA_DDR3_CKE

14

FPGA_DDR3_CS_n

14

USB_SCL

11

USB_FULL

11

USB_EMPTY

11

USB_WR_n

11

USB_RD_n

11

USB_OE_n

11

USB_RESET_n

11

USB_B2_CLK

11

USB_SDA

11

USB_B2_DATA[7..0]

11

FPGA_DDR3_RESET_n

14

FPGA_DDR3_WE_n

14

FPGA_DDR3_RAS_n

14

FPGA_DDR3_CAS_n

14

FPGA_DDR3_ODT

14

FPGA_DDR3_BA[2..0]

14

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK3 & BANK4 D

SoCKit Board

B

332Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK3 & BANK4 D

SoCKit Board

B

332Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK3 & BANK4 D

SoCKit Board

B

332Monday, December 09, 2013

R265

100

BANK 3

BANK 3A BANK 3B

5CSXFC6DF31

U25C

DIFFIO_TX_B8P

AF9

DIFFIO_TX_B9P

AF8

DIFFIO_TX_B9N

AG7

DIFFIO_RX_B10P

AG1

DIFFIO_RX_B10N

AH2

DIFFIO_RX_B11P

AA12

DIFFIO_RX_B11N

AB12

DIFFIO_TX_B12P

AF6

DIFFIO_TX_B12N

AG6

DIFFIO_TX_B13P

AG5

DIFFIO_TX_B13N

AH5

DIFFIO_RX_B14P

AJ1

DIFFIO_RX_B14N

AJ2

DIFFIO_RX_B15P

AC12

DIFFIO_RX_B15N

AD12

DIFFIO_TX_B16P

AG2

DIFFIO_TX_B16N

AH3

DIFFIO_TX_B17P

AG10

DIFFIO_TX_B17N

AH9

DIFFIO_RX_B18P

AF11

DIFFIO_RX_B18N

AG11

DIFFIO_RX_B19P

AA13

DIFFIO_RX_B19N

AB13

DIFFIO_TX_B20P

AK2

DIFFIO_TX_B20N

AK3

DIFFIO_TX_B21P

AJ4

DIFFIO_TX_B21N

AK4

DIFFIO_RX_B22P

AE13

DIFFIO_RX_B22N

AF13

DIFFIO_RX_B23P

AD14

DIFFIO_RX_B23N

AE14

DIFFIO_TX_B24P

AJ5

DIFFIO_TX_B24N

AK6

DIFFIO_TX_B25P

AJ6

DIFFIO_TX_B25N,GND

AJ7

DIFFIO_RX_B26P

AG12

DIFFIO_RX_B26N

AG13

DIFFIO_RX_B27P

AB15

DIFFIO_RX_B27N

AC14

DIFFIO_TX_B28P

AK7

DIFFIO_TX_B28N

AK8

DIFFIO_TX_B29P

AJ9

DIFFIO_TX_B29N

AK9

DIFFIO_RX_B30P

AH13

DIFFIO_RX_B30N

AH14

DIFFIO_TX_B32P

AH7

DIFFIO_TX_B32N

AH8

DIFFIO_TX_B33P

AH10

DIFFIO_TX_B33N,GND

AJ10

DIFFIO_RX_B34P

AJ11

DIFFIO_RX_B34N

AK11

DIFFIO_RX_B35P

AA14

DIFFIO_RX_B35N

AA15

DIFFIO_TX_B36P

AK12

DIFFIO_TX_B36N

AK13

DIFFIO_TX_B37P

AH12

DIFFIO_TX_B37N

AJ12

DIFFIO_RX_B38P

AG15

DIFFIO_RX_B38N

AH15

DIFFIO_TX_B40P

AJ14

DIFFIO_TX_B40N

AK14

BANK 4A

5CSXFC6DF31

U25D

DIFFIO_TX_B41N/RZQ_0

AG17

DIFFIO_RX_B42N

AF18

DIFFIO_TX_B41P

AG16

DIFFIO_RX_B42P

AE17

DIFFIO_RX_B43N

W16

DIFFIO_TX_B44N

AF16

DIFFIO_RX_B43P

V16

DIFFIO_TX_B44P

AE16

DIFFIO_TX_B45N

AK16

DIFFIO_RX_B46N

AH20

DIFFIO_TX_B45P

AJ16

DIFFIO_RX_B46P

AG21

DIFFIO_TX_B48N

AH18

DIFFIO_TX_B48P

AH17

DIFFIO_TX_B49N,GND

AH19

DIFFIO_RX_B50N

AK18

DIFFIO_TX_B49P

AG18

DIFFIO_RX_B50P

AJ17

DIFFIO_RX_B51N

W17

DIFFIO_TX_B52N

AK19

DIFFIO_RX_B51P

V17

DIFFIO_TX_B52P

AJ19

DIFFIO_TX_B53N

AJ21

DIFFIO_RX_B54N

AG20

DIFFIO_TX_B53P

AJ20

DIFFIO_RX_B54P

AF19

DIFFIO_TX_B56N

AH24

DIFFIO_TX_B56P

AG23

DIFFIO_TX_B57N,GND

AH22

DIFFIO_RX_B58N

AE19

DIFFIO_TX_B57P

AG22

DIFFIO_RX_B58P

AE18

DIFFIO_RX_B59N

AA18

DIFFIO_TX_B60N

AK22

DIFFIO_RX_B59P

Y17

DIFFIO_TX_B60P

AK21

DIFFIO_TX_B61N,GND

AJ22

DIFFIO_RX_B62N

AF21

DIFFIO_TX_B61P

AH23

DIFFIO_RX_B62P

AF20

DIFFIO_RX_B63N,GND

AA19

DIFFIO_TX_B64N

AK24

DIFFIO_RX_B63P,GND

Y18

DIFFIO_TX_B64P

AK23

DIFFIO_TX_B65N,GND

AJ25

DIFFIO_RX_B66N

AF24

DIFFIO_TX_B65P

AJ24

DIFFIO_RX_B66P

AF23

DIFFIO_RX_B67N

AD19

DIFFIO_TX_B68N

AK26

DIFFIO_RX_B67P

AC20

DIFFIO_TX_B68P,GND

AJ26

DIFFIO_TX_B69N

AH25

DIFFIO_RX_B70N

AE23

DIFFIO_TX_B69P

AG25

DIFFIO_RX_B70P

AE22

DIFFIO_RX_B71N,GND

W19

DIFFIO_TX_B72N

AK27

DIFFIO_RX_B71P,GND

V18

DIFFIO_TX_B72P

AJ27

DIFFIO_TX_B73N,GND

AK29

DIFFIO_RX_B74N

AD21

DIFFIO_TX_B73P

AK28

DIFFIO_RX_B74P

AD20

DIFFIO_RX_B75N

AA20

DIFFIO_TX_B76N

AH27

DIFFIO_RX_B75P

Y19

DIFFIO_TX_B76P,GND

AG26

DIFFIO_TX_B77N,GND

AF26

DIFFIO_RX_B78N

AC23

DIFFIO_TX_B77P

AF25

DIFFIO_RX_B78P

AC22

DIFFIO_RX_B79N,GND

AB21

DIFFIO_TX_B80N

AE24

DIFFIO_RX_B79P,GND

AA21

DIFFIO_TX_B80P

AD24

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

3.3V

HSMC_VCCIO 1.5V

1.5V

HPS_DDR3_RZQ0

HSMC_D2

HSMC_D0

HSMC_RX_p16

HSMC_RX_n16

HSMC_D3

HSMC_D1 HSMC_TX_p2

HSMC_TX_n2

HSMC_RX_p7

HSMC_RX_n7

HSMC_RX_p13

HSMC_RX_n13

HSMC_TX_p15

HSMC_TX_n15

HSMC_RX_p12

HSMC_RX_n12

HSMC_TX_p0

HSMC_TX_n0

HSMC_TX_p13

HSMC_TX_n13

HSMC_RX_p10

HSMC_RX_n10

HSMC_TX_p14

HSMC_TX_n14

HSMC_RX_p15

HSMC_RX_n15

HSMC_RX_p14

HSMC_RX_n14

HSMC_TX_p12

HSMC_TX_n12

HSMC_RX_p6

HSMC_RX_n6

HSMC_TX_p11

HSMC_TX_n11

HSMC_RX_p11

HSMC_RX_n11

HSMC_TX_p4

HSMC_TX_n4

HSMC_RX_p8

HSMC_RX_n8

HSMC_TX_p1

HSMC_TX_n1

HSMC_RX_p5

HSMC_RX_n5

HSMC_TX_p10

HSMC_TX_n10

HSMC_RX_p9

HSMC_RX_n9

HSMC_TX_p7

HSMC_TX_n7

HSMC_RX_p1

HSMC_RX_n1

HSMC_TX_p9

HSMC_TX_n9

HSMC_RX_p0

HSMC_RX_n0

HSMC_TX_p6

HSMC_TX_n6

HSMC_RX_p4

HSMC_RX_n4

HSMC_TX_p5

HSMC_TX_n5

HSMC_RX_p2

HSMC_RX_n2

HSMC_TX_p8

HSMC_TX_n8

HSMC_RX_p3

HSMC_RX_n3

HSMC_CLKOUT_p1

HSMC_CLKOUT_n1

HSMC_TX_p3

HSMC_TX_n3

HSMC_CLKOUT_p2

HSMC_CLKOUT_n2

HSMC_TX_p16

HSMC_TX_n16

H_KEY2

H_KEY0

H_KEY1

H_KEY3

SW0

SW1

SW2

SW3

AUD_MUTE

VGA_G0

VGA_G1

VGA_G2

VGA_G3

VGA_G4

VGA_G5

VGA_G6

VGA_G7

VGA_B0

VGA_B1

VGA_B2

VGA_B3

VGA_B4

VGA_B5

VGA_B6

VGA_B7

HPS_DDR3_DQ24

HPS_DDR3_DQ25

HPS_DDR3_DQ26

HPS_DDR3_DQ27

HPS_DDR3_DQ28

HPS_DDR3_DQ29

HPS_DDR3_DQ30

HPS_DDR3_DQ31

HPS_DDR3_DM3

HPS_DDR3_DQS_P3

HPS_DDR3_DQS_N3

HPS_DDR3_DQ16

HPS_DDR3_DQ17

HPS_DDR3_DQ18

HPS_DDR3_DQ19

HPS_DDR3_DQ20

HPS_DDR3_DQ21

HPS_DDR3_DQ22

HPS_DDR3_DQ23

HPS_DDR3_DM2

HPS_DDR3_DQS_P2

HPS_DDR3_DQS_N2

HPS_DDR3_A0

HPS_DDR3_A1

HPS_DDR3_A2

HPS_DDR3_A3

HPS_DDR3_A4

HPS_DDR3_A5

HPS_DDR3_A6

HPS_DDR3_A7

HPS_DDR3_A8

HPS_DDR3_A9

HPS_DDR3_A10

HPS_DDR3_DQ8

HPS_DDR3_DQ9

HPS_DDR3_DQ10

HPS_DDR3_DQ11

HPS_DDR3_DQ12

HPS_DDR3_DQ13

HPS_DDR3_DQ14

HPS_DDR3_DQ15

HPS_DDR3_DM1

HPS_DDR3_DQS_P1

HPS_DDR3_DQS_N1

HPS_DDR3_DQ0

HPS_DDR3_DQ1

HPS_DDR3_DQ2

HPS_DDR3_DQ3

HPS_DDR3_DQ4

HPS_DDR3_DQ5

HPS_DDR3_DQ6

HPS_DDR3_DQ7

HPS_DDR3_DM0

HPS_DDR3_DQS_P0

HPS_DDR3_DQS_N0

HPS_DDR3_A11

HPS_DDR3_A12

HPS_DDR3_A13

HPS_DDR3_A14

HPS_DDR3_BA1

HPS_DDR3_BA0

HPS_DDR3_BA2

H_SW3

H_SW2

H_SW1

H_SW0

GND

H_SW[3..0]

22

HPS_DDR3_CK_P

15

HPS_DDR3_CK_N

15

HPS_DDR3_CAS_n

15

HPS_DDR3_RAS_n

15

HPS_DDR3_CS_n

15

AUD_ADCLRCK

20

AUD_ADCDAT

20

HPS_DDR3_RESET_n

15

HPS_DDR3_WE_n

15

HPS_DDR3_CKE

15

AUD_I2C_SDAT

20

AUD_I2C_SCLK

20

H_KEY[3..0]

22

AUD_MUTE

20

VGA_G[7..0]

19

VGA_B[7..0]

19

HPS_DDR3_ODT

15

VGA_CLK

19

SW[3..0]

21

HPS_DDR3_DQS_N[3..0]

15

HPS_DDR3_DQS_P[3..0]

15

HPS_DDR3_DQ[31..0]

15

HPS_DDR3_DM[3..0]

15

HPS_DDR3_BA[2..0]

15

HPS_DDR3_A[14..0]

15

HSMC_D[3..0]

13

HSMC_RX_p[16..0]

8,13

HSMC_RX_n[16..0]

8,13

HSMC_TX_n[16..0]

13

HSMC_TX_p[16..0]

13

HSMC_CLKOUT_n[2..1]

13

HSMC_CLKOUT_p[2..1]

13

FAN_CTRL

8

HSMC_SCL

13

HSMC_SDA

13

HSMC_CLK_OUT0

13

5B_BANK_AB30

27

5B_BANK_AA30

27

5B_BANK_AB28

27

5B_BANK_AD30

27

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK5 / BANK6 / BANK8 D

SoCKit Board

B

432Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK5 / BANK6 / BANK8 D

SoCKit Board

B

432Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK5 / BANK6 / BANK8 D

SoCKit Board

B

432Monday, December 09, 2013

BANK 5

BANK 5A BANK 5B

5CSXFC6DF31

U25E

DIFFIO_TX_R1P/RZQ_1

AG27

DIFFIO_RX_R4P

W20

DIFFIO_RX_R4N

Y21

DIFFIO_TX_R7P

AA25

DIFFIO_RX_R8P

AB22

DIFFIO_TX_R7N

AB26

DIFFIO_RX_R8N

AB23

DIFFIO_RX_R9P

AA24

DIFFIO_TX_R10P

AE27

DIFFIO_RX_R9N

AB25

DIFFIO_TX_R10N

AE28

DIFFIO_RX_R11P

Y23

DIFFIO_TX_R12P

AG28

DIFFIO_RX_R11N

Y24

DIFFIO_TX_R12N

AF28

DIFFIO_RX_R13P

V23

DIFFIO_TX_R14P

AF29

DIFFIO_RX_R13N

W24

DIFFIO_TX_R14N

AF30

DIFFIO_RX_R15P

AD26

DIFFIO_TX_R16P

AH30

DIFFIO_RX_R15N

AC27

DIFFIO_TX_R16N

AG30

DIFFIO_RX_R17P

W25

DIFFIO_TX_R18P

AC28

DIFFIO_RX_R17N

V25

DIFFIO_TX_R18N

AC29

DIFFIO_RX_R19P

AB30

DIFFIO_TX_R20P

AB28

DIFFIO_RX_R19N

AA30

DIFFIO_TX_R20N

AA28

DIFFIO_TX_R22P

AE29

DIFFIO_TX_R22N

AD29

DIFFIO_TX_R24P

AD30

DIFFIO_TX_R24N/RZQ_2

AC30

BANK 6

BANK 6A

BANK 6B

5CSXFC6DF31

U25F

HPS_DM_4

W27

HPS_DQ_39

Y29

HPS_DQ_37

U25

HPS_DQ_38

V27

HPS_DQ_36

T25

HPS_DQS_4

T24

HPS_DDR,HPS_GPI13

Y28

HPS_DQSn_4

T23

HPS_DQ_35

V28

HPS_DQ_33

R24

HPS_DQ_34

U27

HPS_DQ_32

W26

HPS_DDR,HPS_GPI12

V29

HPS_DDR,HPS_GPI11

U20

HPS_DM_3

W30

HPS_DDR,HPS_GPI10

T21

HPS_DQ_31

W29

HPS_DQ_29

R26

HPS_DQ_30

V30

HPS_DQ_28

R27

HPS_DQS_3

R22

HPS_DDR,HPS_GPI9

U28

HPS_DQSn_3

R21

HPS_DQ_27

T28

HPS_DQ_25

P25

HPS_DQ_26

T29

HPS_DQ_24

P24

HPS_DDR,HPS_GPI8

T30

HPS_DDR,HPS_GPI7

V20

HPS_DM_2

R28

HPS_DDR,HPS_GPI6

P22

HPS_DQ_23

R29

HPS_DQ_21

P27

HPS_DQ_22

N27

HPS_DQ_20

P26

HPS_DDR,HPS_GPI5

P29

HPS_DQS_2

R19

HPS_RESET_n

P30

HPS_DQSn_2

R18

HPS_DQ_19

N28

HPS_DQ_17

T26

HPS_DQ_18

N29

HPS_DQ_16

U26

HPS_DDR,HPS_GPI4

N30

HPS_DDR,HPS_GPI3

M22

HPS_DM_1

M28

HPS_DDR,HPS_GPI2

N23

HPS_DQ_15

M30

HPS_DQ_13

M27

HPS_DQ_14

L28

HPS_DQ_12

M26

HPS_CKE_0

L29

HPS_DQS_1

N25

HPS_CKE_1

L30

HPS_DQSn_1

N24

HPS_DQ_11

K27

HPS_DQ_9

L26

HPS_DQ_10

K29

HPS_DQ_8

K26

HPS_DDR,HPS_GPI1

J26

HPS_DDR,HPS_GPI0

M25

HPS_DM_0

K28

HPS_DQ_7

J29

HPS_DQ_5

L24

HPS_DQ_6

J30

HPS_DQ_4

L25

HPS_ODT_1

H29

HPS_DQS_0

N18

HPS_ODT_0

H28

HPS_DQSn_0

M19

HPS_DQ_3

G28

HPS_DQ_1

K22

HPS_DQ_2

H30

HPS_DQ_0

K23

HPS_A_0

F26

HPS_A_1

G30

HPS_A_4

J25

HPS_A_2

F28

HPS_A_5

J27

HPS_A_3

F30

HPS_CK

M23

HPS_A_6

F29

HPS_CK_n

L23

HPS_A_7

E28

HPS_BA_1

J24

HPS_BA_0

E29

HPS_BA_2

J23

HPS_CAS_n

E27

HPS_RAS_n

D30

HPS_A_8

H27

HPS_A_10

D29

HPS_A_9

G26

HPS_A_11

C30

HPS_CS_n0

H24

HPS_A_12

B30

HPS_CS_n1

K21

HPS_A_13

C29

HPS_A_14

H25

HPS_WE_n

C28

HPS_A_15

G25

HPS_RZQ_0

D27

BANK 8A

5CSXFC6DF31

U25H

DIFFIO_TX_T2P

B13

DIFFIO_TX_T2N

A13

DIFFIO_RX_T3P

C13

DIFFIO_TX_T4P

A11

DIFFIO_RX_T3N

B12

DIFFIO_TX_T4N

A10

DIFFIO_RX_T5P

F15

DIFFIO_TX_T6P

C12

DIFFIO_RX_T5N

F14

DIFFIO_TX_T6N

B11

DIFFIO_RX_T7P

D11

DIFFIO_TX_T8P

A9

DIFFIO_RX_T7N

D10

DIFFIO_TX_T8N

A8

DIFFIO_TX_T10P

C7

DIFFIO_TX_T10N

B7

DIFFIO_RX_T11P

E9

DIFFIO_TX_T12P

C8

DIFFIO_RX_T11N

D9

DIFFIO_TX_T12N

B8

DIFFIO_RX_T13P

H14

DIFFIO_TX_T14P

C10

DIFFIO_RX_T13N

G13

DIFFIO_TX_T14N

C9

DIFFIO_RX_T15P

F13

DIFFIO_TX_T16P

A6

DIFFIO_RX_T15N

E13

DIFFIO_TX_T16N

A5

DIFFIO_RX_T17P

H8

DIFFIO_TX_T18P

A4

DIFFIO_RX_T17N

G8

DIFFIO_TX_T18N

A3

DIFFIO_RX_T19P

E12

DIFFIO_RX_T19N

D12

DIFFIO_RX_T23P

F11

DIFFIO_TX_T24P

E8

DIFFIO_RX_T23N

E11

DIFFIO_TX_T24N

D7

DIFFIO_RX_T25P

J7

DIFFIO_TX_T26P

B2

DIFFIO_RX_T25N

H7

DIFFIO_TX_T26N

B1

DIFFIO_RX_T27P

B6

DIFFIO_TX_T28P

C3

DIFFIO_RX_T27N

B5

DIFFIO_TX_T28N

B3

DIFFIO_RX_T29P

K12

DIFFIO_TX_T30P

D2

DIFFIO_RX_T29N

J12

DIFFIO_TX_T30N

C2

DIFFIO_RX_T31P

G12

DIFFIO_TX_T32P

E4

DIFFIO_RX_T31N

G11

DIFFIO_TX_T32N

D4

DIFFIO_RX_T33P

K7

DIFFIO_TX_T34P

E3

DIFFIO_RX_T33N

K8

DIFFIO_TX_T34N

E2

DIFFIO_RX_T35P

G10

DIFFIO_TX_T36P

E1

DIFFIO_RX_T35N

F10

DIFFIO_TX_T36N

D1

DIFFIO_RX_T37P

J10

DIFFIO_TX_T38P

E7

DIFFIO_RX_T37N

J9

DIFFIO_TX_T38N

E6

DIFFIO_RX_T39P

F9

DIFFIO_TX_T40P

G7

DIFFIO_RX_T39N

F8

DIFFIO_TX_T40N

F6

DIFFIO_TX_T20P

D6

DIFFIO_TX_T20N

C5

DIFFIO_RX_T21P

H13

DIFFIO_RX_T21N

H12

DIFFIO_TX_T22P

D5

DIFFIO_TX_T22N

C4

R295 100

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

3.3V

3.3V

3.3V

3.3V

BOOTSEL0 BOOTSEL2 BOOTSEL1 CLKSEL0

CLKSEL1

WARM_RST

HPS_FLASH_DATA2

HPS_FLASH_DATA1

HPS_FLASH_DATA0

HPS_BOOTSEL2

HPS_LED0

HPS_LED1

HPS_LED2

HPS_LED3

HPS_ENET_TX_DATA0

HPS_ENET_TX_DATA1

HPS_ENET_TX_DATA2

HPS_ENET_TX_DATA3

HPS_ENET_RX_DATA0

HPS_ENET_RX_DATA1

HPS_ENET_RX_DATA2

HPS_ENET_RX_DATA3

HPS_SPIM_SS HPS_BOOTSEL2 HPS_FLASH_NCSO HPS_LCM_SPIM_SS HPS_LCM_D_C

HPS_WARM_RST_n

HPS_RESET_n

HPS_WARM_RST_n

HPS_FLASH_DATA3

GND

VCC3P3

GND

VCC3P3

GND

VCC3P3

GND

VCC3P3

GND

VCC3P3

GND

GND

VCC3P3

GND

VCC3P3

VCC3P3

GND

VCC3P3

VCC3P3

HPS_FLASH_NCSO

17

HPS_USB_DATA0

24

HPS_USB_DATA1

24

HPS_USB_DATA2

24

HPS_USB_DATA3

24

HPS_USB_DATA4

24

HPS_SD_DATA2

23

HPS_USB_DATA5

24

HPS_USB_DATA6

24

HPS_USB_STP

24

HPS_USB_DIR

24

HPS_USB_NXT

24

HPS_SD_DATA0

23

HPS_SD_DATA1

23

HPS_USB_CLKOUT

24

HPS_USB_DATA7

24

HPS_CONV_USB_n

23

HPS_LCM_RST_n

18

HPS_UART_TX

23

HPS_UART_RX

23

HPS_ENET_RESET_n

5,25

HPS_SPIM_CLK

26

HPS_SPIM_MOSI

26

HPS_SPIM_SS

26

HPS_ENET_RX_DATA[3..0]25

HPS_ENET_TX_DATA[3..0]

25

HPS_I2C_SDA

8,26

HPS_I2C_CLK

8,26

HPS_GSENSOR_INT

26

HPS_ENET_GTX_CLK

25

HPS_ENET_TX_EN

25

HPS_ENET_MDC

25

HPS_ENET_MDIO

25

HPS_ENET_RX_CLK

25

HPS_ENET_RX_DV

25

HPS_ENET_INT_n

25

USB3300_MR_n

24

HPS_USB_DATA[7..0]

24

HPS_ENET_RESET_n

5,25

HPS_RESET_UART_n

23

HPS_WARM_RST_n

11,12

HPS_CLOCK1_25

6

HPS_LCM_D_C

18

HPS_SPIM_MISO

26

HPS_TDO

12

HPS_TDI

12

HPS_TMS

12

HPS_TCK

12

USB_RESET_PHY

24

HPS_LTC_GPIO

26

HPS_LCM_SPIM_CLK

18

HPS_LCM_SPIM_MOSI

18

HPS_LCM_SPIM_SS

18

HPS_SD_CMD

23

HPS_SD_DATA3

23

HPS_SD_CLK

23

HPS_LED[3..0]

22

HPS_CLOCK2_25

6

HPS_FLASH_DATA[3..0]

17

HPS_FLASH_DCLK

17

HPS_LCM_BK

18

HPS_RESET_n

11

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK7 D

SoCKit Board

B

532Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK7 D

SoCKit Board

B

532Monday, December 09, 2013

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

BANK7 D

SoCKit Board

B

532Monday, December 09, 2013

R142 0

R330

100K

DNI

R336 10K

R187 1K

R302 100K

R138

0

BANK 7

BANK 7A

BANK 7B

BANK 7C

BANK 7D

5CSXFC6DF31

U25G

HPS_NRST

C27

HPS_NPOR

F23

HPS_TDO

B28

HPS_TMS

A29

HPS_TCK

H22

HPS_TRST

A28

HPS_TDI

B27

HPS_PORSEL

F24

HPS_CLK1

D25

HPS_CLK2

F25

NAND_ALE,RGMII1_TX_CLK,QSPI_SS3,HPS_GPIO14

H19

NAND_CE,RGMII1_TXD0,USB1_D0,HPS_GPIO15

F20

NAND_CLE,RGMII1_TXD1,USB1_D1,HPS_GPIO16

J19

NAND_RE,RGMII1_TXD2,USB1_D2,HPS_GPIO17

F21

NAND_RB,RGMII1_TXD3,USB1_D3,HPS_GPIO18

F19

NAND_DQ0,RGMII1_RXD0,HPS_GPIO19

A21

NAND_DQ1,RGMII1_MDIO,I2C3_SDA,HPS_GPIO20

E21

NAND_DQ2,RGMII1_MDC,I2C3_SCL,HPS_GPIO21

B21

NAND_DQ3,RGMII1_RX_CTL,USB1_D4,HPS_GPIO22

K17

NAND_DQ4,RGMII1_TX_CTL,USB1_D5,HPS_GPIO23

A20

NAND_DQ5,RGMII1_RX_CLK,USB1_D6,HPS_GPIO24

G20

NAND_DQ6,RGMII1_RXD1,USB1_D7,HPS_GPIO25

B20

NAND_DQ7,RGMII1_RXD2,HPS_GPIO26

B18

NAND_WP,RGMII1_RXD3,QSPI_SS2,HPS_GPIO27

D21

NAND_WE,QSPI_SS1,BOOTSEL2,HPS_GPIO28

D20

QSPI_IO0,USB1_CLK,HPS_GPIO29

C20

QSPI_IO1,USB1_STP,HPS_GPIO30

H18

QSPI_IO2,USB1_DIR,HPS_GPIO31

A19

QSPI_IO3,USB1_NXT,HPS_GPIO32

E19

QSPI_SS0,BOOTSEL1,HPS_GPIO33

A18

QSPI_CLK,HPS_GPIO34

D19

QSPI_SS1,HPS_GPIO35

C19

SDMMC_CMD,USB0_D0,HPS_GPIO36

F18

SDMMC_PWREN,USB0_D1,HPS_GPIO37

B17

SDMMC_D0,USB0_D2,HPS_GPIO38

G18

SDMMC_D1,USB0_D3,HPS_GPIO39

C17

SDMMC_D4,USB0_D4,HPS_GPIO40

H17

SDMMC_D5,USB0_D5,HPS_GPIO41

C18

SDMMC_D6,USB0_D6,HPS_GPIO42

G17

SDMMC_D7,USB0_D7,HPS_GPIO43

E18

SDMMC_CLK_IN,USB0_CLK,HPS_GPIO44

E17

SDMMC_CLK,USB0_STP,HPS_GPIO45

A16

SDMMC_D2,USB0_DIR,HPS_GPIO46

D17

SDMMC_D3,USB0_NXT,HPS_GPIO47

B16

RGMII0_TX_CLK,HPS_GPIO0

F16

RGMII0_TXD0,USB1_D0,HPS_GPIO1

E16

RGMII0_TXD1,USB1_D1,HPS_GPIO2

G16

RGMII0_TXD2,USB1_D2,HPS_GPIO3

D16

RGMII0_TXD3,USB1_D3,HPS_GPIO4

D14

RGMII0_RXD0,USB1_D4,HPS_GPIO5

A15

RGMII0_MDIO,USB1_D5,I2C2_SDA,HPS_GPIO6

C14

RGMII0_MDC ,USB1_D6,I2C2_SCL,HPS_GPIO7

D15

RGMII0_RX_CTL,USB1_D7,HPS_GPIO8

M17

RGMII0_TX_CTL,HPS_GPIO9

B15

RGMII0_RX_CLK,USB1_CLK,HPS_GPIO10

N16

RGMII0_RXD1,USB1_STP,HPS_GPIO11

C15

RGMII0_RXD2,USB1_DIR,HPS_GPIO12

E14

RGMII0_RXD3,USB1_NXT,HPS_GPIO13

A14

CAN0_TX,UART0_TX,SPIM1_SS0,HPS_GPIO66

D24

CAN0_RX,UART0_RX,SPIM1_MISO,HPS_GPIO65

E24

I2C0_SCL,UART1_TX,SPIM1_MOSI,HPS_GPIO64

D22

I2C0_SDA,UART1_RX,SPIM1_CLK,HPS_GPIO63

C23

UART0_TX,CAN0_TX,SPIM1_SS1,HPS_GPIO62

G22

UART0_RX,CAN0_RX,SPIM0_SS1,HPS_GPIO61

B22

SPIM0_SS0,CAN1_TX,UART1_RTS,BOOTSEL0,HPS_GPIO60

H20

SPIM0_MISO,CAN1_RX,UART1_CTS,HPS_GPIO59

B23

SPIM0_MOSI,I2C1_SCL,UART0_RTS,HPS_GPIO58

C22

SPIM0_CLK,I2C1_SDA,UART0_CTS,HPS_GPIO57

A23

TRACE_D7,SPIS1_MISO,I2C0_SCL,HPS_GPIO56

E23

TRACE_D6,SPIS1_SS0,I2C0_SDA,HPS_GPIO55

C24

TRACE_D5,SPIS1_MOSI,CAN1_TX,HPS_GPIO54

G21

TRACE_D4,SPIS1_CLK,CAN1_RX,HPS_GPIO53

A24

TRACE_D3,SPIS0_SS0,I2C1_SCL,HPS_GPIO52

H23

TRACE_D2,SPIS0_MISO,I2C1_SDA,HPS_GPIO51

A25

TRACE_D1,SPIS0_MOSI,UART0_TX,HPS_GPIO50

C25

TRACE_D0,SPIS0_CLK,UART0_RX,HPS_GPIO49

B25

TRACE_CLK,HPS_GPIO48

B26

R337 10K J15

CLKSEL0

1

2

3

R136

0

R301 0

DNI

J18

BOOTSEL2

1

2

3

R139 1K

C445 0.1u

KEY5

HPS_RESET_n

4 3

21

TP5

DNI

R137 0

R341 0

U29

ADM811

GND

1

RST_n

2

MR_n

3

VCC

4

J16

CLKSEL1

1

2

3

R333 10K

R140 1K

R331

100K

DNI

R345 1K

R300 100K

R340 0DNI

TP3

DNI

R334 10K

J17

BOOTSEL0

1

2

3

R133 1K

R332 0DNI

KEY6

4 3

21

J19

BOOTSEL1

1

2

3

R299 4.7K

R335 10K

C444 0.1u

R298 4.7K

U30

ADM811

GND

1

RST_n

2

MR_n

3

VCC

4

剩余31页未读,继续阅读

xinranfeifan

- 粉丝: 1

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2