EDA课设解析:AHDL与max+plus2学习笔记

需积分: 10 53 浏览量

更新于2024-09-12

收藏 203KB DOCX 举报

"这篇资源是关于EDA课程设计的总结,主要涵盖了AHDL语言和max+plus2工具的使用。作者分享了学习笔记,包括程序段定义、逻辑操作、总线操作以及高级总线概念,还涉及到了数码管段定义和IF-THEN-ELSE结构的应用。"

在EDA(电子设计自动化)领域,AHDL是一种硬件描述语言,用于描述数字系统的逻辑功能。在这个课设摘要中,作者展示了如何使用AHDL来定义程序段。例如,SUBDESIGNdecode1是一个子设计模块,它有4位输入a[3..0]和1位输出chip_enable。在AHDL中,可以使用等于操作符来设置条件,如`chip_enable=(a[3..0]==H"7")`,这表示当输入a的值等于十六进制数7时,输出chip_enable为高电平。

max+plus2是一款由 Synopsis 公司开发的综合工具,用于将AHDL或其他硬件描述语言编写的代码转换为可编程逻辑器件(如FPGA或CPLD)的配置数据。在描述中,作者使用了max+plus2进行逻辑操作,如逻辑或运算(`#`符号表示逻辑或),以及常数函数定义(`CONSTANTIO_ADDRESS=H"A"`)。

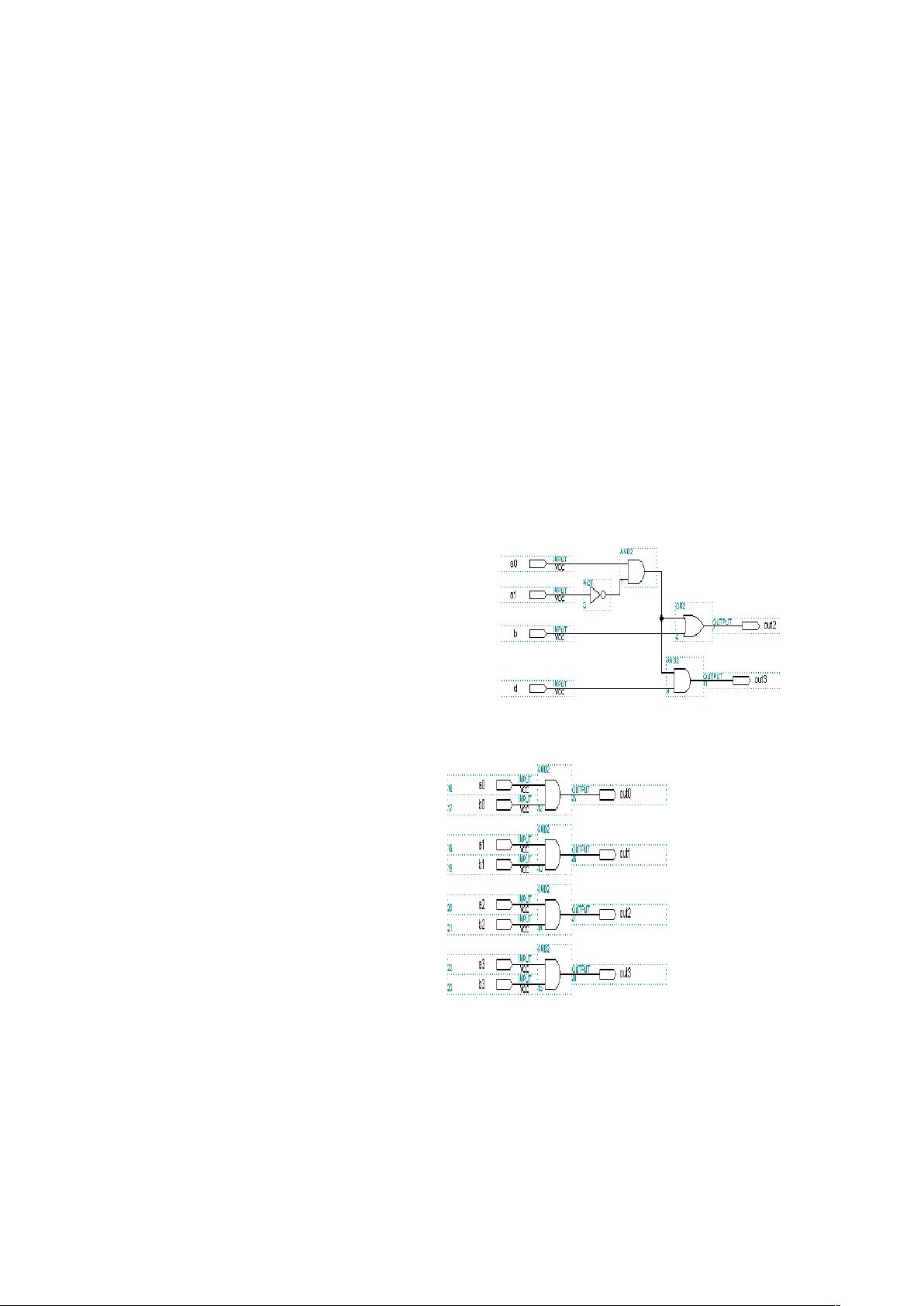

在总线操作部分,作者展示了如何使用AHDL处理总线数据。例如,`out0=a0&b0;`表示out0的值是a0和b0的逻辑与。此外,他还讨论了如何通过索引来访问和赋值总线的特定部分,如`a[9..8]=1;`。这种操作允许对总线上的任意位进行独立控制。

高级总线部分提到了两种特殊类型的总线:Bus和ARRAYBUS。Bus是一个简单的线性结构,如b[3..0],而ARRAYBUS则是多维的,如a[3..0][2..0],它可以被看作是一组排列的子总线。在ARRAYBUS中,可以方便地对每个子总线进行独立操作。

最后,摘要还提及了IF-THEN-ELSE结构在AHDL中的应用,这是逻辑控制的关键部分,允许根据条件执行不同的操作。然而,这部分在摘要中没有详细展开。

这篇资源是学习AHDL语言和max+plus2工具的一个很好的起点,特别是对于那些正在做EDA课程设计的学生或者需要理解数字系统逻辑描述的人。通过理解和实践这些基本概念,可以进一步深入到更复杂的硬件设计中。

497 浏览量

189 浏览量

108 浏览量

198 浏览量

3450 浏览量

2013-05-03 上传

2428 浏览量

点击了解资源详情

119 浏览量

AAQHIT

- 粉丝: 0

- 资源: 6