数字逻辑课程设计(数字钟 三人表决器 “101”序列检测器)

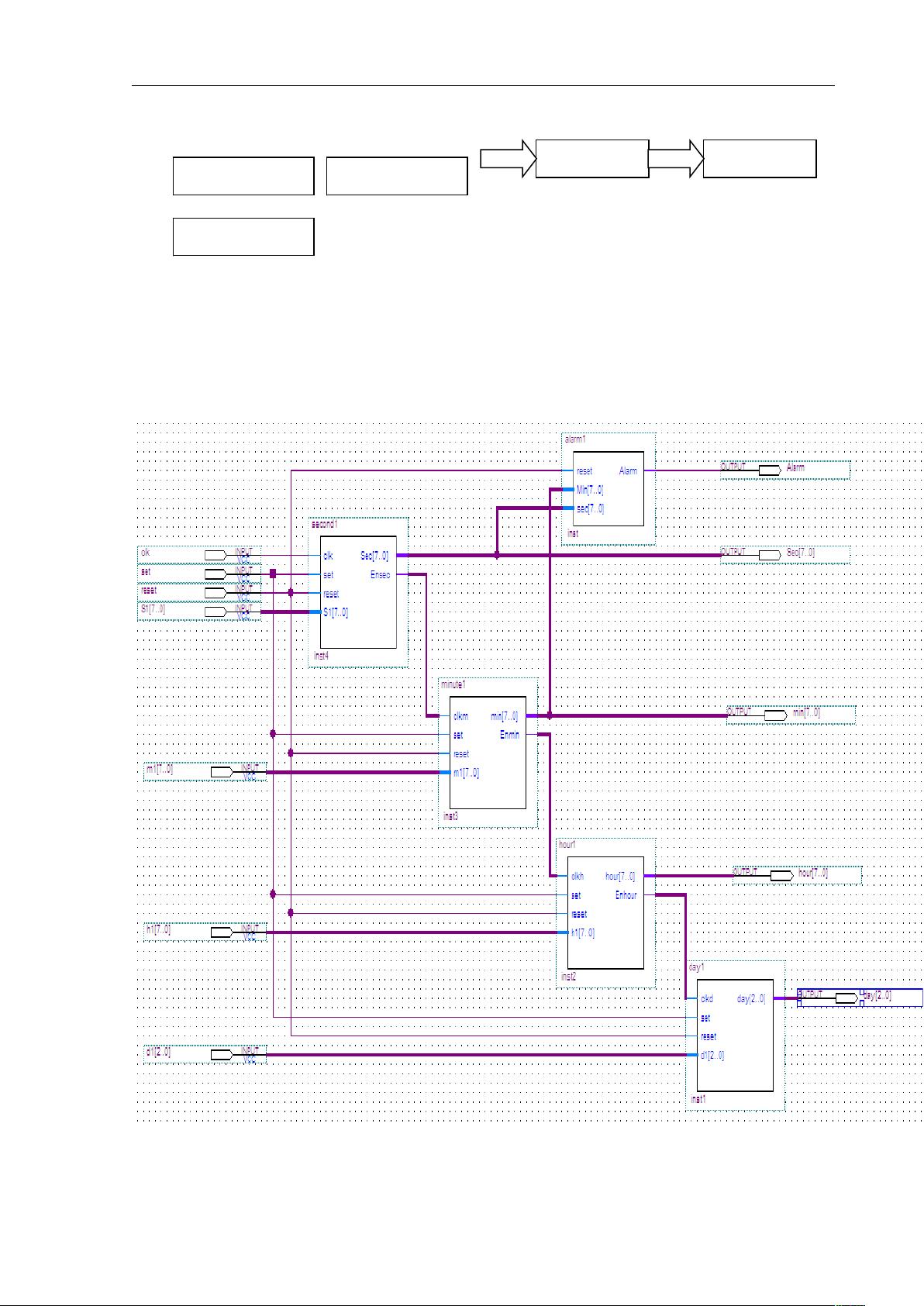

本人设计一个数字时钟,主要用来实现00~59的秒、分六十进制计数器, 00~23的小时二十四进制计数器,整点报时,置数,清零以及数码管显示等功能。

本人设计一个运算单元,主要用来实现三人多数表决,当三个人中通过的人数比不通过的人数多时,则通过,反之,你不通过。

本人设计一个状态机,主要用来检测所输入的序列中是否有“101”序列,设置不同的状态,输入不同的信号,从而得出次态和输出。

2020-04-09 上传

2022-06-13 上传

2022-06-13 上传

2013-10-18 上传

2022-11-21 上传

点击了解资源详情

petters

- 粉丝: 0

- 资源: 13

最新资源

- 俄罗斯RTSD数据集实现交通标志实时检测

- 易语言开发的文件批量改名工具使用Ex_Dui美化界面

- 爱心援助动态网页教程:前端开发实战指南

- 复旦微电子数字电路课件4章同步时序电路详解

- Dylan Manley的编程投资组合登录页面设计介绍

- Python实现H3K4me3与H3K27ac表观遗传标记域长度分析

- 易语言开源播放器项目:简易界面与强大的音频支持

- 介绍rxtx2.2全系统环境下的Java版本使用

- ZStack-CC2530 半开源协议栈使用与安装指南

- 易语言实现的八斗平台与淘宝评论采集软件开发

- Christiano响应式网站项目设计与技术特点

- QT图形框架中QGraphicRectItem的插入与缩放技术

- 组合逻辑电路深入解析与习题教程

- Vue+ECharts实现中国地图3D展示与交互功能

- MiSTer_MAME_SCRIPTS:自动下载MAME与HBMAME脚本指南

- 前端技术精髓:构建响应式盆栽展示网站