Cadence芯片版图设计工具实战指南

"Cadence芯片版图设计工具入门手册提供了对Virtuoso、Diva和Dracula的详细使用指南,适用于初学者。手册涵盖了从工具的准备工作、环境配置到实际设计步骤,包括电路图与版图编辑、DRC检查、LVS验证以及PAD相关的操作流程。"

Cadence是全球领先的电子设计自动化(EDA)软件供应商,其提供的Virtuoso、Diva和Dracula是芯片版图设计的关键工具。Virtuoso是一款先进的集成电路(IC)设计平台,它支持多层混合信号设计,提供了一流的模拟、数字及混合信号设计环境。Diva(Device Interactive Visualizer)则是一个用于版图视图和分析的工具,而Dracula主要用于版图的LVS(Layout vs. Schematic)检查。

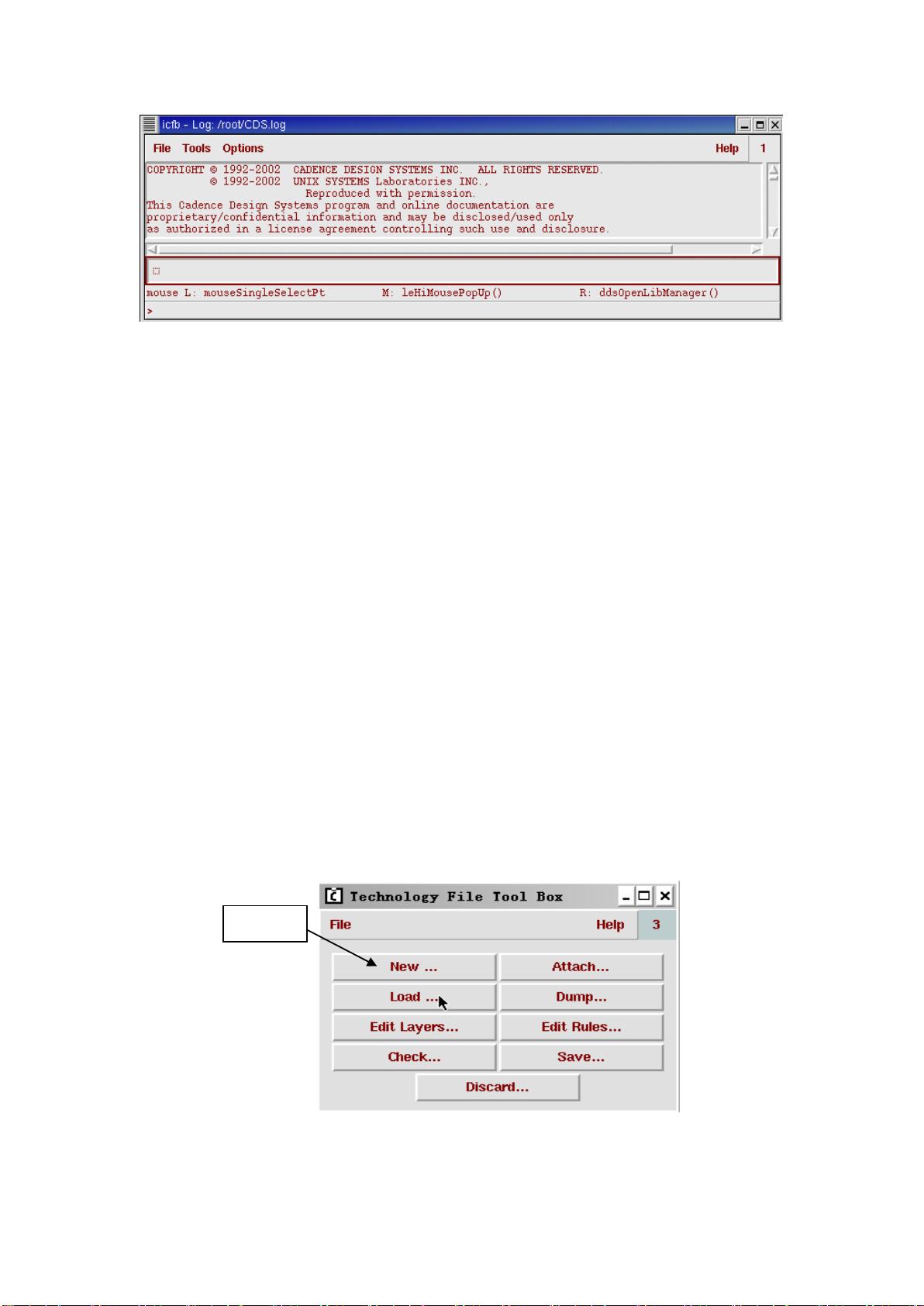

在使用Virtuoso、Diva和Dracula之前,需要确保有一台装有这些工具的计算机并能够连接到它。接下来,需要进行软件环境配置,这包括创建启动目录、复制必要配置文件如.cdsinit和.cdsenv,设置工艺库路径,并安装必要的工艺库和PCELL(参数化单元)。

设计过程始于创建一个新的设计库,然后附加库并创建新设计。电路图的编辑允许用户构建电路模型,而版图编辑则涉及布局规划和布线。版图层次显示特性的调整能帮助优化视觉效果。编辑完成后,务必保存并退出以防止丢失工作。

DRC(Design Rule Check)是设计流程中的重要步骤,通过Diva或Dracula可以进行检查,确保版图符合制造规则。DRC基于Diva的方式主要是在图形界面中直观检查,而基于Dracula的方式则是通过命令行进行更深入的规则验证。

LVS验证是确认版图与电路图的一致性。首先,需要准备版图的GDS文件和电路网表。然后,使用LOGLVS将电路网表转换为LVS所需的格式。接着,根据LVS命令文件进行微调,生成LVS任务的可执行文件,并在控制台运行以检查错误。如有错误,需要进行相应的修改。

最后,PAD相关部分介绍了如何处理输入/输出端口的设计。这包括准备PAD库,导入PAD版图的GDS文件,更新GDS和CDL(Chip Description Language)文件,以便于实现与外部电路的互连。

Cadence芯片版图设计工具入门手册为学习者提供了一个全面的学习路径,从基础的工具配置到复杂的设计和验证步骤,逐步引导初学者掌握这一专业领域的核心技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-05-07 上传

2013-09-16 上传

2008-10-08 上传

2021-09-30 上传

2009-04-20 上传

520 浏览量

hanliuic

- 粉丝: 1

- 资源: 1

最新资源

- jmeter中文使用手册.pdf

- 几种函数调用方式 asm ,disassemble

- 计算机科学与技术专业毕业设计

- A Beginner’s Introduction to Computer program

- 基于PCA和ICA的人脸识别

- Ubuntu部落教程,让你轻松入门ubuntu

- 555定时器的频率发生以及计算

- ccna cisco测试题答案

- ccen cisco测试题答案

- 基于无线传感器网络的机房温度监控系统

- asp。net做的海图对比

- 自适应滤波器 英文资料

- Win2K&WinXP网络显示配置常用命令

- 网络组建基础必备之网线制作

- 项目开发计划书(DOC格式)

- 无线传感器网络的自身定位算法研究