93AA56A/B/C, 93LC56A/B/C, 93C56A/B/C

DS21794E-page 6 © 2007 Microchip Technology Inc.

2.0 FUNCTIONAL DESCRIPTION

When the ORG pin (93XX56C) pin is connected to

V

CC, the (x16) organization is selected. When it is

connected to ground, the (x8) organization is selected.

Instructions, addresses and write data are clocked into

the DI pin on the rising edge of the clock (CLK). The DO

pin is normally held in a High-Z state except when read-

ing data from the device, or when checking the Ready/

Busy

status during a programming operation. The

Ready/Busy

status can be verified during an Erase/

Write operation by polling the DO pin; DO low indicates

that programming is still in progress, while DO high

indicates the device is ready. DO will enter the High-Z

state on the falling edge of CS.

2.1 START Condition

The Start bit is detected by the device if CS and DI are

both high with respect to the positive edge of CLK for

the first time.

Before a Start condition is detected, CS, CLK and DI

may change in any combination (except to that of a

Start condition), without resulting in any device

operation (Read, Write, Erase, EWEN, EWDS, ERAL

or WRAL). As soon as CS is high, the device is no

longer in Standby mode.

An instruction following a Start condition will only be

executed if the required opcode, address and data bits

for any particular instruction are clocked in.

2.2 Data In/Data Out (DI/DO)

It is possible to connect the Data In and Data Out pins

together. However, with this configuration it is possible

for a “bus conflict” to occur during the “dummy zero”

that precedes the read operation, if A0 is a logic high

level. Under such a condition the voltage level seen at

Data Out is undefined and will depend upon the relative

impedances of Data Out and the signal source driving

A0. The higher the current sourcing capability of A0,

the higher the voltage at the Data Out pin. In order to

limit this current, a resistor should be connected

between DI and DO.

2.3 Data Protection

All modes of operation are inhibited when VCC is below

a typical voltage of 1.5V for ‘93AA’ and ‘93LC’ devices

or 3.8V for ‘93C’ devices.

The EWEN and EWDS commands give additional

protection against accidentally programming during

normal operation.

After power-up, the device is automatically in the

EWDS mode. Therefore, an EWEN instruction must be

performed before the initial ERASE or WRITE instruction

can be executed.

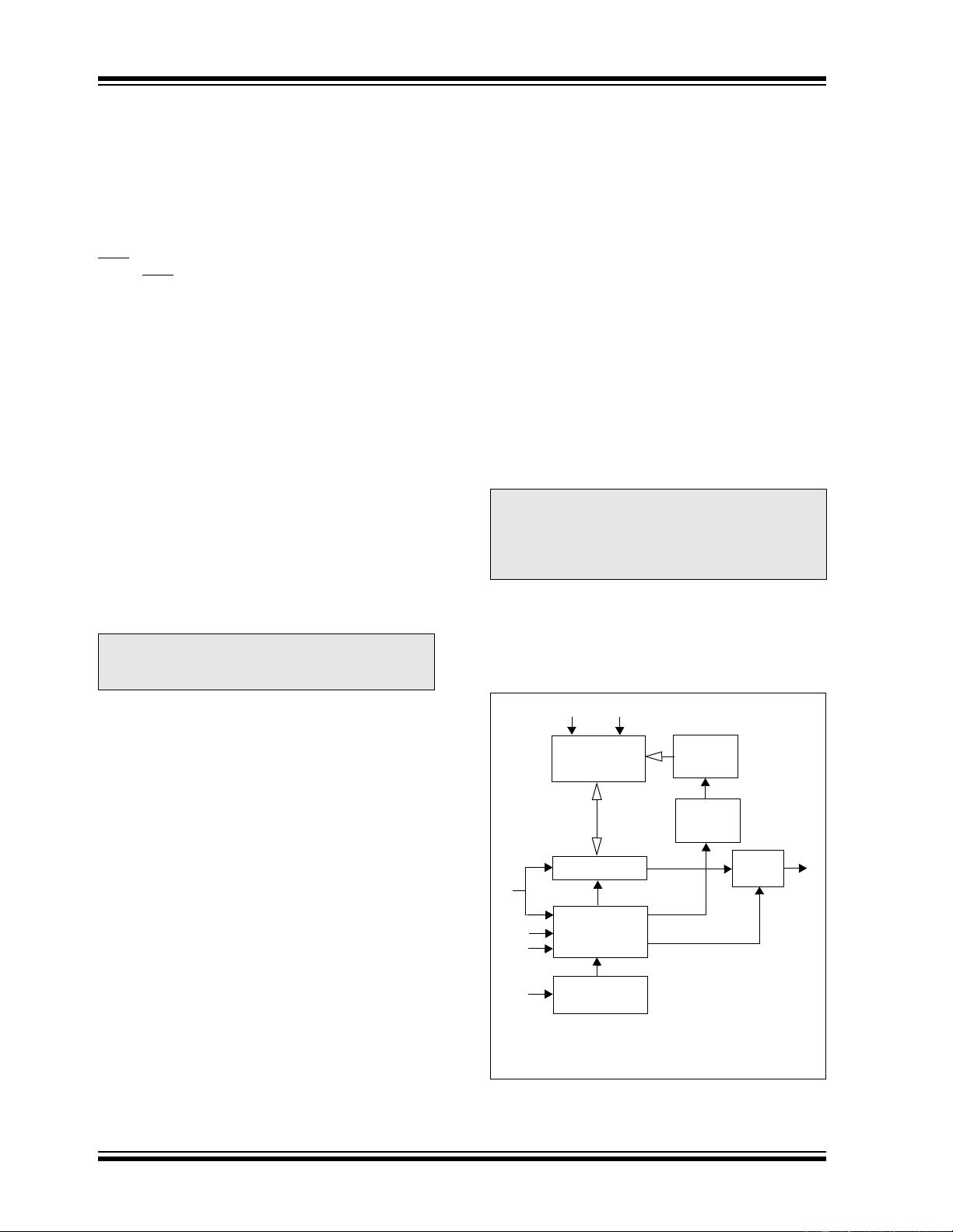

Block Diagram

Note: When preparing to transmit an instruction,

either the CLK or DI signal levels must be

at a logic low as CS is toggled active high.

Note: For added protection, an EWDS command

should be performed after every write

operation and an external 10 kΩ pull-down

protection resistor should be added to the

CS pin.

Memory

Array

Data Register

Mode

Decode

Logic

Clock

Register

Address

Decoder

Address

Counter

Output

Buffer

DO

DI

ORG*

CS

CLK

V

CC VSS

*ORG input is not available on A/B devices