8-3编码器与3-8译码器的Verilog实现及其改进

64 浏览量

更新于2024-08-03

收藏 288KB DOCX 举报

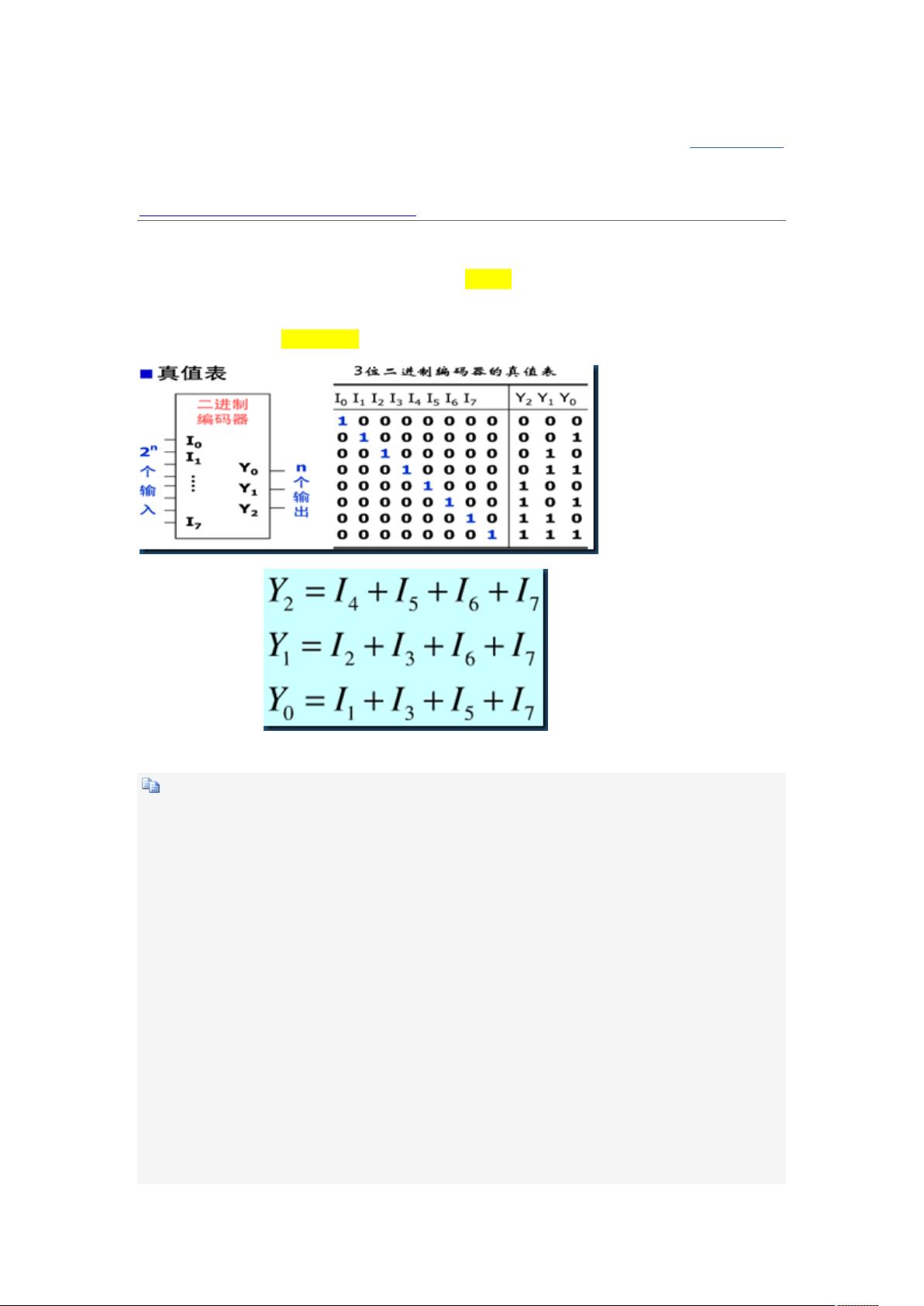

在Verilog语言中,8-3编码器是一种基础的逻辑设计,用于将8位的输入信号转换为3位的输出代码,以便于进行编码操作。在数字系统设计中,编码器扮演着至关重要的角色,它通过将输入的二进制信号组合成特定的输出代码,便于后续的处理和通信。

首先,我们来看一个简单的8-3编码器的实现。在这个例子中,模块`mb_83`接收8位输入`x[7:0]`,并根据输入的不同组合输出对应的3位原码编码。使用`always @(x)`语句,设计者Sasha Xu定义了一个条件语句`case(x)`,其中列举了所有可能的8位输入`x`对应到3位输出`y`的映射关系。这种映射是硬编码的,每个输入值与特定的输出码成一一对应关系。

然而,这个基础的8-3编码器存在一个局限性,即它不支持并行输入,这意味着在同一时刻只能有一个输入信号有效,否则会导致输出混乱。为了克服这一问题,引入了优先编码器。优先编码器允许同时有多路输入,但会根据预先设定的优先级来决定哪个输入应该被编码。例如,如果输入信号i[7:0]和输入使能端ei以及优先级控制信号eo一起工作,优先编码器会选择优先级最高的信号进行编码,从而避免了并发输入时的冲突。

优先编码器的真值表展示了不同输入信号组合下的优先级关系,这对于理解和设计编码器的优先级机制非常重要。在Verilog实现上,除了基本的映射逻辑外,可能还需要额外的控制逻辑来处理优先级,这通常涉及到条件判断、计数器或者其他控制电路的设计。

在实际的Verilog代码中,优先编码器可能包含这样的结构:

```verilog

module pe_83(input [7:0] i, input ei, input [1:0] eo, output reg [2:0] y);

//...(优先级控制逻辑、状态机、映射逻辑等)

endmodule

```

在这里,`ei`作为输入使能,`eo`表示不同的优先级级别,而内部的复杂逻辑将根据这些信号调整编码过程。优先级编码器的实现会更复杂,但能提供更高的灵活性和可靠性,尤其在需要处理多个并行输入的场景下。

总结来说,8-3编码器和优先编码器是数字逻辑设计中的基础组件,它们在Verilog中通过条件语句和控制逻辑来实现不同的功能。理解这些概念有助于深入学习和设计高级的数字电路系统。

2022-06-16 上传

2022-10-13 上传

2021-02-27 上传

2022-11-10 上传

2022-06-20 上传

2022-06-20 上传

2022-06-20 上传

2022-06-12 上传

2022-11-07 上传

xiaoshun007~

- 粉丝: 4102

- 资源: 3118

最新资源

- 温特线性matlab代码-matlab_NS_solvers:旧的研究代码。主要是涡量公式中的2DNS求解器

- 行业文档-设计装置-一种切纸机的双位刀头.zip

- Lora-32-Connect-by-Wifi

- 视图:场景模块的界面,为发送到渲染器的显示对象提供用户交互输入输出和剔除管理

- omniauth-rails_csrf_protection:在Rails应用程序的OmniAuth请求端点上提供CSRF保护

- ryanatkn

- 基于神经网络的人脸识别.zip

- derrobott.github.io:没事了

- matlab导弹落点代码-missile_simulation_matlab:导弹仿真Matlab代码

- iains:TestAccount

- xlog:xlog是netcontext感知HTTP应用程序的记录器

- 自动驾驶汽车案例研究

- 「基于图像识别的收银台」客户端软件,基于OpenCV + Qt,需要搭配「基于图像识别的收银台」后端服务使用。.zip

- darwish-rainmeter

- CSCI3800_Sp15_Team8:CSCI3800 Spring 2015 Team 8项目

- blog