高速电路板设计:RapidIO交换的信号完整性挑战

195 浏览量

更新于2024-08-28

收藏 255KB PDF 举报

"本文深入探讨了在高速电路板设计中如何处理信号完整性问题,特别是通过串行RapidIO交换技术来解决这一挑战。随着无线通信、网络基础设施和航空电子设备的数据速率不断提高,信号完整性的管理变得至关重要。串行RapidIO作为一种高效的串行链接方式,被广泛用于处理器、FPGA和数字信号处理器之间的数据传输,以及系统内部的交换卡互联,以满足高带宽需求。

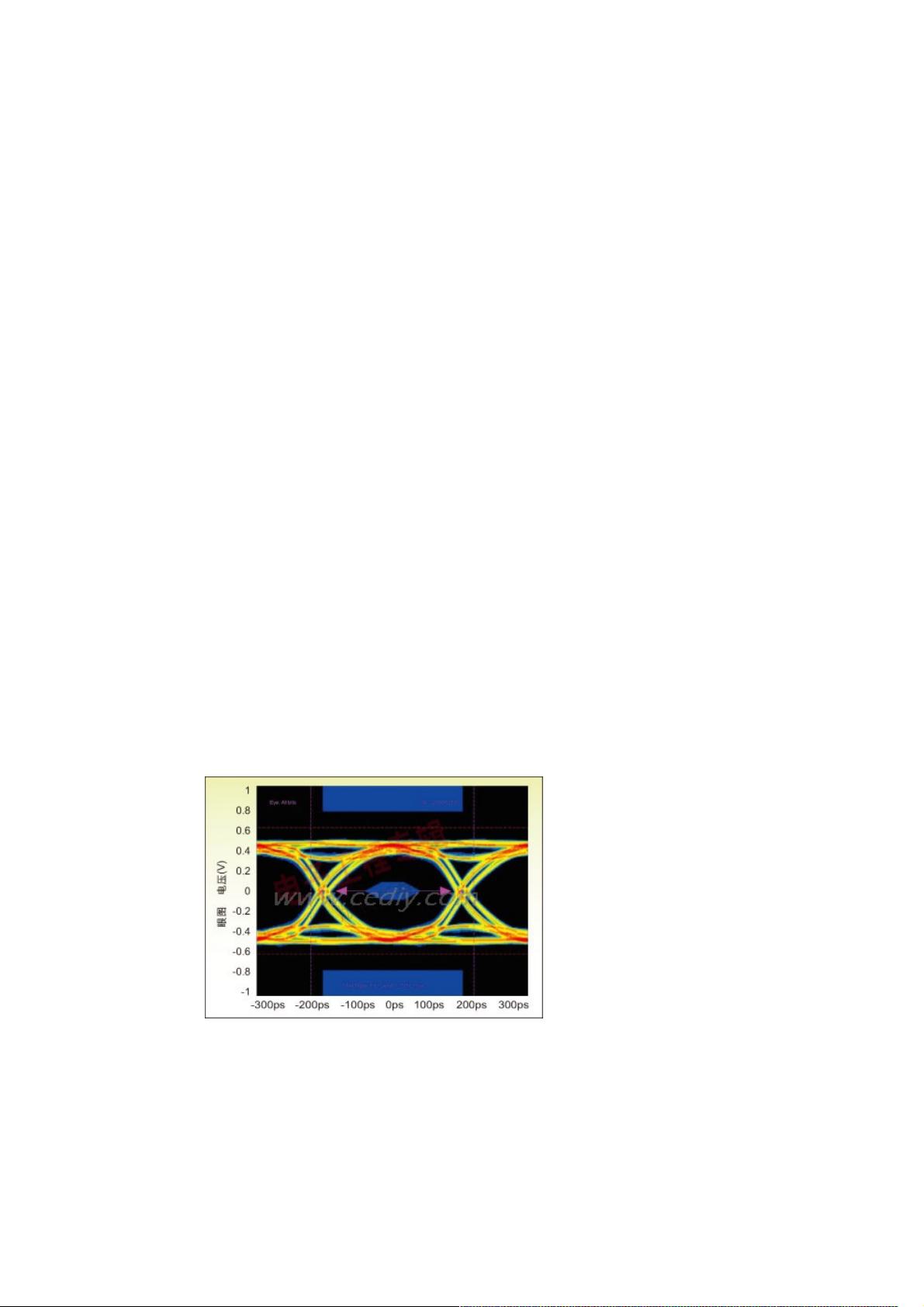

在高速接口设计中,信号完整性面临的首要问题是接收眼图的质量。接收眼图的大小直接影响着信号质量,一个开放的眼图意味着更好的信号品质。信号质量可能会受到各种因素的影响,包括噪声、布线问题、外部干扰以及系统自身的噪声源。因此,设计者需要在整个系统层面考虑信号源和接收端的特性,确保信号完整性。

在电路板设计阶段,有多个关键因素需要考虑。电源输入、局部调节器、时钟生成和分配、退耦电路、PCB材料选择、芯片间连接、背板连接、电路板层叠和阻抗控制,以及机架间的连接器和电缆选择都是决定信号完整性的关键因素。在高频设计中,常规的低频设计方法不再适用,需要考虑到波长与电路板尺寸的关系,以及材料的介电常数和损耗因子。

例如,FR4材料在较低频率下是常用的基材,但在高频环境下,过孔设计和阻抗匹配变得尤为重要。未使用的过孔部分可能会导致阻抗不匹配,影响信号质量。此外,良好的退耦策略可以减少电源噪声,保持信号的稳定性。

解决这些问题需要采用仿真工具进行信号完整性分析,预测和解决问题。设计者还应利用高级布线策略,如差分对和屏蔽技术,来降低串扰并增强信号完整性。同时,优化电源和地平面布局,以及选择具有适当电气特性的连接器和电缆,也是确保信号质量的关键。

在实际应用中,开发板和电子技术,特别是基于ARM的开发板,经常使用串行RapidIO交换来实现高速数据传输。设计者需要掌握这些技术,以便在面对日益复杂的电路板设计挑战时,能够有效地管理和改善信号完整性,从而保证系统的稳定性和性能。

高速电路板设计中的信号完整性是当前数字硬件设计的重要议题。通过理解和应用串行RapidIO交换技术,结合对电路板设计细节的深入理解,设计者可以应对不断增加的数据速率要求,实现高性能、低延迟的系统互连。"

2020-07-28 上传

2020-01-29 上传

2014-09-22 上传

2021-07-13 上传

2016-03-16 上传

2021-01-20 上传

2021-07-26 上传

点击了解资源详情

2024-11-10 上传

weixin_38691703

- 粉丝: 2

- 资源: 961

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码