0.13μm CMOS工艺的低电压带隙基准电压源设计

47 浏览量

更新于2024-08-31

1

收藏 205KB PDF 举报

"电源技术中的一种低电压带隙基准电压源的设计"

电源技术在现代电子设备中扮演着至关重要的角色,特别是在数模混合电路的设计中,基准电压是不可或缺的一部分。带隙基准电压源作为产生恒定基准电压的常用方法,其设计随着技术的发展不断演进。随着CMOS工艺的不断进步,数字电路的功耗和占用面积得到了显著降低,电源电压也随之下降,这对模拟电路的设计提出了新的挑战。

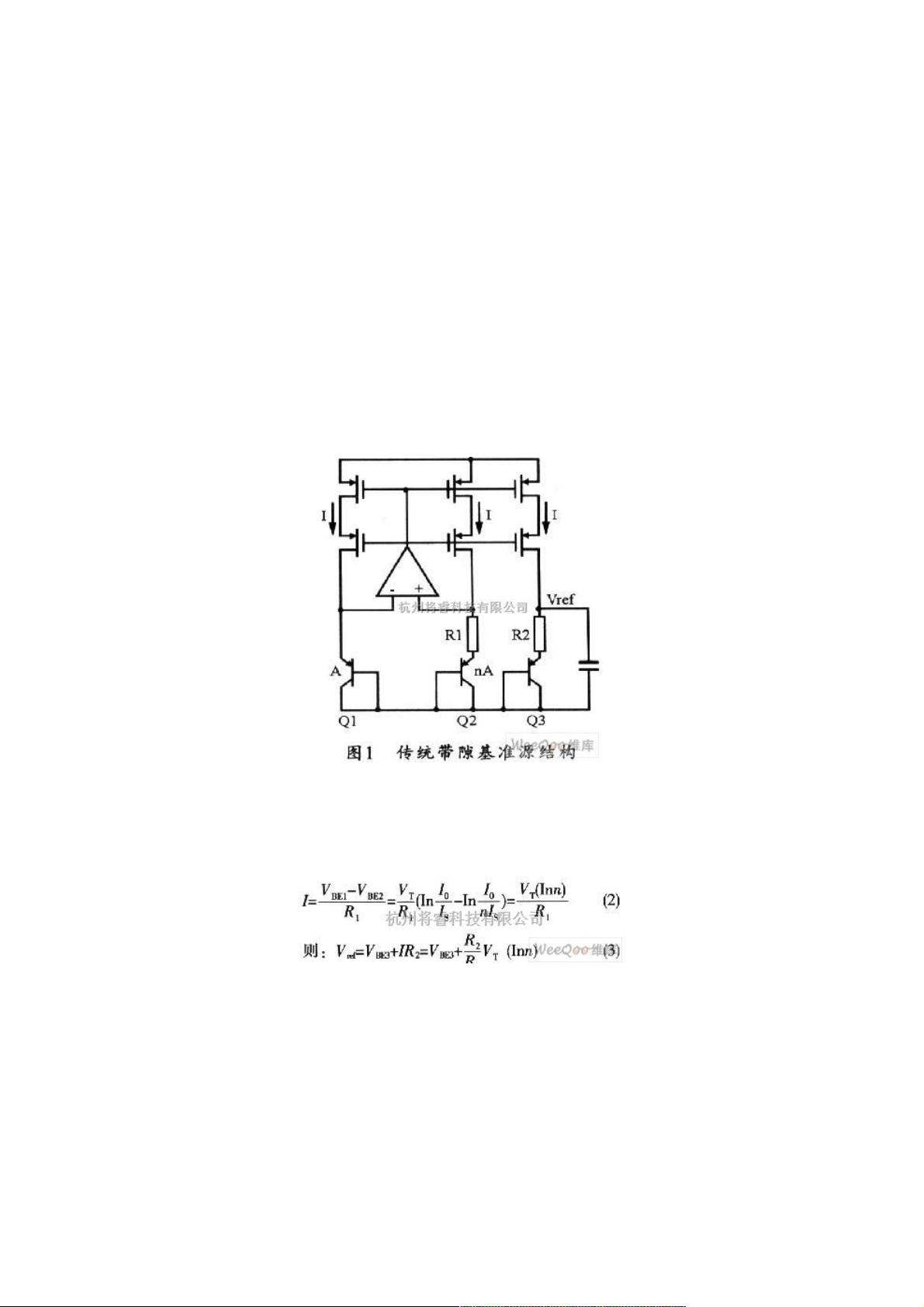

传统的带隙基准电压源通常利用双极型晶体管的基极-发射极电压(VBE)和热电压(VT)的温度特性来实现零温度系数的电压输出。这种设计中,双极型晶体管Q2的面积是Q1的n倍,通过运算放大器的高增益保持输入端电平平衡,调整电阻比例以抵消VBE的负温度系数和VT的正温度系数。然而,在0.13微米的CMOS工艺中,由于低电压MOS管的工作电压降至约1.2V,传统方案无法满足低电源电压的需求。

为应对这一挑战,新型的低电压带隙基准电压源应运而生。虽然其基本工作原理仍然基于抵消正负温度系数,但设计上进行了优化以适应低电源电压环境。低电压带隙基准电压源的核心部分会采用更适宜低电压操作的器件和电路结构,例如使用MOSFET代替双极型晶体管,并且可能引入新的温度补偿机制,以确保在低电压环境下也能提供稳定且无温度漂移的基准电压。

在设计过程中,除了核心电路外,还包括运算放大器的设计,它需要有足够高的增益以维持输入端电压平衡,并且在低电源电压下仍能正常工作。此外,偏置电路和启动电路也是必不可少的组成部分,它们确保基准电压源能够正确启动并保持稳定的工作状态。在TSMC 0.13微米CMOS工艺条件下,这些电路都需要经过精心设计和优化,以确保在实际应用中的性能和可靠性。

为了验证设计的有效性,通常会使用电路仿真工具进行仿真分析。Cadence Spectre是一款广泛使用的电路仿真软件,它可以模拟电路在各种条件下的行为,帮助设计师在实际制造之前发现潜在问题并进行调整。通过这样的仿真验证,设计者可以确保低电压带隙基准电压源在实际应用中能够满足预期的低功耗和高精度要求。

低电压带隙基准电压源设计是电源技术领域的一个重要研究方向,它旨在解决随着工艺尺寸减小和电源电压下降带来的设计难题。通过创新的电路结构和补偿策略,这种新型设计能够在低电源电压环境中提供稳定的基准电压,满足现代电子设备对低功耗和高性能的需求。

616 浏览量

585 浏览量

136 浏览量

585 浏览量

218 浏览量

2021-09-14 上传

2021-07-26 上传

230 浏览量

weixin_38623009

- 粉丝: 5

- 资源: 906