基于FPGA的HDB3编解码系统设计与实现

本设计说明书详细阐述了一种基于FPGA的HDB3码编解码系统的设计,针对电气与信息工程学院通信工程专业学生易X在2016年6月完成的课程设计项目。设计的核心目标是利用EP2C5T114C8N FPGA实现HDB3码的高效编解码,同时具备单双极性转换功能,以适应FPGA内部处理和便于数字逻辑分析。

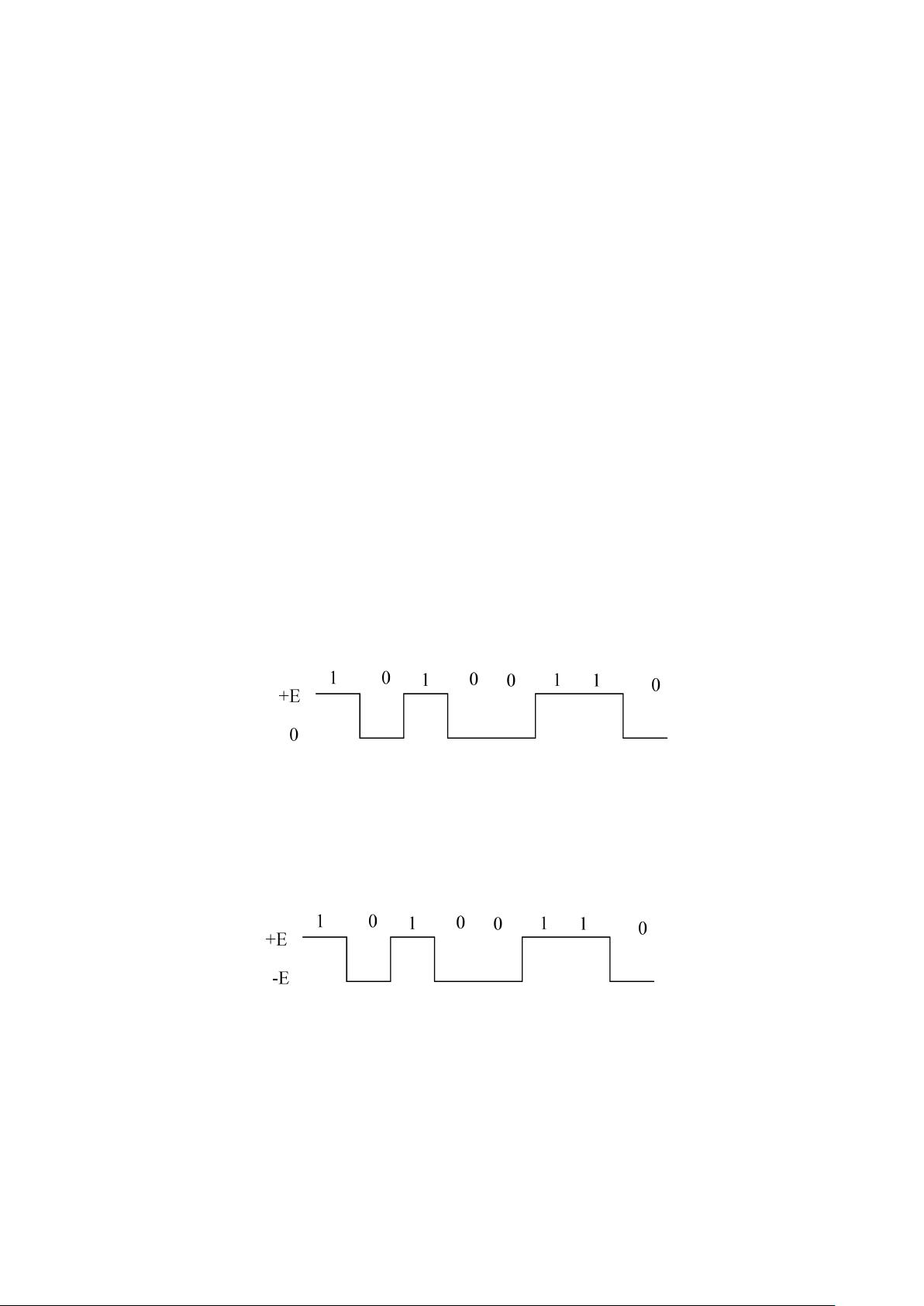

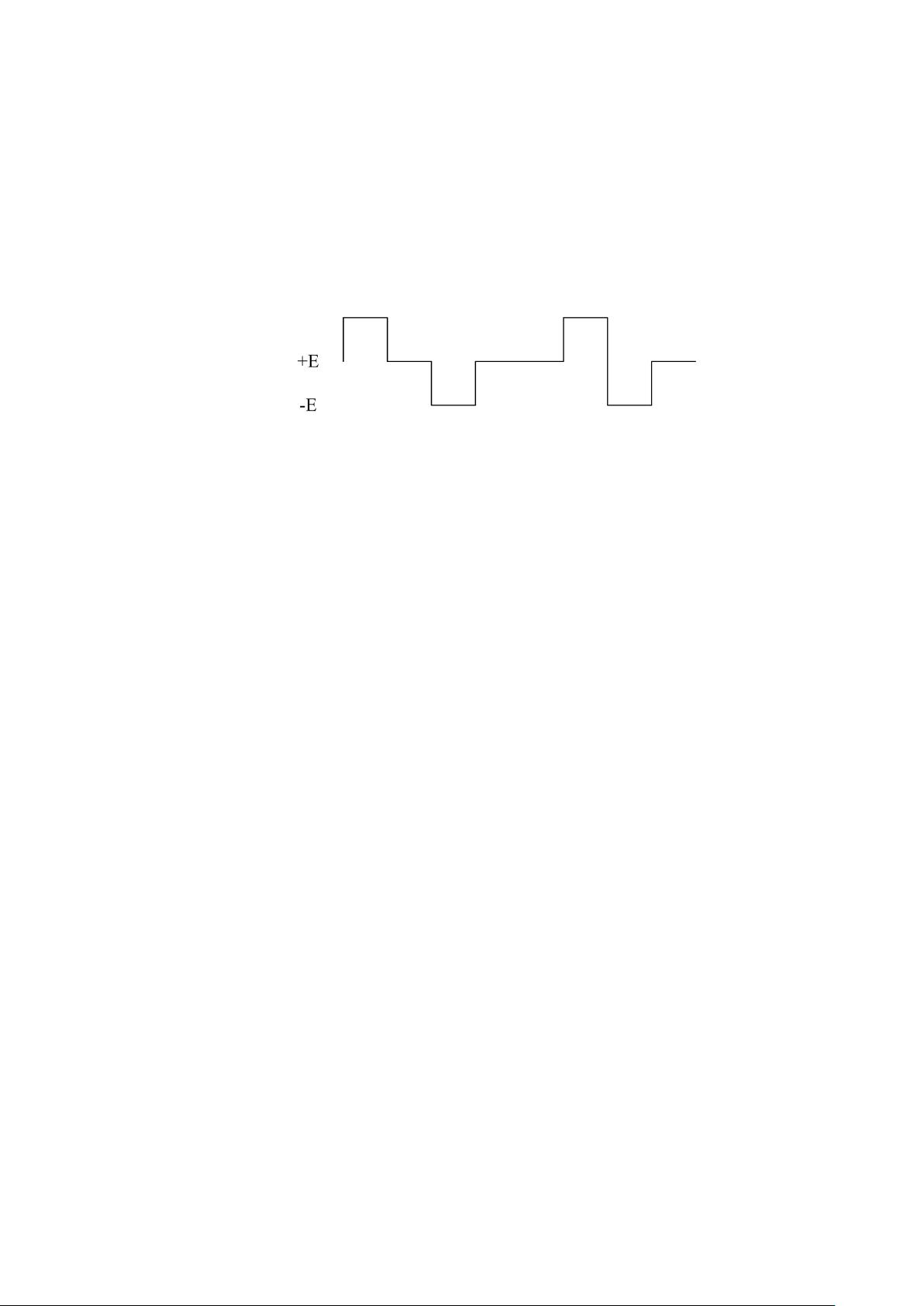

HDB3(归零双极性编码)是一种广泛应用于基带传输的码型,它通过在每个码元前后添加均衡的0电平,增强了信号的抗噪声性能。系统设计主要包括五个关键模块:源码生成模块负责生成原始信号,HDB3编码模块将NRZ(非归零)或AMI(归零不等宽)码转换为HDB3码,编码规则分析了如何执行这个过程;HDB3译码模块则负责逆向操作,将接收到的HDB3码还原为原始信号;键控脉冲发生模块用于同步和控制信号的发送,而分频模块则可能用于调整系统的工作频率。

整个系统设计遵循了清晰的结构和简洁的外围电路,强调了稳定性、抗干扰能力和可调试性。FPGA的独特性质体现在其使用VHDL语言进行编程,允许设计师在硬件层面灵活修改代码,这对于实时调整和优化系统性能至关重要。通过仿真验证,该编解码系统在实际测试中表现出良好的稳定性和可靠性,适用于实际的通信电路应用。

关键词:HDB3码、FPGA、编解码、VHDL语言、系统仿真。设计者通过深入理解HDB3码的工作原理,结合实际硬件平台,成功实现了一个功能齐全且实用的编解码系统,为通信工程领域提供了有价值的参考案例。

385 浏览量

2023-07-27 上传

144 浏览量

2021-07-13 上传

2021-10-02 上传

233 浏览量

重剑无锋ing

- 粉丝: 0

最新资源

- Verilog实现的Xilinx序列检测器设计教程

- 九度智能SEO优化软件新版发布,提升搜索引擎排名

- EssentialPIM Pro v11.0 便携修改版:全面个人信息管理与同步

- C#源代码的恶作剧外表答题器程序教程

- Weblogic集群配置与优化及常见问题解决方案

- Harvard Dataverse数据的Python Flask API教程

- DNS域名批量解析工具v1.31:功能提升与日志更新

- JavaScript前台表单验证技巧与实例解析

- FLAC二次开发实用论文资料汇总

- JavaScript项目开发实践:Front-Projeto-Final-PS-2019.2解析

- 76云保姆:迅雷云点播免费自动升级体验

- Android SQLite数据库增删改查操作详解

- HTML/CSS/JS基础模板:经典篮球学习项目

- 粒子群算法优化GARVER-6直流配网规划

- Windows版jemalloc内存分配器发布

- 实用强大QQ机器人,你值得拥有