TMS320F28335 PLL初始化:倍频器配置详解

需积分: 50 164 浏览量

更新于2024-09-07

收藏 404KB DOCX 举报

"这篇文档主要介绍了TMS320F28335 DSP芯片中PLL倍频器的初始化设置,包括PLL模块的功能、工作模式、以及相关寄存器的使用。"

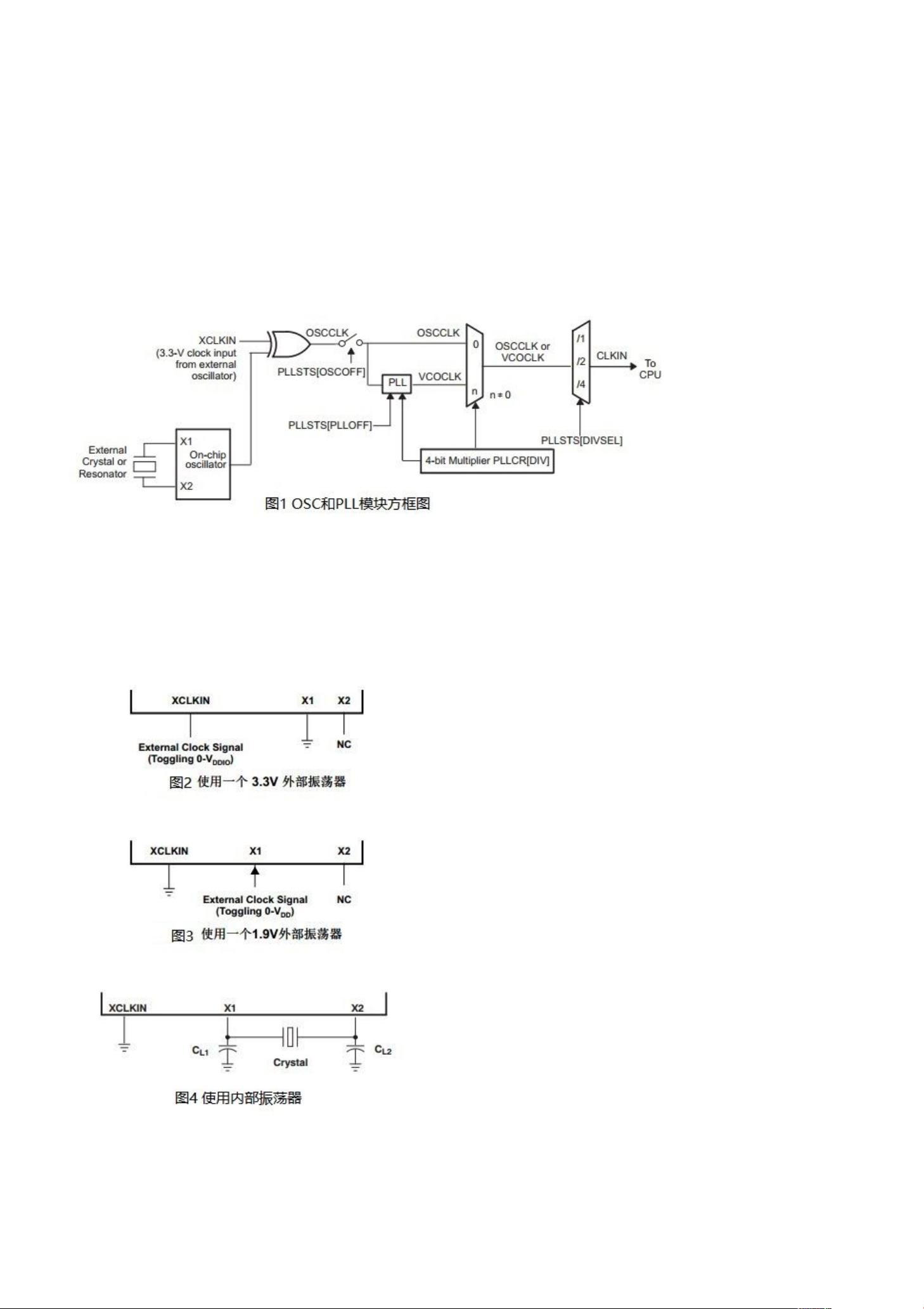

TMS320F28335是一款高性能的数字信号处理器,其时钟系统中的PLL(Phase-Locked Loop,锁相环)倍频器是关键组件,能够对输入时钟进行倍频,从而生成高频率的时钟信号,降低生成高频时钟的成本。PLL模块包含两个重要寄存器:PLL状态寄存器(PLLSTS)和PLL控制寄存器(PLLCR),它们用于监控和配置PLL的工作状态。

1. PLL模块及工作模式

PLL模块具备两种操作模式。第一种是晶振操作模式,利用外部晶振或谐振器提供时钟基础。第二种是外部时钟源操作模式,允许通过X1或XCLKIN引脚输入外部时钟信号,旁路内部振荡器。文档中提到的30MHz外部石英晶振具有特定的技术规格,包括负载电容、并联谐振参数等。

2. 基于PLL的时钟模块

TMS320F28335的时钟模块内置了PLL倍频器,能提供所有系统所需的时钟信号,并且可以控制低功耗模式。当PLL启用时,需要密切关注PLLSTS寄存器中的MCLKSTS位,以确保系统时钟的稳定性。若MCLKSTS位被置位,可能需要采取措施如系统停机或复位。

3. PLL配置寄存器

PLL配置涉及到两个寄存器:PLLSTS和PLLCR。PLLSTS的DIVSEL位域决定了CPU时钟的分频系数,可以选择/4、/2或/1。而PLLCR的DIV位域则定义了CPU时钟的倍频系数,可以设置为1到10的倍频。例如,若要将30MHz的外部晶振频率提升至150MHz,就需要设置PLLCR的DIV为10,同时根据需求选择适当的PLLSTS的DIVSEL值。

初始化PLL倍频器的过程通常涉及以下步骤:

1. 检查PLLSTS寄存器,确认PLL是否已稳定。

2. 设置PLLCR寄存器的DIV位,以选择期望的倍频系数。

3. 设置PLLSTS的DIVSEL位,设定分频系数。

4. 使能PLL,等待PLL稳定后,再切换系统时钟源至PLL输出。

这个过程中,需特别注意PLL的工作条件和稳定性,避免因错误配置导致系统异常。正确的初始化和监控是保证TMS320F28335正常运行的关键。

2020-08-04 上传

2020-08-10 上传

2022-09-23 上传

2022-09-23 上传

2022-09-21 上传

ade3050

- 粉丝: 0

- 资源: 4

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程