基于DSC的SPLL改进:提高ip-iq谐波电流检测精度

121 浏览量

更新于2024-09-01

1

收藏 518KB PDF 举报

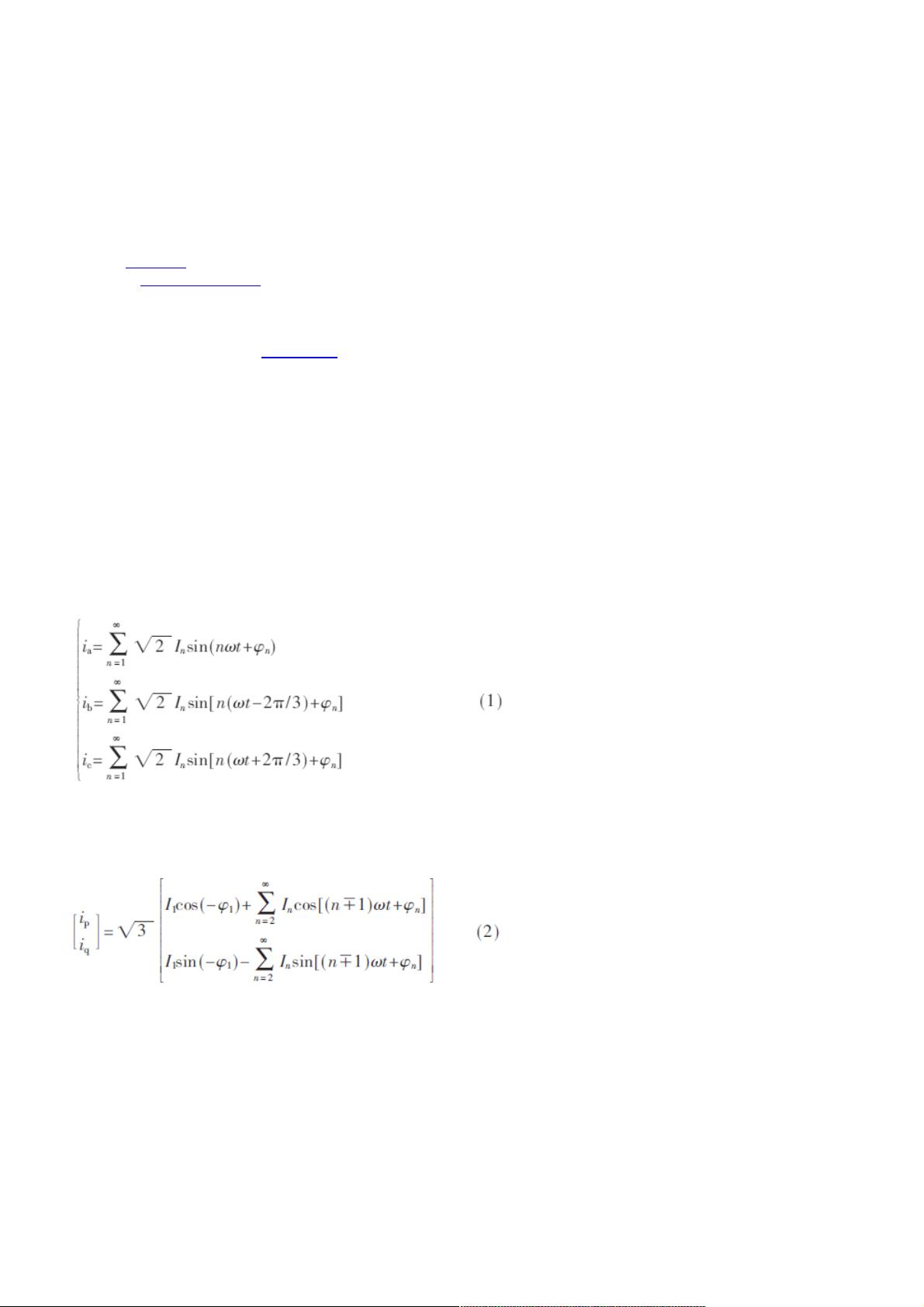

在现代电力系统中,谐波电流检测作为有源电力滤波器的关键组成部分,其准确性直接影响到系统的性能和电能质量。本文主要探讨了基于瞬时无功功率理论的ip-iq算法在谐波电流检测中的应用,特别是针对软件锁相环(Software Phase-Locked Loop, SPLL)的优化研究。

传统的ip-iq算法依赖于锁相环来精确锁定电网电压的频率,这在实时检测谐波电流时至关重要。然而,PLL存在锁相误差、信号畸变和频率波动等问题,这些问题会直接导致谐波检测的不准确。为了解决这些问题,研究者们针对不同类型的软件锁相环进行了深入分析:

1. **基于同步旋转参考坐标系的SPLL**:这种方法结构清晰,能够快速锁定电压角频率,适合检测谐波,但锁相性能对PI控制器参数敏感,对电压畸变和频率波动的抑制能力受到限制。

2. **基于正序基波提取器的SPLL**:尽管具有较好的频率波动抑制效果,但结构复杂,物理意义不明显,锁相速度较慢,锁相性能受增益K值的影响大。

3. **基于正交分解法的SPLL**:虽然结构简单,但检测精度不高,软件实现复杂,且受低通滤波器影响较大。

本文着重介绍了基于延迟信号取消(Delay Signal Cancellation, DSC)模块的三相软件锁相环的改进。DSC模块的作用是通过实时延时处理信号,从而提取信号的正负序分量,这对于提高锁相的稳定性和精度非常关键。通过结合DSC,新型的三相SPLL算法得以简化,运算速度得到提升,能够更准确地锁定相位信息,进而提高谐波检测的准确性和实时性。

在实际应用中,作者首先回顾了基于瞬时无功功率理论的ip-iq算法,它利用三相电路中瞬时有功电流ip和瞬时无功电流iq的计算,有效地检测出谐波分量,即使在不对称电网和电压波形畸变的情况下也能保持良好的性能。然后,通过仿真和实验验证,证明了基于DSC模块的SPLL改进方案在抑制电压畸变和频率波动方面具有明显优势,从而为有源电力滤波器提供了更为精确和可靠的谐波电流检测手段。

总结来说,这篇文章深入研究了ip-iq算法在谐波检测中的SPLL技术,并通过引入DSC模块实现了SPLL性能的提升,为电力系统的谐波管理提供了一种有效的解决方案。

2022-07-13 上传

2022-07-14 上传

2022-07-13 上传

2024-07-23 上传

2020-10-19 上传

2022-09-20 上传

2021-04-29 上传

weixin_38559569

- 粉丝: 3

- 资源: 948

最新资源

- MANITOR-Raspberry:Manitor Para La树莓

- react-text-transition:动画文字更改

- 季节

- embafu:这是embafu short let上市网站的应用程序

- bg-helper-cubalibre:自由古巴的人工智能伴侣

- 基于微信小程序的疫苗预约接种系统.zip

- flax:Flax是JAX的神经网络生态系统,旨在提高灵活性

- 谷歌视觉API

- 天池短租新人赛-数据集

- 温特线性matlab代码-Dual-Inverted-Pendulum-MATLAB:为双倒立摆设计控制器和估计器。UCSDWinter15'

- 在Android上将实时摄像头与AI危害检测配合使用

- go-netstat:用Go编写的netstat实现

- meanBackend:我正在一个完整JavaScript环境中工作!

- square-kappa

- Android应用源码多种特效,实现多种动画,抽屉效果、多种自定义的view-IT计算机-毕业设计.zip

- 基于java的大数据分析.zip