The Structure of the ARMulator

6 Copyright © 2003 ARM Limited. All rights reserved. Application Note 32

ARM DAI 0032F

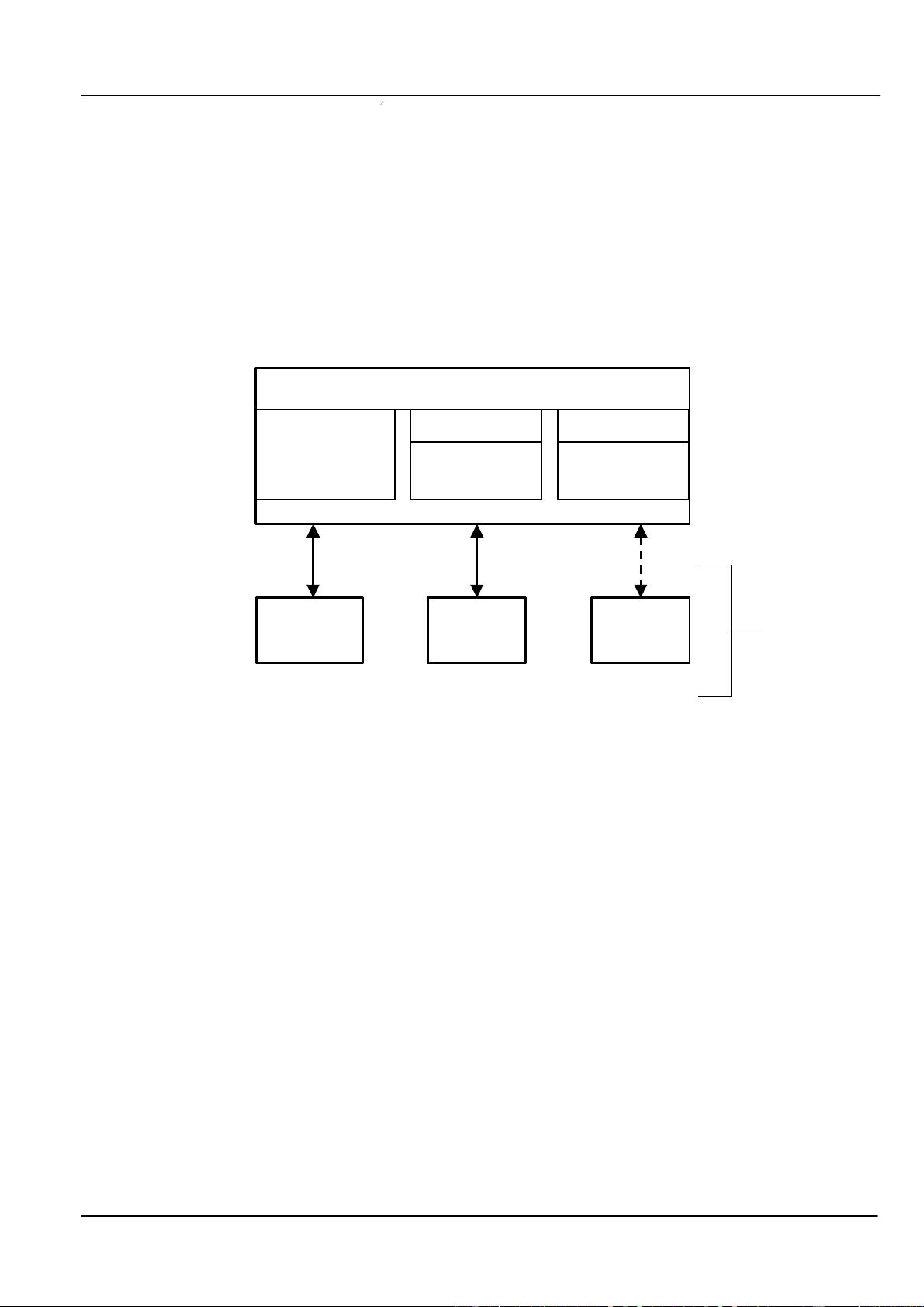

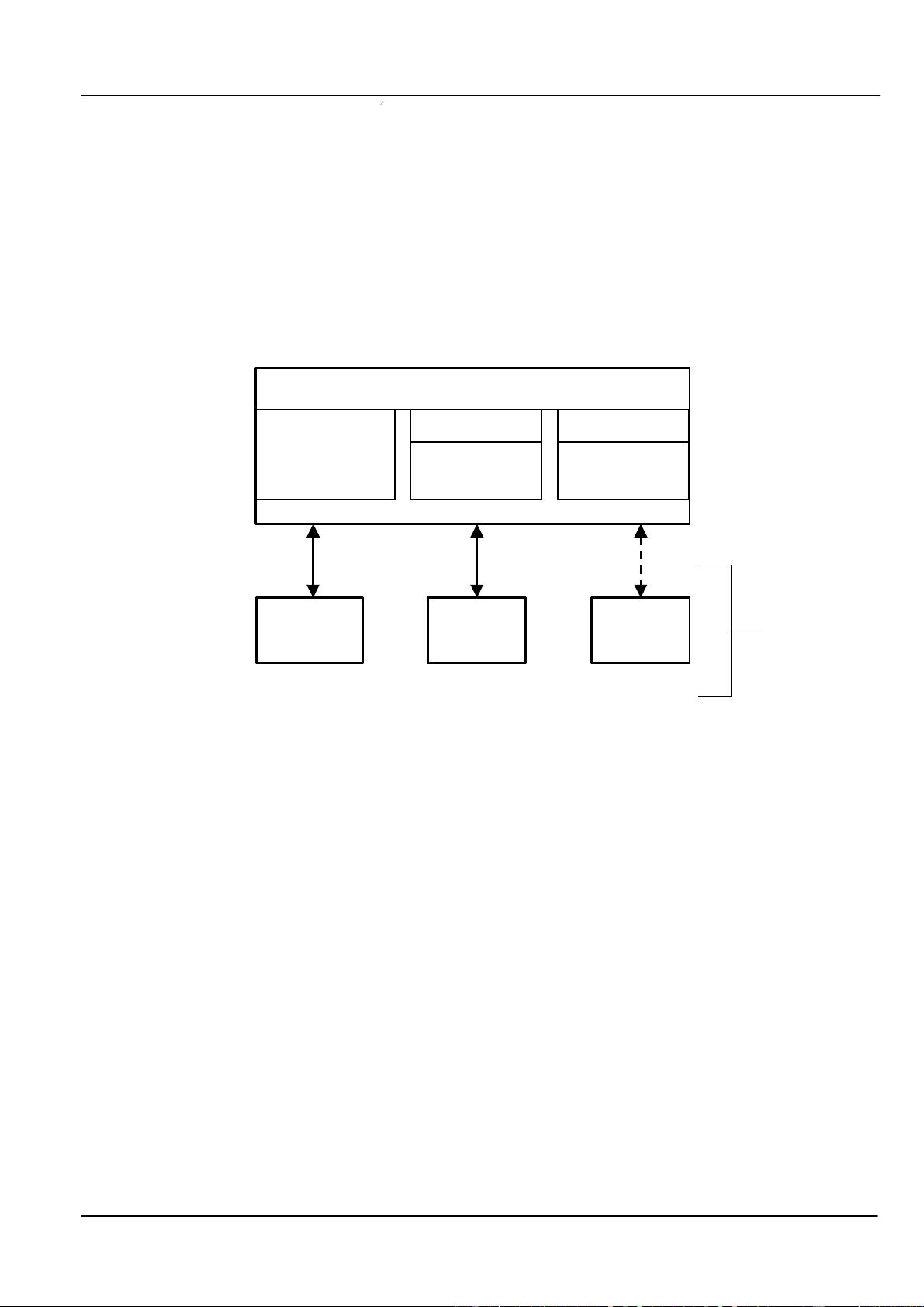

2 The Structure of the ARMulator

The ARMulator comprises several parts:

• a model of the ARM processor core and cache (if used)

• peripheral models that communicate with the base memory model and may be

enabled or disabled via configuration files

• an operating system interface to provide an execution environment.

By modifying or rewriting the supplied models, you can model almost any ARM system

and use it to debug code. The following diagram illustrates this structure.

ARMULATE.SDI

ARM7 & ARM9

Core Model

(+ Cache)

ARMISS.SDI v6 ARMISS.SDI

ARM10 + XScale

+ Cache

Architecture v6

Interrupt

Controller

Timer (Others)

Peripheral

Models

Peripherals are registered by calling the functions ARMulif_ReadBusRange and

bus_registerPeripFunc during model initialisation. This is explained fully with an

example in section 4.2 Explanation (Parallel Port Model). Address settings may either be

hard-coded or loaded in from a configuration (.ami or .dsc) file prior to registration. The

user provides:

• a base address at which the peripheral is located

• the number of bytes which are covered by the peripheral model.

It is possible to have gaps within this range which are not decoded by a peripheral.

In the diagram above, ARMULATE.SDI represents the main ARMulator component. Below

this resides a model of the core being emulated along with any cache if it has been

configured. At the lowest level is a flat memory model (with the full 32 bit, 4GB range

accessible) and the peripheral decoder. Prior to ADS 1.2, the decoder and flat memory

model were integral to the ARMulator and could not be modified. However, this is not the

case in ADS 1.2 and RV ARMulator ISS.

2.1 The ARM processor core model

The ARM processor core model handles all communication with the debugger. This part

of the ARMulator is not customizable.