台湾学者详解PLL设计:原理与应用

需积分: 9 47 浏览量

更新于2024-07-05

1

收藏 1.05MB PDF 举报

台湾学者Ching-Yuan Yang在国立中兴大学电气工程系的课程"PLL及应用-2004"中,深入探讨了相位锁定环路(Phase-Locked Loop, PLL)的设计与应用。PLL是数字集成电路设计中的关键组件,主要用于抑制时钟抖动、频率合成、时钟恢复以及减少系统中的时钟偏差。课程内容包括以下几个部分:

1. **概述**:介绍了PLL的基本原理,重点阅读材料推荐了B.Razavi的《Analog CMOS Integrated Circuit Design》第15章以及Cicero S.Vaucher的《Architectures for RF Frequency Synthesizers》第2章,这两本书提供了关于PLL理论和技术基础的深入理解。

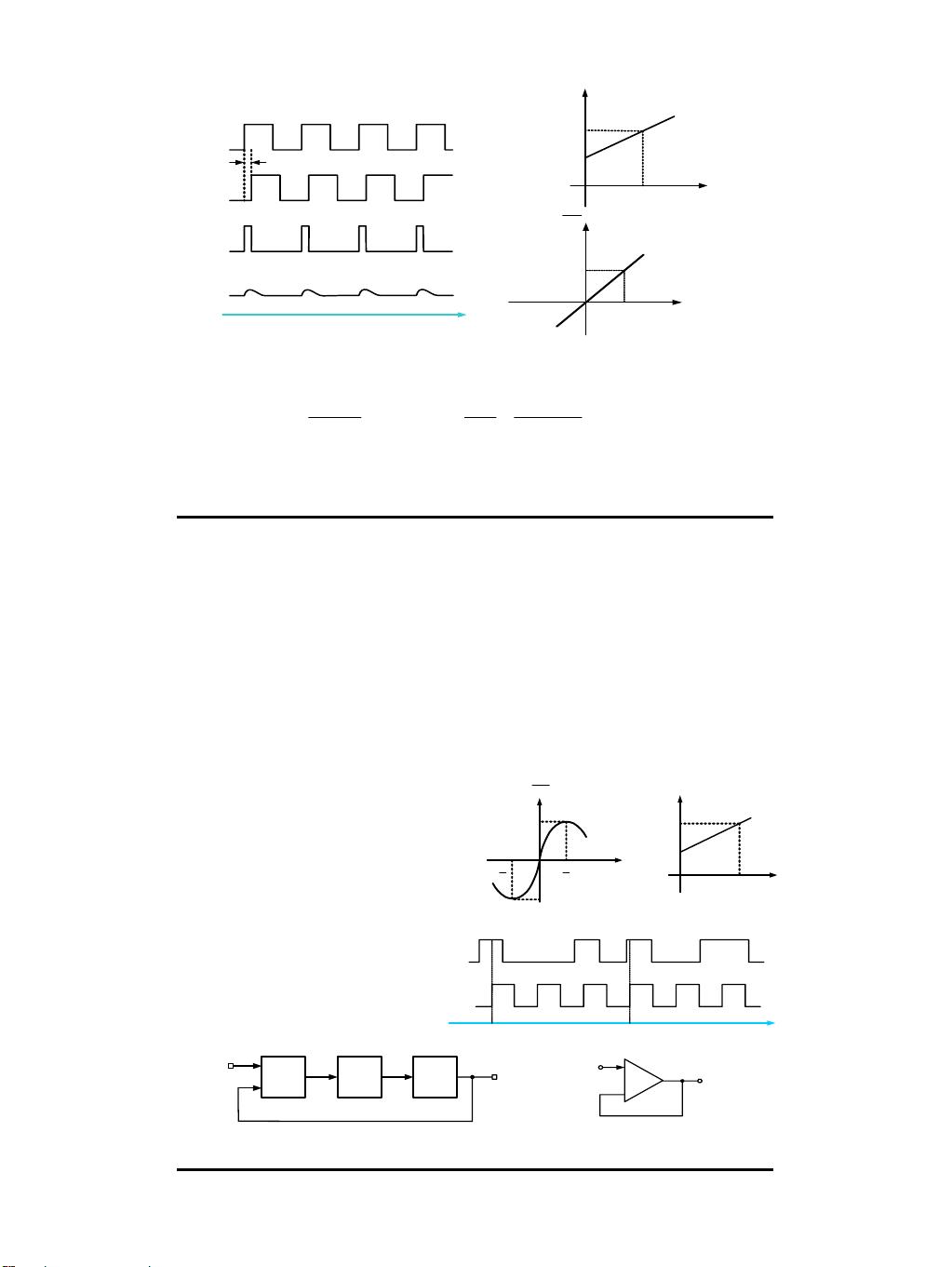

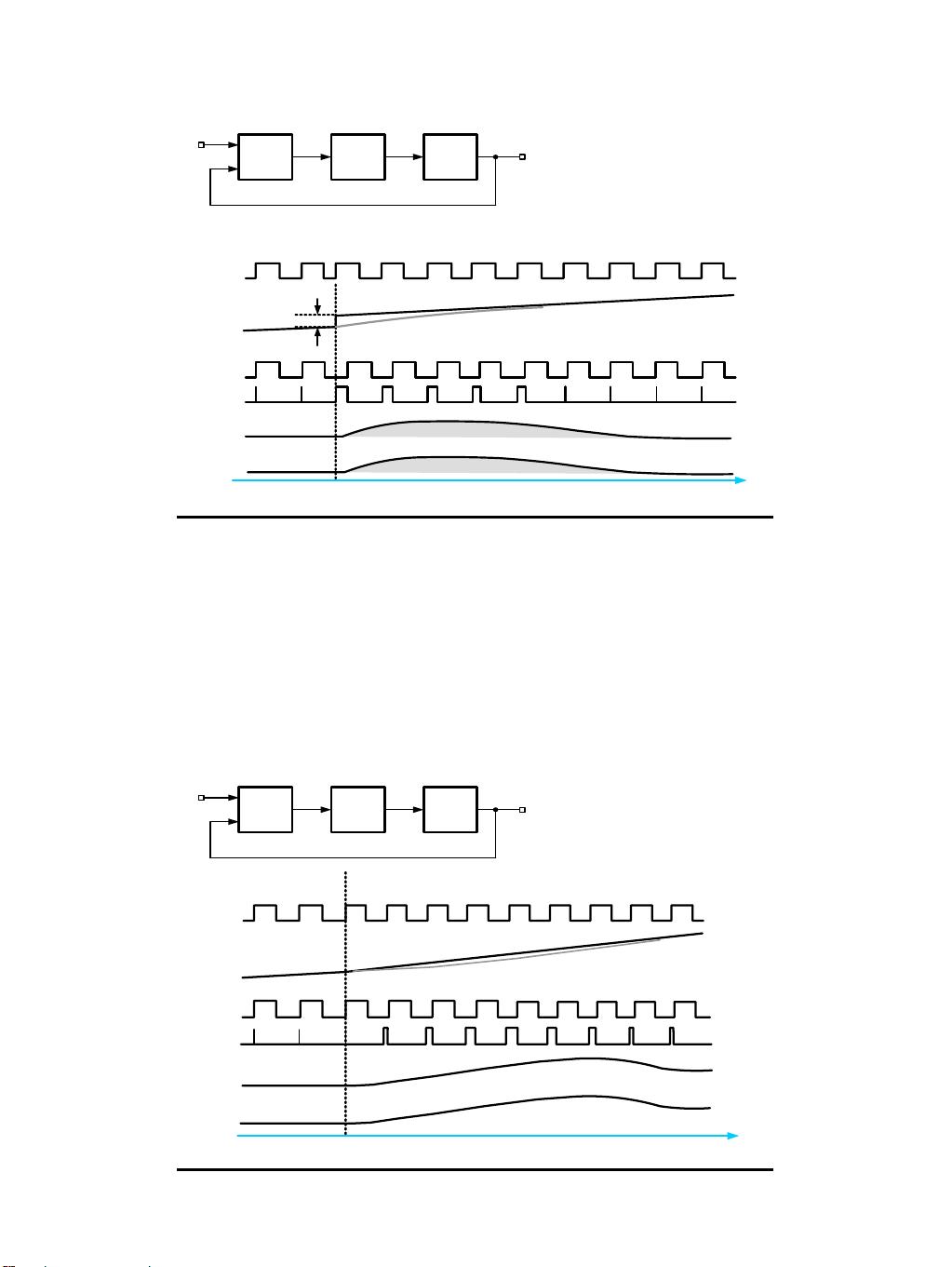

2. **简单相位锁定环路**:这部分讲解了PLL的基本结构,包括其工作原理,即利用相位检测器(Phase Detector, PD)测量输入信号x(t)和参考信号y(t)之间的相位差,并通过误差放大器进行反馈调整,直至达到锁定状态,确保输出信号的稳定频率。

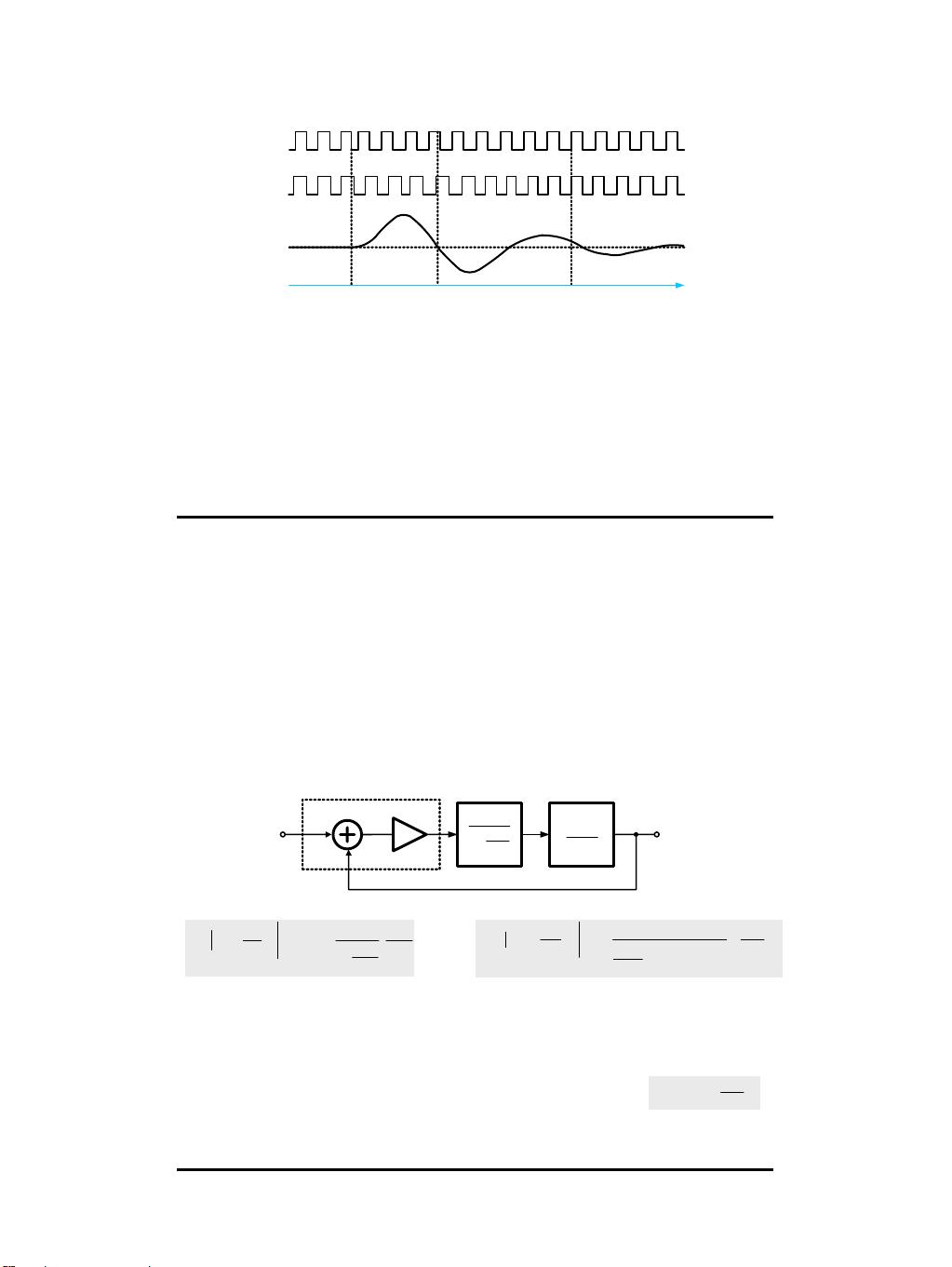

3. **电荷泵相位锁定环路**:相比于简单的PLL,电荷泵PLL使用了额外的电路来提供相位控制,适用于需要更高精度和速度的应用,如微处理器的时钟同步。

4. **非理想效应**:PLL并非完美的解决方案,实际应用中会遇到如锁定范围限制、噪声和 jitter(抖动)等问题。这部分着重讨论了这些非理想因素对PLL性能的影响以及如何减小它们。

5. **PLL的应用**:PLL广泛应用于各种领域,如数字信号处理、无线通信、数据传输等。例如,用于900~925MHz频率合成的系统,或者在光纤接收器中实现数据时钟的恢复,以解决时钟偏移问题。

6. **行为仿真**:课程还包括PLL行为的模拟,这对于理解和优化设计至关重要,通过模拟可以预测不同条件下PLL的实际性能。

7. **实例分析**:以具体场景如CPU、内存和I/O接口的时钟同步为例,展示了PLL在解决时钟偏斜和恢复问题中的作用,以及微处理器如何利用PLL来改善体验。

通过学习这门课程,学生不仅可以掌握PLL的基础理论,还能了解其实现技术在现代电子系统中的实际应用,这对于从事IC设计和信号处理领域的专业人士来说,是一门不可或缺的技术课程。

2024-10-07 上传

2020-04-30 上传

2024-06-20 上传

2021-10-02 上传

shijuntao1985

- 粉丝: 2

- 资源: 73

最新资源

- Cucumber-JVM模板项目快速入门教程

- ECharts打造公司组织架构可视化展示

- DC Water Alerts 数据开放平台介绍

- 图形化编程打造智能家居控制系统

- 个人网站构建:使用CSS实现风格化布局

- 使用CANBUS控制LED灯柱颜色的Matlab代码实现

- ACTCMS管理系统安装与更新教程

- 快速查看IP地址及地理位置信息的View My IP插件

- Pandas库助力数据分析与编程效率提升

- Python实现k均值聚类音乐数据可视化分析

- formdotcom打造高效网络表单解决方案

- 仿京东套餐购买列表源码DYCPackage解析

- 开源管理工具orgParty:面向PartySur的多功能应用程序

- Flutter时间跟踪应用Time_tracker入门教程

- AngularJS实现自定义滑动项目及动作指南

- 掌握C++编译时打印:compile-time-printer的使用与原理