FPGA组合逻辑实验:Vivado实现38译码器与全加器

需积分: 0 104 浏览量

更新于2024-08-05

收藏 3.09MB PDF 举报

"本次实验是关于组合逻辑设计的实践,主要使用了Vivado软件进行FPGA实现。实验包括三个部分:按照‘Vivado工程1.pdf’的案例完成实验,‘Vivado工程2.pdf’中的38译码器及多数表决器实现,以及一位全加器和四位加减法器的构建。实验目的是让学生掌握FPGA实现组合逻辑的基本方法,并通过板上运行验证设计的正确性。"

实验中涉及的知识点包括:

1. **Vivado软件**:Vivado是一款由Xilinx公司开发的综合设计环境,用于FPGA的设计、仿真、实现和调试。在实验中,学生需要学会使用Vivado创建项目、编写Verilog代码、配置IP核、仿真验证以及生成硬件描述语言(HDL)代码。

2. **组合逻辑设计**:组合逻辑是由一组无记忆的逻辑门组成的电路,其输出仅依赖于当前的输入状态,不具有存储信息的能力。实验中涉及的38译码器和多数表决器都是组合逻辑电路的例子。

3. **38译码器**:这是一种多输入多输出的逻辑电路,可以将一个高位二进制数字转化为多个低位输出,用于地址解码或数据选择等功能。在实验第二部分,学生需要生成38译码器的IP核,并使用它来实现多数表决器。

4. **多数表决器**:多数表决器是一种逻辑电路,用于确定多个输入信号中占多数的信号状态。在本实验中,可能要求学生设计一个电路,当超过半数的输入为某一状态时,输出就跟随这一状态。

5. **一位全加器**:全加器是能够处理进位的加法运算单元,可以将两个二进制位及一个进位输入相加,产生和与进位两个输出。实验要求学生实现一位全加器模块,并理解Ci、Si和Ci_1的含义。

6. **四位加减法器**:基于一位全加器,学生需要设计一个四位加减法器,能够进行4位二进制数的加法和减法运算。输入A和B通过开关(sw)控制,输出S和C通过LED显示,还包含溢出位(O)。

7. **Verilog HDL**:实验中所有逻辑电路的描述都是使用Verilog硬件描述语言完成的。学生需要熟悉Verilog语法,如输入输出声明、逻辑操作符(如^表示异或)、赋值语句(assign)等。

8. **约束源文件**:在FPGA设计中,约束文件用于指定物理引脚分配和时序约束,确保设计能正确地映射到FPGA芯片上。学生需要学习如何编写约束源文件来连接硬件接口。

9. **仿真验证**:在设计完成后,学生需要进行功能仿真以检验设计的正确性,通过观察仿真波形图判断逻辑运算是否符合预期。

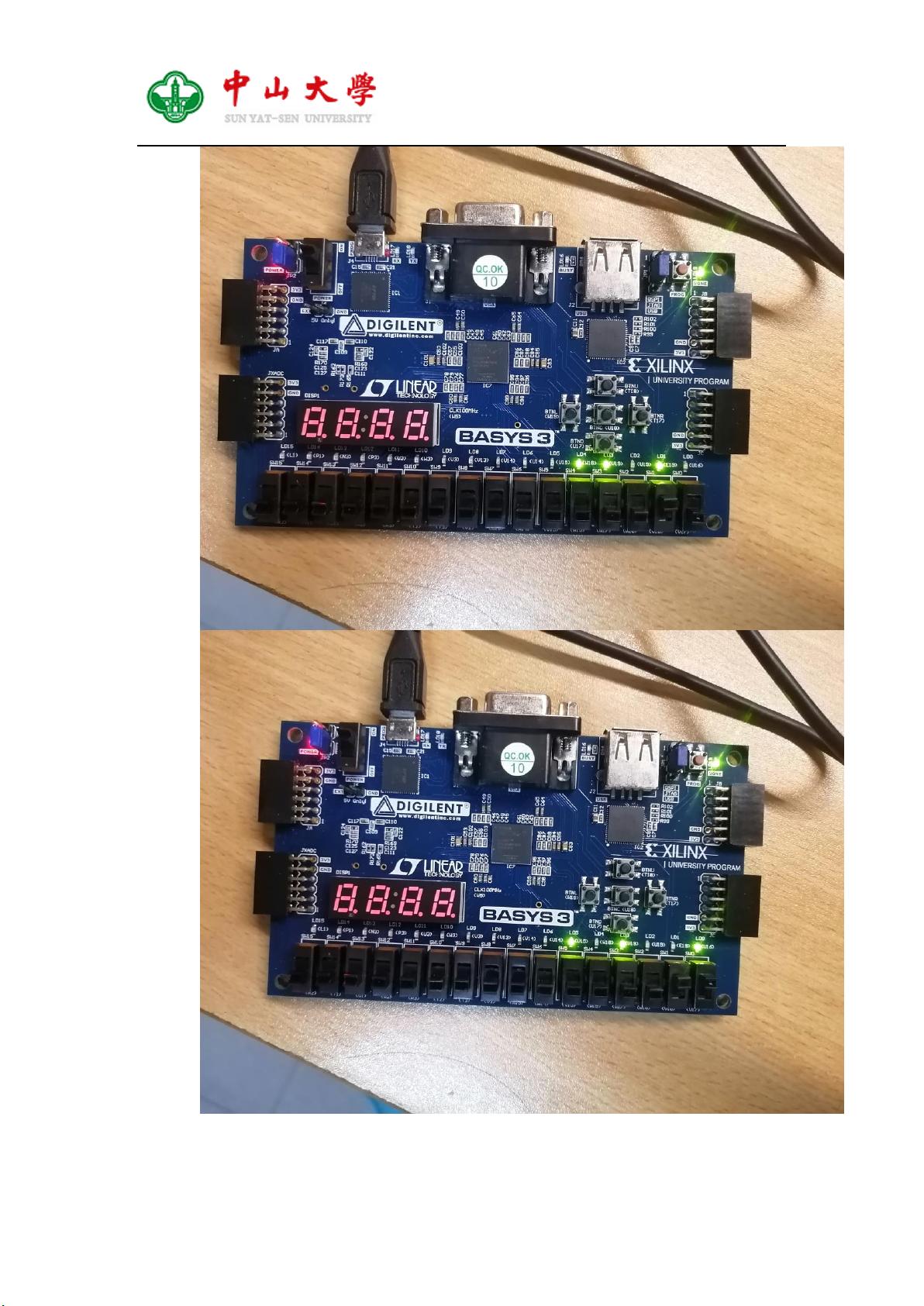

10. **板上运行**:实验的最后一步是将设计下载到FPGA板上实际运行,并拍照记录结果,这验证了设计在硬件上的正确性。

通过这个实验,学生不仅掌握了基本的组合逻辑设计,还熟悉了FPGA开发流程,以及Verilog编程和硬件验证的方法。

238 浏览量

点击了解资源详情

点击了解资源详情

145 浏览量

2021-10-28 上传

2021-07-09 上传

2021-11-22 上传

2022-08-04 上传

俞林鑫

- 粉丝: 20

最新资源

- MATLAB实现ART与SART算法在医学CT重建中的应用

- S2SH整合版:快速搭建Struts2+Spring+Hibernate开发环境

- 托奇卡项目团队成员介绍

- 提升外链发布效率的SEO推广神器——搜易达网络推广大师v2.035

- C#打造简易记事本应用详细教程

- 探索虚拟现实地图VR的奥秘

- iOS模拟器屏幕截图新工具

- 深入解析JavaScript在生活应用开发中的运用

- STM32F10x函数库3.5中文版详解与应用

- 猎豹浏览器v6.0.114.13396 r1:安全防护与网购敢赔

- 掌握JS for循环输出的最简洁代码技巧

- Java入门教程:TranslationFileGenerator快速指南

- OpenDDS3.9源码解析及最新文档指南

- JavaScript提示框插件:鼠标滑过显示文章摘要

- MaskRCNN气球数据集:优质图像识别资源

- Laravel日志查看器:实现Apache多站点日志统一管理