VHDL设计:ADC0809 A/D转换器状态机控制实验报告

版权申诉

27 浏览量

更新于2024-08-26

1

收藏 404KB DOC 举报

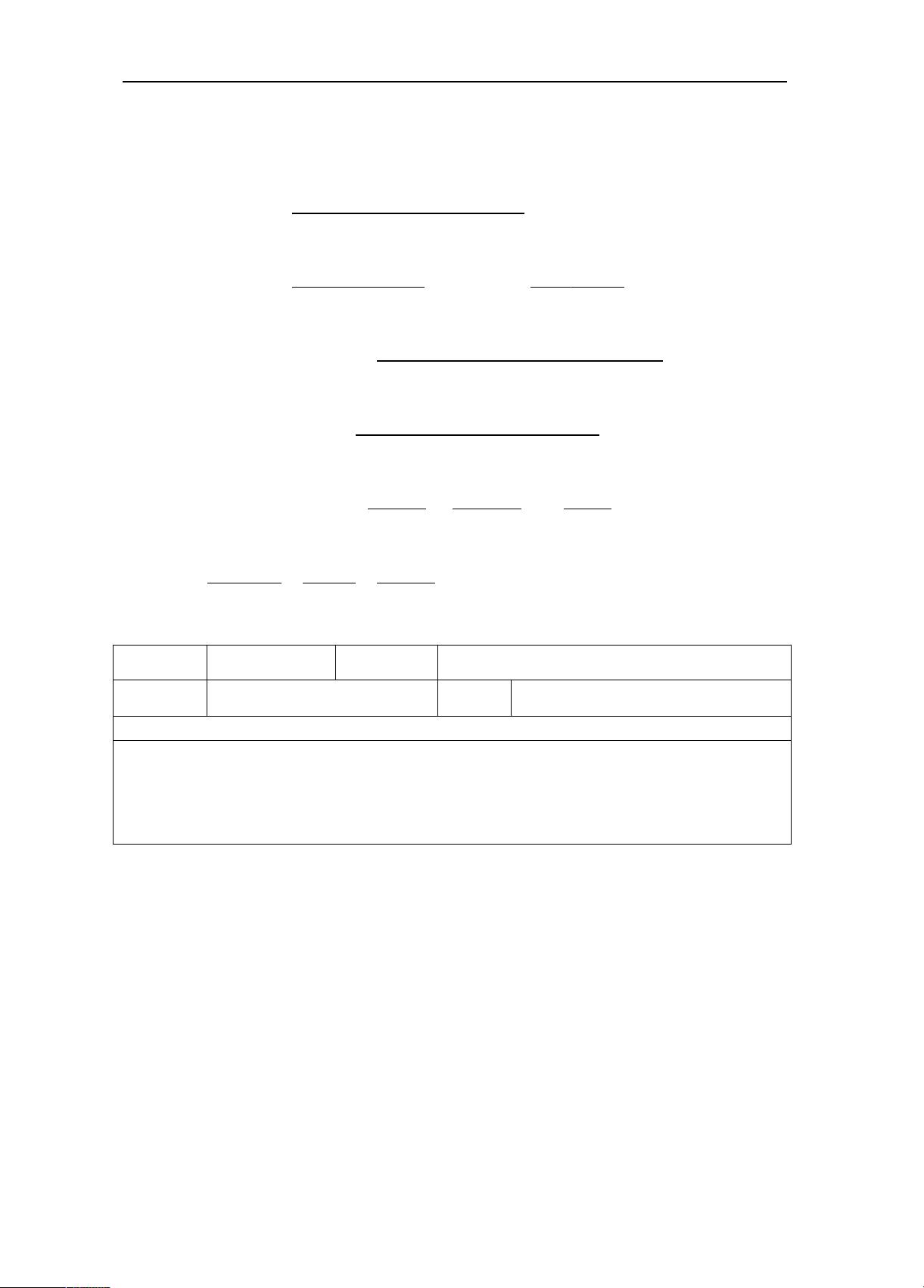

本实验报告旨在引导本科学生通过VHDL语言设计有限状态机来控制ADC0809 A/D转换器的采样控制电路。实验者是114090315学号的开斌,来自物电学院11电子专业,进行的是电子设计自动化(EDA)实验课程,指导教师罗永道副教授。该实验发生在2013至2014学年下学期,于2014年5月30日提交。

实验的核心目标是熟悉并应用VHDL编程,通过构建状态机来精确管理ADC0809的工作流程,包括模拟信号的选择、转换启动、状态检测以及数据输出。ADC0809是一款8位CMOS A/D转换器,具有8路模拟开关,分辨率为8位,转换时间为约100us。关键控制信号包括START、ALE和EOC,它们分别是转换启动、地址锁存和转换结束信号。

实验设备和材料包括一台电脑、Quartus II实验平台以及EDA实验箱。实验过程分为预习阶段和实际操作步骤:

1. 实验预习阶段:

- 学生需要了解ADC0809的工作原理,如模拟量输入选择、转换触发和结果输出的流程。

- 了解状态机的基本概念,如状态机的组成部分,包括状态类型定义、状态变量的设置以及与外部时钟同步的工作机制。

2. 实验方法步骤:

- 在VHDL设计中,首先定义新数据类型和状态类型,例如使用枚举类型表示状态,每个状态应有明确的命名规则,以便理解和调试。

- 创建主控时序进程,这是状态机的核心部分,它会根据实验箱提供的工作时钟信号变化,驱动状态机从一个状态转换到下一个状态。

- 设计状态机流程,比如模拟启动转换、读取地址选择、等待EOC信号确认转换结束,以及在EOC上升沿后控制数据输出。

- 采用Quartus II环境编写并仿真VHDL代码,验证状态机的正确性和性能。

3. 注意事项:

- 确保VHDL代码的清晰性和可读性,合理组织模块,避免冗余和错误。

- 实验过程中要关注时间和效率,因为ADC0809的转换时间约为100us,需要合理安排状态机的切换。

- 需要充分理解并正确处理EOC信号,以确保数据的正确输出。

通过这个实验,学生不仅可以提升VHDL编程能力,还能深入了解A/D转换器的控制逻辑,培养硬件设计的实际操作技巧。

2023-06-06 上传

2022-09-21 上传

2021-09-17 上传

2024-11-01 上传

2024-11-01 上传

2024-10-25 上传

2024-06-26 上传

2023-06-01 上传

2024-10-25 上传

天泽通信

- 粉丝: 3

- 资源: 5万+

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜