ISE时序约束详解与应用

需积分: 31 30 浏览量

更新于2024-07-16

2

收藏 471KB DOC 举报

"ISE时序约束笔记_中文翻译版.doc"

在数字集成电路设计中,时序约束是优化设计性能的关键步骤,特别是在使用Xilinx的ISE(Integrated Synthesis Environment)工具进行FPGA或CPLD设计时。时序约束指导设计工具如布局布线器,以满足特定的性能指标,例如最大工作频率或最小延迟要求。本文档详细介绍了ISE中的时序约束技巧和方法。

首先,理解时序约束的重要性是至关重要的。设计工具并不会自动寻找最优的布局布线方案以达到最高的运行速度,而是根据用户设定的时序约束来优化设计。没有时序约束的设计可能导致无法预测的性能,而添加适当的约束可以帮助提升设计的时钟频率。

文档中提到了两种情况对比:一个无时序约束的设计只能运行到50MHz,而另一个添加了全局时序约束的设计则可以达到60MHz。这凸显了时序约束对提高系统时钟频率的直接影响。时序约束可以将逻辑元件放置得更接近,减少布线延迟,从而改善整体性能。

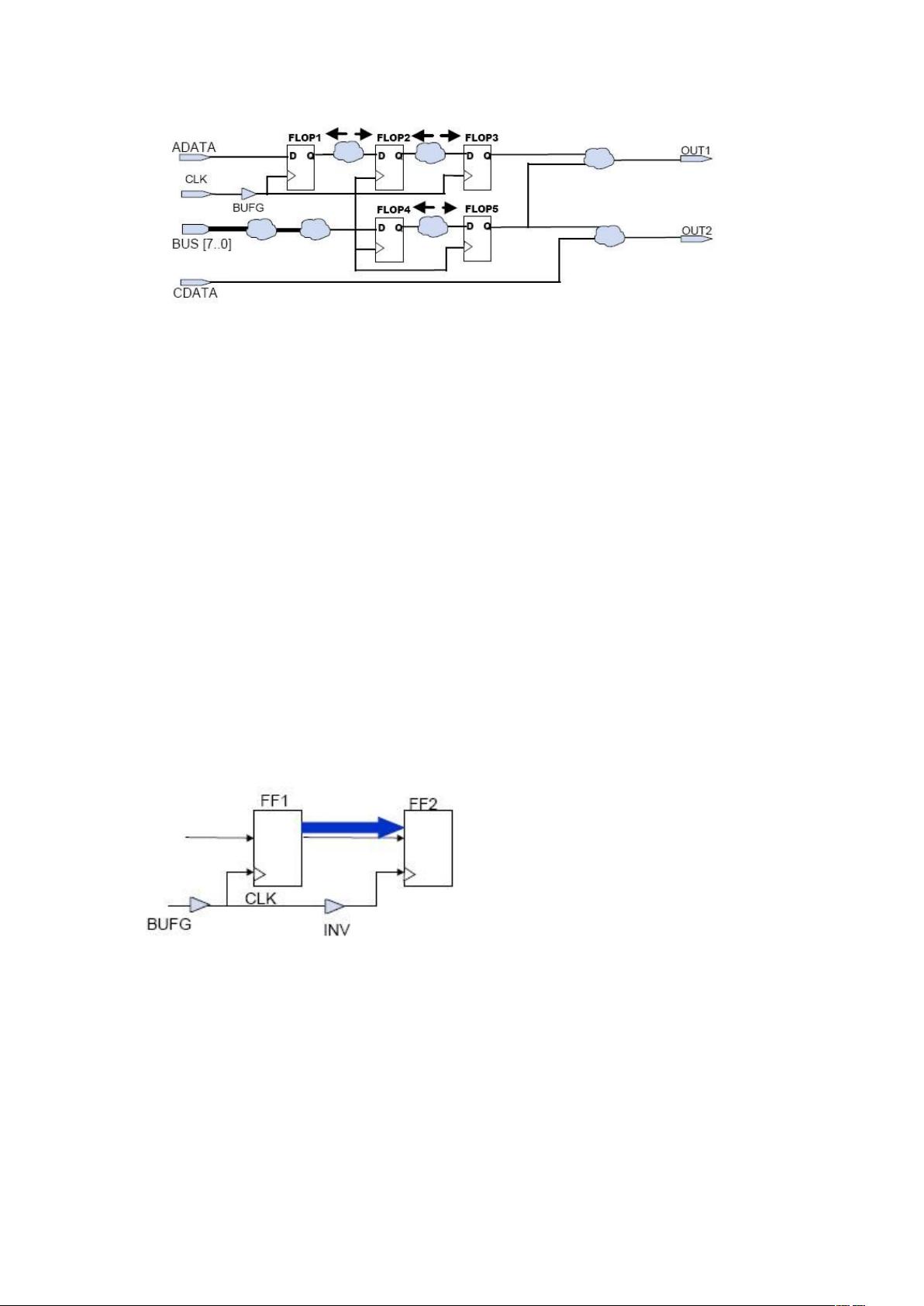

时序约束主要分为两个步骤:确定路径终点并设置路径之间的时序要求。路径终点可以是输入/输出引脚(I/O pads)或同步单元,如触发器、锁存器和RAM。全局约束通常应用于所有触发器和I/O引脚,确保所有相关路径都被覆盖。

问题思考部分探讨了如何识别路径终点和共享时钟的多个寄存器。在这种情况下,路径终点是所有共享相同时钟信号的寄存器,对这些寄存器的时序约束可以同时约束所有相关路径的延迟。

周期约束是时序约束的一种类型,用于指定由同一时钟网络控制的同步单元之间的路径延迟。这种约束不包括纯组合逻辑路径,如输入引脚到输出引脚,或输入引脚到同步单元,以及同步单元到输出引脚的路径。周期约束利用最精确的时序信息来计算时钟偏斜(Clock Skew),确保在给定周期内正确同步数据传输。

ISE时序约束笔记提供了一个全面的指南,帮助设计者理解和应用有效的时序约束策略,以达到最佳的设计性能。设计者应根据综合报告和映射后的静态时序分析来调整和验证约束,确保设计满足性能目标,并在布局布线后达到预期的时序要求。理解并熟练运用时序约束是提升FPGA设计效率和可靠性的基础。

2022-09-24 上传

2022-09-24 上传

2022-09-24 上传

2022-09-21 上传

2022-09-21 上传

2022-09-19 上传

weixin_40022273

- 粉丝: 3

- 资源: 3

最新资源

- 前端协作项目:发布猜图游戏功能与待修复事项

- Spring框架REST服务开发实践指南

- ALU课设实现基础与高级运算功能

- 深入了解STK:C++音频信号处理综合工具套件

- 华中科技大学电信学院软件无线电实验资料汇总

- CGSN数据解析与集成验证工具集:Python和Shell脚本

- Java实现的远程视频会议系统开发教程

- Change-OEM: 用Java修改Windows OEM信息与Logo

- cmnd:文本到远程API的桥接平台开发

- 解决BIOS刷写错误28:PRR.exe的应用与效果

- 深度学习对抗攻击库:adversarial_robustness_toolbox 1.10.0

- Win7系统CP2102驱动下载与安装指南

- 深入理解Java中的函数式编程技巧

- GY-906 MLX90614ESF传感器模块温度采集应用资料

- Adversarial Robustness Toolbox 1.15.1 工具包安装教程

- GNU Radio的供应商中立SDR开发包:gr-sdr介绍