5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

PM_EXTTS#0

PM_EXTTS#1

+H_RCOMP

+H_SWING

H_D#32

H_D#24

H_D#19

H_D#59

H_D#42

H_D#36

H_D#3

H_D#40

+H_RCOMP

H_D#55

H_D#4

H_D#60

H_D#30

H_D#34

H_D#27

H_D#1

H_D#23

H_D#51

H_D#48

H_D#46

H_D#44

H_D#39

H_D#22

H_D#15

H_D#14

H_D#9

H_D#56

H_D#54

H_D#8

H_RESET#

H_D#37

H_D#35

H_D#28

H_D#25

H_D#12

H_D#38

H_D#26

H_D#11

H_D#7

H_D#53

H_D#52

H_D#41

H_D#18

H_D#10

+H_VREF

H_D#57

H_D#33

H_D#29

+H_SWING

H_D#6

H_D#45

H_D#43

H_D#20

H_D#61

H_D#17

H_D#63

H_D#58

H_D#21

H_D#16

H_D#50

H_CPUSLP#

H_D#62

H_D#5

H_D#49

H_D#31

H_D#2

H_D#47

H_D#13

H_D#0

+H_VREF

+SMRCOMP_VOH

+SMRCOMP_VOL

+V_DDR_MCH_REF

H_LOCK#

CLK_MCH_BCLK#

H_ADS#

H_HITM#

H_DEFER#

H_ADSTB#1

CLK_MCH_BCLK

H_DRDY#

H_BPRI#

H_HIT#

H_DBSY#

H_BR0#

H_TRDY#

H_ADSTB#0

H_DPWR#

H_BNR#

H_DSTBN#1

H_DSTBN#2

H_DSTBN#0

H_DSTBN#3

H_REQ#0

H_REQ#1

H_REQ#3

H_REQ#4

H_REQ#2

H_DINV#0

H_DINV#3

H_DINV#1

H_DINV#2

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBP#3

H_RS#1

H_RS#0

H_RS#2

H_A#32

H_A#12

H_A#7

H_A#19

H_A#16

H_A#21

H_A#18

H_A#3

H_A#24

H_A#9

H_A#30

H_A#5

H_A#27

H_A#31

H_A#23

H_A#22

H_A#11

H_A#14

H_A#26

H_A#25

H_A#6

H_A#15

H_A#8

H_A#20

H_A#34

H_A#29

H_A#33

H_A#13

H_A#4

H_A#17

H_A#35

H_A#10

H_A#28

ADC_ACZ_SDIN0_GMCH

CLK_3GPLLREQ#

MCH_ICH_SYNC#

TSATN#

CL_CLK0

CL_RST#

M_PWROK

CL_DATA0

+CL_VREF

DMI_ITX_MRX_N1

DMI_ITX_MRX_N0

DMI_ITX_MRX_P2

DMI_ITX_MRX_P0

DMI_MTX_IRX_N0

DMI_ITX_MRX_P3

DMI_ITX_MRX_N3

DMI_ITX_MRX_N2

DMI_MTX_IRX_P1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_N1

DMI_ITX_MRX_P1

DMI_MTX_IRX_P3

DMI_MTX_IRX_P2

DMI_MTX_IRX_P0

MCH_DREFCLK

MCH_DREFCLK#

DREF_SSCLK#

DREF_SSCLK

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

SM_REXT

TP_SM_DRAMRST#

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR3

+V_DDR_MCH_REF

M_CLK_DDR2

M_CLK_DDR1

M_CLK_DDR0

M_CLK_DDR#3

M_CLK_DDR#2

SMRCOMP#

+SMRCOMP_VOH

M_ODT1

+SMRCOMP_VOL

DDR_CKE0_DIMMA

SMRCOMP

M_ODT2

M_ODT0

M_ODT3

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS1_DIMMA#

DDR_CS3_DIMMB#

DDR_CKE1_DIMMA

DDR_CS2_DIMMB#

DDR_CS0_DIMMA#

CFG5

CFG9

CFG19

CFG6

CPU_MCH_BSEL0

CPU_MCH_BSEL2

CPU_MCH_BSEL1

CFG12

CFG20

CFG7

CFG13

CFG16

H_THERMTRIP#

DPRSLPVR

PM_EXTTS#1

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_PWROK_R

PLT_RST#_NB

PM_PWROK_R

MCH_DREFCLK

MCH_DREFCLK#

DREF_SSCLK

DREF_SSCLK#

H_DPRSTP#

+VCCP

+VCCP

+3VS

+1.8V

+1.8V

+V_DDR_MCH_REF +VCCP

+VCCP

+1.8V

+V_DDR_MCH_REF

H_D#[0..63]<8>

H_CPUSLP#<8>

H_RESET#<7>

H_ADS# <7>

H_BNR# <7>

H_ADSTB#1 <7>

H_ADSTB#0 <7>

H_BR0# <7>

H_BPRI# <7>

H_DBSY# <7>

H_DEFER# <7>

H_TRDY# <7>

H_DRDY# <7>

H_DPWR# <8>

H_HITM# <7>

H_HIT# <7>

H_LOCK# <7>

CLK_MCH_BCLK# <6>

CLK_MCH_BCLK <6>

H_DINV#1 <8>

H_DINV#2 <8>

H_DINV#0 <8>

H_DINV#3 <8>

H_DSTBN#2 <8>

H_DSTBN#0 <8>

H_DSTBN#1 <8>

H_DSTBP#0 <8>

H_DSTBN#3 <8>

H_DSTBP#1 <8>

H_DSTBP#3 <8>

H_DSTBP#2 <8>

H_REQ#0 <7>

H_REQ#1 <7>

H_REQ#2 <7>

H_REQ#3 <7>

H_REQ#4 <7>

H_RS#0 <7>

H_RS#1 <7>

H_RS#2 <7>

H_A#[3..35] <7>

GMCH_HDA_BITCLK <22>

GMCH_HDA_SYNC <22>

GMCH_HDA_RST# <22>

ADC_GMCH_SDIN2 <22>

GMCH_HDA_SDOUT <22>

CLK_3GPLLREQ# <6>

MCH_ICH_SYNC# <23>

GMCH_HDMIDAT <20>

GMCH_HDMICLK <20>

M_PWROK <23>

CL_DATA0 <23>

CL_CLK0 <23>

CL_RST# <23>

DMI_ITX_MRX_N1 <23>

DMI_ITX_MRX_N2 <23>

DMI_ITX_MRX_P0 <23>

DMI_ITX_MRX_P1 <23>

DMI_ITX_MRX_N0 <23>

DMI_ITX_MRX_P2 <23>

DMI_ITX_MRX_P3 <23>

DMI_ITX_MRX_N3 <23>

DMI_MTX_IRX_N0 <23>

DMI_MTX_IRX_N1 <23>

DMI_MTX_IRX_N2 <23>

DMI_MTX_IRX_P3 <23>

DMI_MTX_IRX_N3 <23>

DMI_MTX_IRX_P0 <23>

DMI_MTX_IRX_P1 <23>

DMI_MTX_IRX_P2 <23>

CLK_MCH_3GPLL# <6>

CLK_MCH_3GPLL <6>

MCH_DREFCLK# <6>

MCH_DREFCLK <6>

DREF_SSCLK <6>

DREF_SSCLK# <6>

M_CLK_DDR3 <17>

M_CLK_DDR0 <16>

M_CLK_DDR1 <16>

M_CLK_DDR#1 <16>

M_CLK_DDR#2 <17>

M_CLK_DDR2 <17>

DDR_CKE0_DIMMA <16>

DDR_CKE1_DIMMA <16>

M_CLK_DDR#0 <16>

DDR_CKE2_DIMMB <17>

DDR_CKE3_DIMMB <17>

M_CLK_DDR#3 <17>

M_ODT1 <16>

DDR_CS0_DIMMA# <16>

DDR_CS1_DIMMA# <16>

DDR_CS2_DIMMB# <17>

M_ODT3 <17>

DDR_CS3_DIMMB# <17>

M_ODT0 <16>

M_ODT2 <17>

CFG19<12>

CFG6<12>

CFG7<12>

CFG5<12>

CFG20<12>

CFG9<12>

CFG16<12>

CPU_MCH_BSEL1<6,8>

CPU_MCH_BSEL2<6,8>

CPU_MCH_BSEL0<6,8>

ICH_PWROK<23,30>

PLT_RST#<21,27,30,34>

DPRSLPVR<23,48>

H_THERMTRIP#<7,22>

PM_BMBUSY#<23>

PM_EXTTS#0<16>

H_DPRSTP#<8,22,48>

PM_EXTTS#1<17>

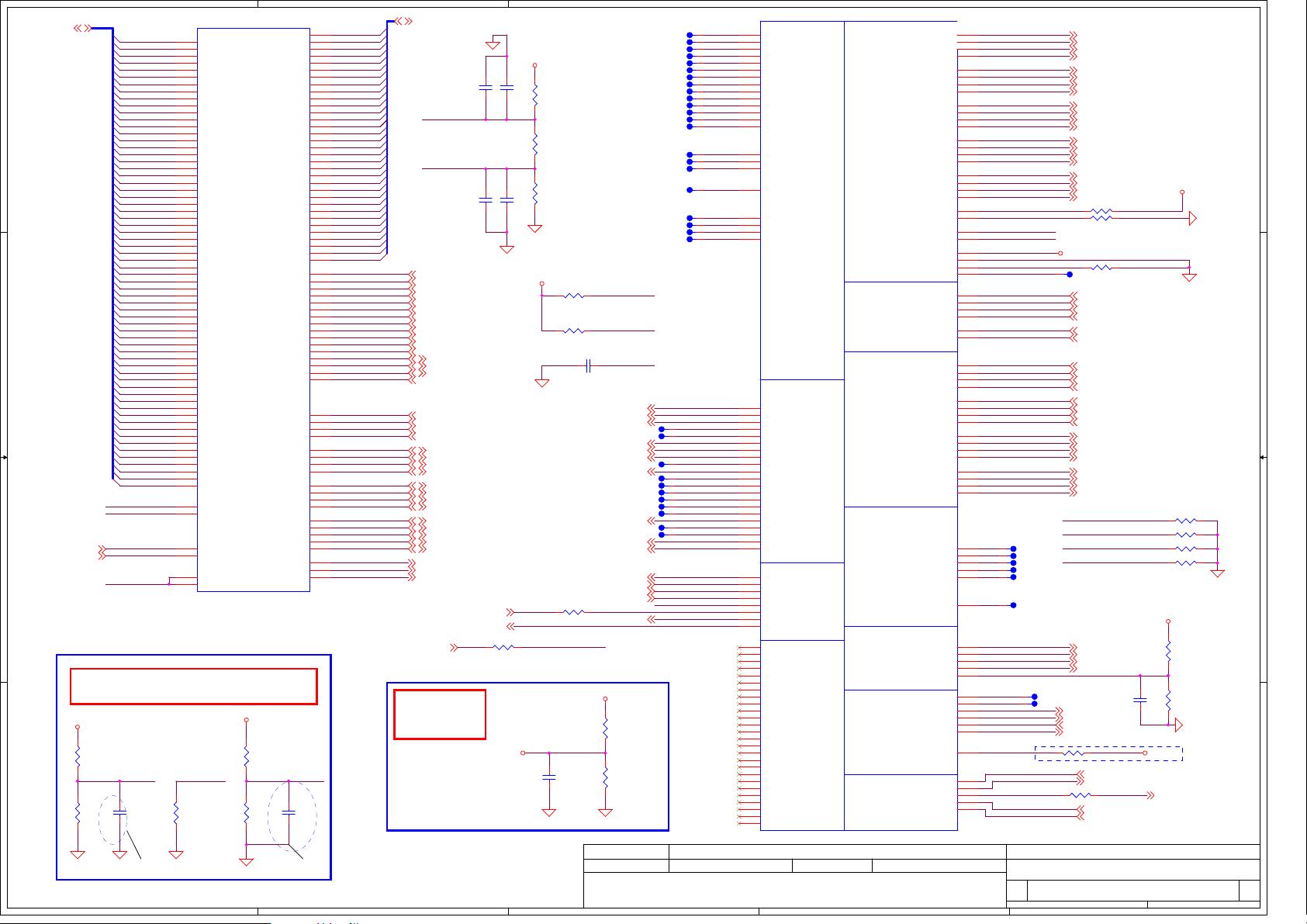

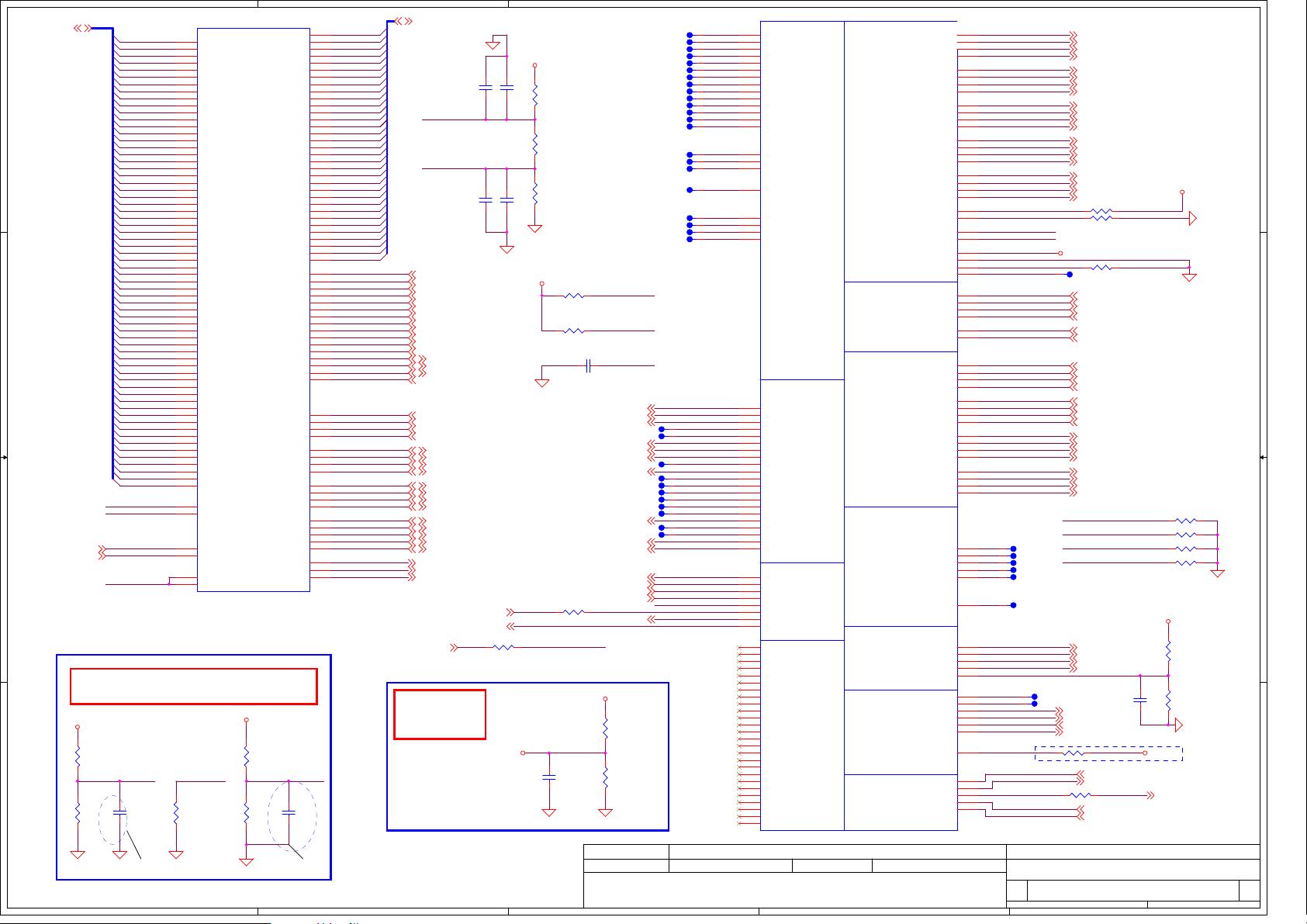

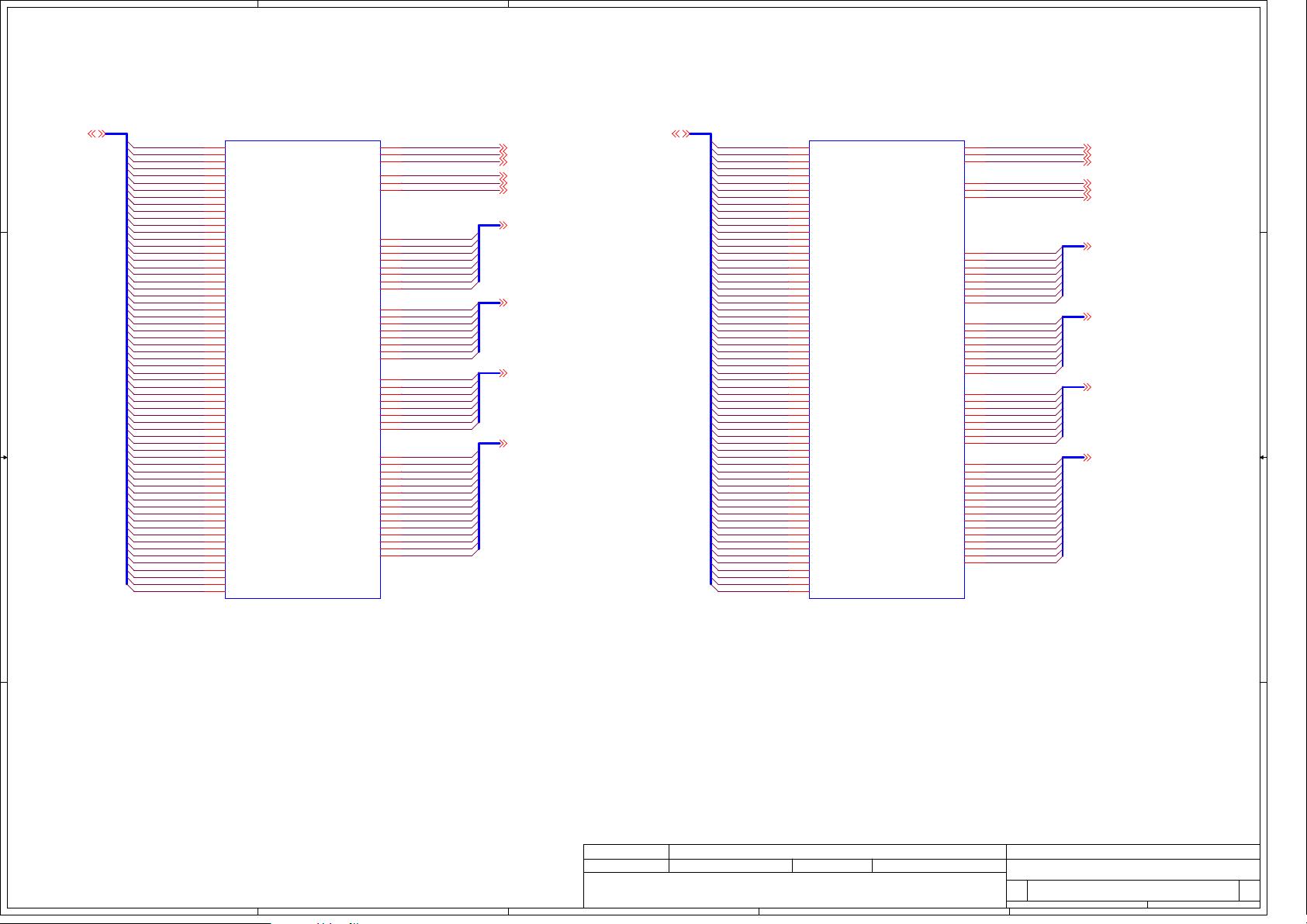

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-5162P

0.2

Cantiga(1/6)-AGTL/DMI/DDR

Custom

10 60Monday, April 20, 2009

2009/01/05 2009/01/05

Compal Electronics, Inc.

Layout Note:

+H_RCOMP / +H_VREF / +H_SWING

trace width and spacing is 10/20

Near B3 pinwithin 100 mils from NB

Layout Note:

+V_DDR_MCH_REF

trace width and

spacing is 20/20.

0.35V

R1045

1K_0402_1%

12

R408 0_0402_5%

1 2

T44

R328 80.6_0402_1%

1 2

T11

R521 56_0402_5%

12

C403

2.2U_0603_6.3V6K~D

1

2

R42

1K_0402_1%

12

R324

24.9_0402_1%

12

T10

T73

RG158

0_0402_5%

@

1 2

T75

R331

1K_0402_1%

12

T29

R43

1K_0402_1%

12

T40

T27

T7

RG156

0_0402_5%

@

1 2

R329 80.6_0402_1%

1 2

T35

T8

T41

T23

C391

0.1U_0402_16V7K~D

@

1

2

C404

0.01U_0402_16V7K

1

2

C36

0.1U_0402_16V7K~D

@

12

R333

1K_0402_1%

12

RG160

0_0402_5%

@

1 2

R1040 499_0402_1%

1 2

T30

T25

T67

T72

R323

100_0402_1%

12

R98 33_0402_5%~D1@

1 2

T34

RG161

0_0402_5%

@

1 2

T136

T47

C400

0.01U_0402_16V7K

1

2

T21

R332

3.01K_0402_1%

12

T32

R322

221_0603_1%

12

T22

T37

R99

511_0402_1%

12

C398

2.2U_0603_6.3V6K~D

1

2

R46

2K_0402_1%

12

T31

HOST

U4A

CANTIGA ES_FCBGA1329

H_A#_3

A14

H_A#_4

C15

H_A#_5

F16

H_A#_6

H13

H_A#_7

C18

H_A#_8

M16

H_A#_9

J13

H_A#_10

P16

H_A#_11

R16

H_A#_12

N17

H_A#_13

M13

H_A#_14

E17

H_A#_15

P17

H_A#_16

F17

H_A#_17

G20

H_A#_18

B19

H_A#_19

J16

H_A#_20

E20

H_A#_21

H16

H_A#_22

J20

H_A#_23

L17

H_A#_24

A17

H_A#_25

B17

H_A#_26

L16

H_A#_27

C21

H_A#_28

J17

H_A#_29

H20

H_A#_30

B18

H_A#_31

K17

H_A#_32

B20

H_A#_33

F21

H_A#_34

K21

H_A#_35

L20

H_ADS#

H12

H_ADSTB#_0

B16

H_ADSTB#_1

G17

H_BNR#

A9

H_BPRI#

F11

H_BREQ#

G12

H_DEFER#

E9

H_DBSY#

B10

HPLL_CLK

AH7

HPLL_CLK#

AH6

H_DPWR#

J11

H_DRDY#

F9

H_HIT#

H9

H_HITM#

E12

H_LOCK#

H11

H_TRDY#

C9

H_DINV#_0

J8

H_DINV#_1

L3

H_DINV#_2

Y13

H_DINV#_3

Y1

H_DSTBN#_0

L10

H_DSTBN#_1

M7

H_DSTBN#_2

AA5

H_DSTBN#_3

AE6

H_DSTBP#_0

L9

H_DSTBP#_1

M8

H_DSTBP#_2

AA6

H_DSTBP#_3

AE5

H_REQ#_0

B15

H_REQ#_1

K13

H_REQ#_2

F13

H_REQ#_3

B13

H_REQ#_4

B14

H_RS#_0

B6

H_RS#_1

F12

H_RS#_2

C8

H_D#_0

F2

H_D#_1

G8

H_D#_2

F8

H_D#_3

E6

H_D#_4

G2

H_D#_5

H6

H_D#_6

H2

H_D#_7

F6

H_D#_8

D4

H_D#_9

H3

H_D#_10

M9

H_D#_11

M11

H_D#_12

J1

H_D#_13

J2

H_D#_14

N12

H_D#_15

J6

H_D#_16

P2

H_D#_17

L2

H_D#_18

R2

H_D#_19

N9

H_D#_20

L6

H_D#_21

M5

H_D#_22

J3

H_D#_23

N2

H_D#_24

R1

H_D#_25

N5

H_D#_26

N6

H_D#_27

P13

H_D#_28

N8

H_D#_29

L7

H_D#_30

N10

H_D#_31

M3

H_D#_32

Y3

H_D#_33

AD14

H_D#_34

Y6

H_D#_35

Y10

H_D#_36

Y12

H_D#_37

Y14

H_D#_38

Y7

H_D#_39

W2

H_D#_40

AA8

H_D#_41

Y9

H_D#_42

AA13

H_D#_43

AA9

H_D#_44

AA11

H_D#_45

AD11

H_D#_46

AD10

H_D#_47

AD13

H_D#_48

AE12

H_D#_49

AE9

H_D#_50

AA2

H_D#_51

AD8

H_D#_52

AA3

H_D#_53

AD3

H_D#_54

AD7

H_D#_55

AE14

H_D#_56

AF3

H_D#_57

AC1

H_D#_58

AE3

H_D#_59

AC3

H_D#_60

AE11

H_D#_61

AE8

H_D#_62

AG2

H_D#_63

AD6

H_SWING

C5

H_RCOMP

E3

H_CPURST#

C12

H_CPUSLP#

E11

H_AVREF

A11

H_DVREF

B11

T18

T68

T19

RSVD CFG PM NC

CLKDMIGRAPHICS VIDMEMISC

DDR CLK/ CONTROL/ COMPENSATIONHDA

U4B

CANTIGA ES_FCBGA1329

SA_CK_0

AP24

SA_CK_1

AT21

SB_CK_0

AV24

SB_CK_1

AU20

SA_CK#_0

AR24

SA_CK#_1

AR21

SB_CK#_0

AU24

SB_CK#_1

AV20

SA_CKE_0

BC28

SA_CKE_1

AY28

SB_CKE_0

AY36

SB_CKE_1

BB36

SA_CS#_0

BA17

SA_CS#_1

AY16

SB_CS#_0

AV16

SB_CS#_1

AR13

SA_ODT_0

BD17

SA_ODT_1

AY17

SB_ODT_O

BF15

SB_ODT_1

AY13

SM_RCOMP

BG22

SM_RCOMP#

BH21

SM_RCOMP_VOH

BF28

SM_RCOMP_VOL

BH28

SM_VREF

AV42

SM_PWROK

AR36

SM_REXT

BF17

SM_DRAMRST#

BC36

DPLL_REF_CLK

B38

DPLL_REF_CLK#

A38

DPLL_REF_SSCLK

E41

DPLL_REF_SSCLK#

F41

PEG_CLK

F43

PEG_CLK#

E43

DMI_RXN_0

AE41

DMI_RXN_1

AE37

DMI_RXN_2

AE47

DMI_RXN_3

AH39

DMI_RXP_0

AE40

DMI_RXP_1

AE38

DMI_RXP_2

AE48

DMI_RXP_3

AH40

DMI_TXN_0

AE35

DMI_TXN_1

AE43

DMI_TXN_2

AE46

DMI_TXN_3

AH42

DMI_TXP_0

AD35

DMI_TXP_1

AE44

DMI_TXP_2

AF46

DMI_TXP_3

AH43

GFX_VID_0

B33

GFX_VID_1

B32

GFX_VID_2

G33

GFX_VID_3

F33

GFX_VID_4

E33

GFX_VR_EN

C34

CL_CLK

AH37

CL_DATA

AH36

CL_PWROK

AN36

CL_RST#

AJ35

CL_VREF

AH34

DDPC_CTRLCLK

N28

DDPC_CTRLDATA

M28

SDVO_CTRLCLK

G36

SDVO_CTRLDATA

E36

CLKREQ#

K36

ICH_SYNC#

H36

HDA_BCLK

B28

HDA_RST#

B30

HDA_SDI

B29

HDA_SDO

C29

HDA_SYNC

A28

RSVD1

M36

RSVD2

N36

RSVD3

R33

RSVD4

T33

RSVD5

AH9

RSVD6

AH10

RSVD7

AH12

RSVD8

AH13

RSVD9

K12

RSVD10

AL34

RSVD11

AK34

RSVD12

AN35

RSVD13

AM35

RSVD14

T24

RSVD15

B31

RSVD17

M1

RSVD20

AY21

RSVD22

BG23

RSVD23

BF23

RSVD24

BH18

CFG_0

T25

CFG_1

R25

CFG_2

P25

CFG_3

P20

CFG_4

P24

CFG_5

C25

CFG_6

N24

CFG_7

M24

CFG_8

E21

CFG_9

C23

CFG_10

C24

CFG_11

N21

CFG_12

P21

CFG_13

T21

CFG_14

R20

CFG_15

M20

CFG_16

L21

CFG_17

H21

CFG_18

P29

CFG_19

R28

CFG_20

T28

PM_SYNC#

R29

PM_DPRSTP#

B7

PM_EXT_TS#_0

N33

PM_EXT_TS#_1

P32

PWROK

AT40

RSTIN#

AT11

THERMTRIP#

T20

DPRSLPVR

R32

NC_1

BG48

NC_2

BF48

NC_3

BD48

NC_4

BC48

NC_5

BH47

NC_6

BG47

NC_7

BE47

NC_8

BH46

NC_9

BF46

NC_10

BG45

NC_11

BH44

NC_12

BH43

NC_13

BH6

NC_14

BH5

NC_15

BG4

NC_16

BH3

NC_17

BF3

NC_18

BH2

NC_19

BG2

NC_20

BE2

NC_21

BG1

NC_22

BF1

NC_23

BD1

NC_24

BC1

NC_25

F1

RSVD16

B2

RSVD25

BF18

NC_26

A47

TSATN#

B12

R82

10K_0402_5%~D

12

T33

C181

0.1U_0402_16V7K~D

1

2

T17

T28

T74

T65

R83

10K_0402_5%~D

12

T48

T26

T20

T9

R100

1K_0402_1%

12

R523 100_0402_5%~D

1 2

T36

C121

0.1U_0402_16V7K~D

1

2

C386

0.1U_0402_16V7K~D

1

2

T184

T24

T66

T39

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功