高速PCB电源走线优化:噪声与压降解决方案

下载需积分: 10 | DOC格式 | 80KB |

更新于2024-10-08

| 77 浏览量 | 举报

"本文深入探讨了高速PCB(印刷电路板)上的电源走线问题,重点关注了由于高频信号干扰和走线宽度减小导致的电源噪声和压降。文章提出了一种高速PCB的电源模型,并提供了几种解决方案,包括采用电源总线网络布线、选择适当的滤波电容以及模拟与数字地的分离,以应对高速PCB设计中的噪声和压降挑战。"

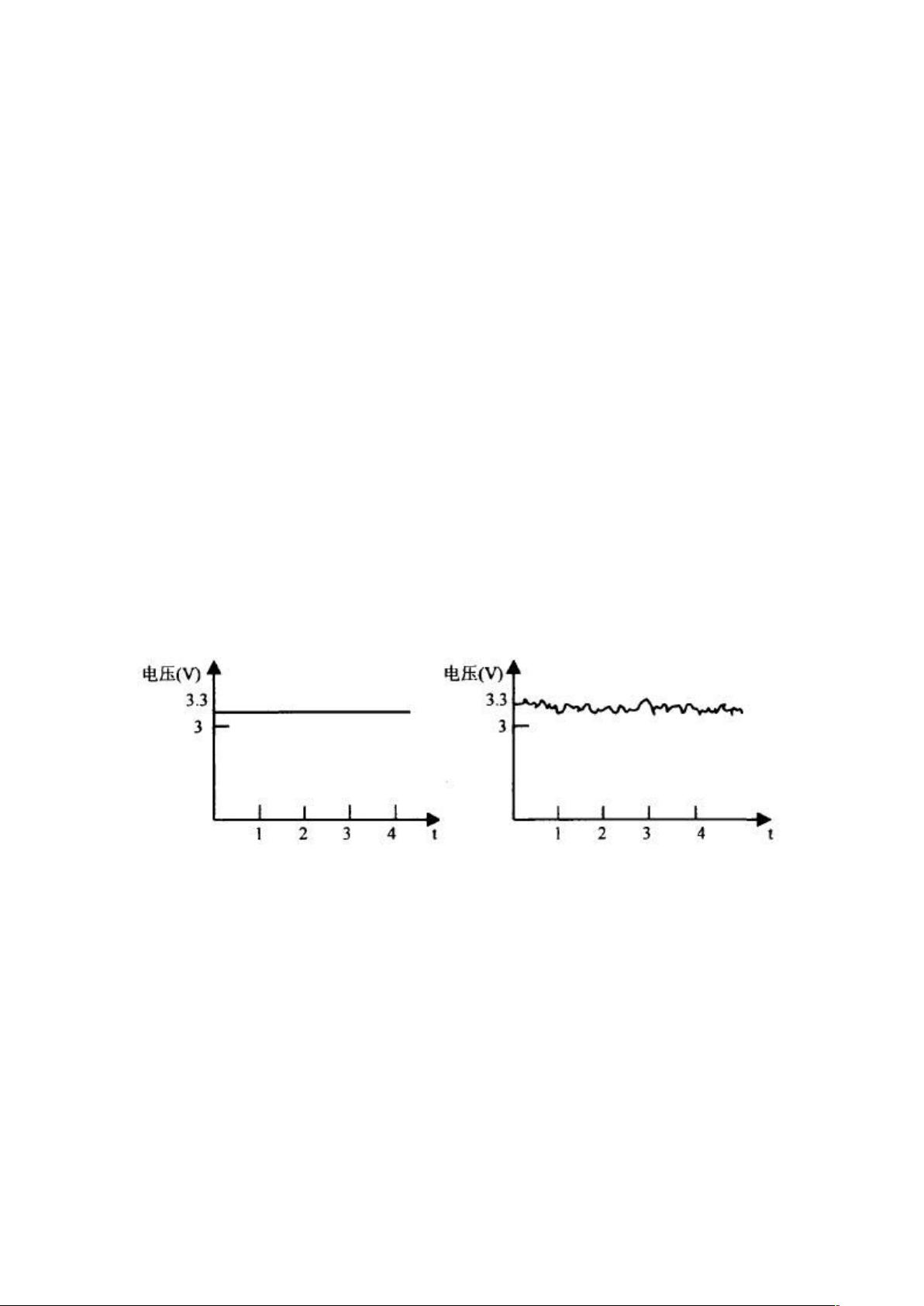

在高速PCB设计中,电源走线的优化至关重要。传统的电源模型通常假设电源无内阻且无寄生阻抗,但在实际应用中,特别是在高频环境下,电源会受到电场和磁场相互作用的影响,导致噪声的产生。此外,细小的走线会增加线路阻抗,从而引起远离电源的元件电压下降。因此,高速PCB设计的两大关键问题便是电源噪声和压降。

为了解决这些问题,文章提出了电源总线技术,这是一种将所有元器件连接到宽电源线上的方法,以减少压降并降低噪声。虽然这种方法并不能完全消除问题,但它在成本和复杂性之间找到了一个平衡点,相对于使用单独的电源层,电源总线技术更受设计师青睐。通过增大电源线的宽度,可以有效地减轻压降,但噪声仍然存在。

此外,文章还提到了改进型电源总线的设计,这种设计可能包含额外的滤波电容配置,以进一步减少噪声。滤波电容的选择至关重要,因为它能帮助稳定电源电压,吸收高频噪声,保持电路的稳定运行。同时,模拟地和数字地的分开也是关键,因为这可以避免不同类型的信号互相干扰,提升系统的整体性能。

高速PCB上的电源走线设计是一项复杂且精细的任务,涉及到电源模型的建立、电源总线的布局、滤波电容的选用以及地平面的分割策略。设计师必须全面考虑这些因素,以确保PCB在高频操作下的稳定性和可靠性。通过本文的分析和建议,读者可以获得关于如何处理高速PCB电源走线问题的宝贵见解,从而提高电子设备的性能和稳定性。

相关推荐

2021-09-24 上传

431 浏览量

1048 浏览量

111 浏览量

190 浏览量

298 浏览量

1080 浏览量

132 浏览量

554 浏览量

gggggggggesvxz

- 粉丝: 17

最新资源

- HTML技术在 CPS课程中的应用研究

- 循环流程关系图PPT模板下载指南

- 快速搭建企业级Vue应用:antd-vue-pcms初始化指南

- Carlos Salvo个人网站:从零开始构建指南

- Stm32L4温度湿度传感器接口项目实现

- Android开源一键清理项目:全面优化加速与管理

- 掌握Kubernetes基础:实践培训课程解析

- BlockRice.crx插件:屏蔽禁食名单中的OpenRice餐厅

- Bootstrap框架打造的响应式个人作品集网站

- 职场白领PPT素材模板下载:26张高清背景图

- 学习bash与python,寻求内容创作合作

- Vue项目奖励教程:从设置到编译和自定义配置

- 智能设备开发指南:Gulp模板Liga AK的快速入门

- NodeJS中使用JWT进行身份验证的API示例

- 中国海洋大学2020年856高等代数考研真题解析

- JavaScript食谱后端项目开发实践指南