Xilinx高端FPGA PCIE3.0 IP支持与选型分析

“Xilinx高端FPGAPCIE3.0IP分析”

Xilinx是一家领先的FPGA(现场可编程门阵列)制造商,其产品广泛应用于人工智能、大数据等高速通信领域。随着PCIE(Peripheral Component Interconnect Express)技术的快速发展,特别是PCIE 3.0及4.0标准的推出,对支持这些标准的FPGA器件的需求也在增加。然而,并非所有Xilinx FPGA系列都支持最新的PCIE版本,尤其是在高端产品如Ultrascale+、Ultrascale和Virtex7系列中。

1. PCIE支持情况

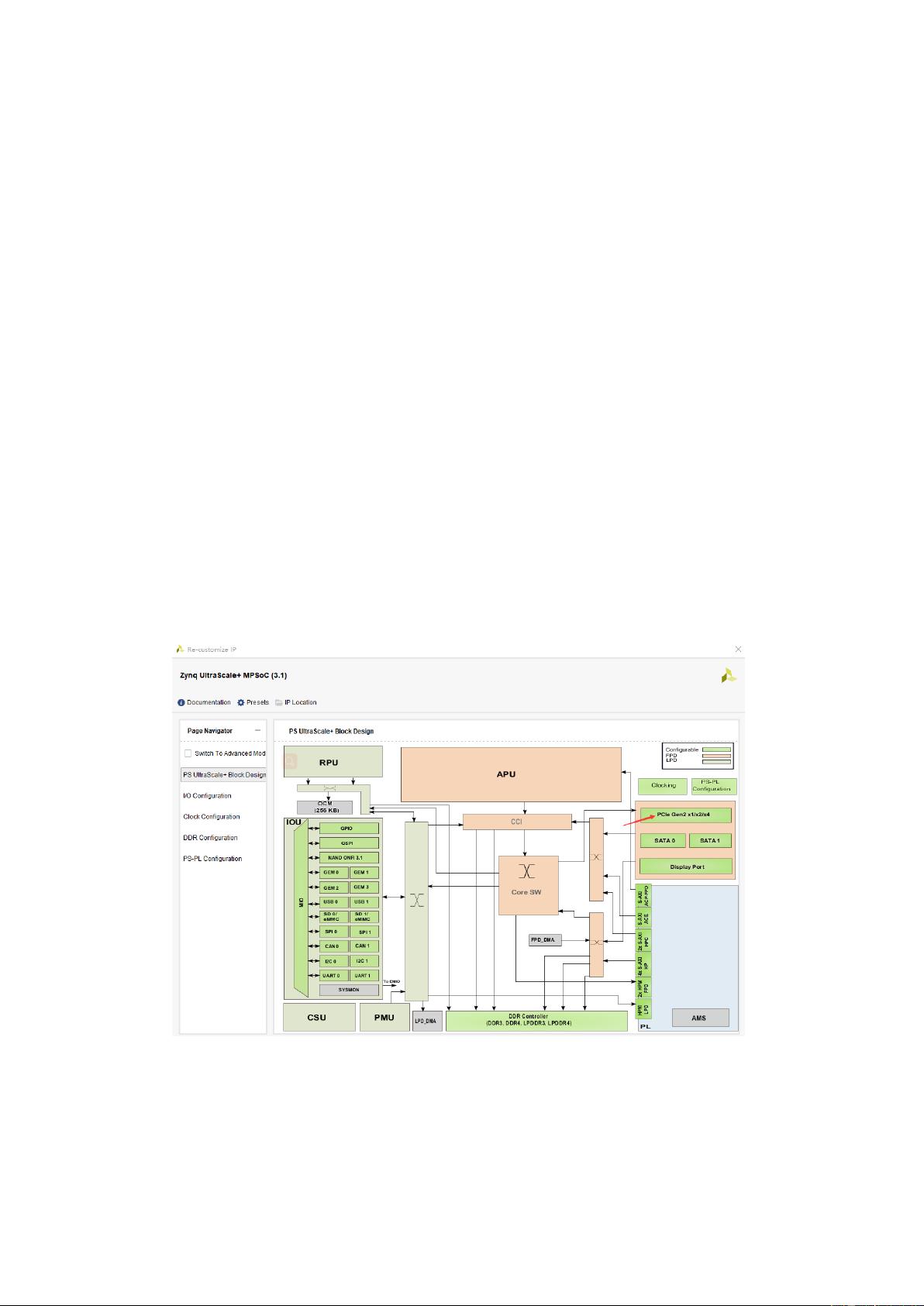

Xilinx在高端FPGA中为PCIE提供了不同级别的支持。例如,Zynq系列的FPGA通常内置硬核PCIE 2.0 x4 IP,而在拥有高性能计算单元(HBC)的FPGA中,可能会集成PCIE 3.0 x4的硬核。这些硬核IP允许开发者快速接入ARM处理器系统,简化软件开发流程。如果需要更高级别的配置,比如将PCIE设备设置为Root Complex模式,需要在配置界面启用“Switch To Advanced Mode”。

2. IP产品分析

- **7Series Integrated Block**:该IP适用于Ultrascale和Virtex-7系列,提供AXI-Stream接口,涵盖了PCIE的数据链路层、物理层和高速串行收发器功能。它更适合于需要高度定制化开发的硬件工程师。

- **AXI Bridge for PCI Express Gen3**:这个IP仅支持UltraScale和Virtex-7,能够达到GEN3 x16的速度等级,具备AXI-Bridge功能,便于集成到AXI总线的系统中,方便软件开发者使用。

- **DMA/Bridge Subsystem for PCI Express core**:专为UltraScale+系列设计,兼容AXI Bridge功能,支持更高的传输速率,但仅限于这一特定系列的FPGA。

在选择适合的Xilinx FPGA器件时,设计者需要根据项目需求考虑PCIE的速度等级、灵活性和与系统其余部分的集成难易程度。对于需要高吞吐量和低延迟的应用,可能需要选择支持PCIE 3.0或4.0的器件,并结合适当的IP来构建高效的系统架构。此外,了解每个IP核的特性、接口和兼容性是成功设计的关键,设计者应参考官方文档(如UG194)来获取详细信息。

Xilinx为不同层次的开发者提供了多样化的PCIE解决方案,使得开发者能够在满足性能需求的同时,兼顾成本和设计复杂性。对于高端FPGA用户来说,理解这些IP的特点和限制至关重要,以便做出最佳的器件选型和系统设计决策。

点击了解资源详情

129 浏览量

300 浏览量

300 浏览量

1861 浏览量

115 浏览量

116 浏览量

804 浏览量

112 浏览量

weixin_42401637

- 粉丝: 1

- 资源: 2

最新资源

- Meets:具有AI集成的下一代社交计划应用程序。 华盛顿大学202021冬季编码训练营最佳UX和UI设计奖以及“人民选择奖”

- katie

- Macrobond:Macrobond API的非官方熊猫包装

- Django-2.0.13.tar.gz

- pdf_converter

- Drawing:代码使草图软件中的手指绘图应用程序

- ec2recovery

- 转换tfrecord代码.zip

- qbaka-angular:Qbaka 的 Angular 插件

- Jukebox:TERA工具箱模块,可让您使用便携式自动点唱机在任何地方收听一些很棒的音乐!

- Android仿微信摇骰子游戏

- Oh Remind Me!-crx插件

- IBM x3650 m2网卡驱动32位 for win2003/2008 32位

- 控制任何外部IE内核浏览器-易语言

- ratings-api:在Redis上构建评级API的简单实现示例

- System-programming