FPGA验证入门指南:SystemVerilog、UVM与Questasim详解

需积分: 16 71 浏览量

更新于2024-07-22

5

收藏 1.7MB PDF 举报

本文是一篇关于FPGA验证的入门指南,作者分享了自己在2013年至2014年期间的经验和学习心得。主要内容涵盖了四个关键领域:

1. **SystemVerilog (SV)**: 作为硬件描述语言,SystemVerilog是FPGA验证中的重要工具。它用于描述设计的行为和结构,支持高级建模和验证。文章中提到,虽然讲解较为基础,但读者可以借此了解SV的基础知识,进一步学习时需要参考如《SystemVerilog与功能验证》等深入教材。

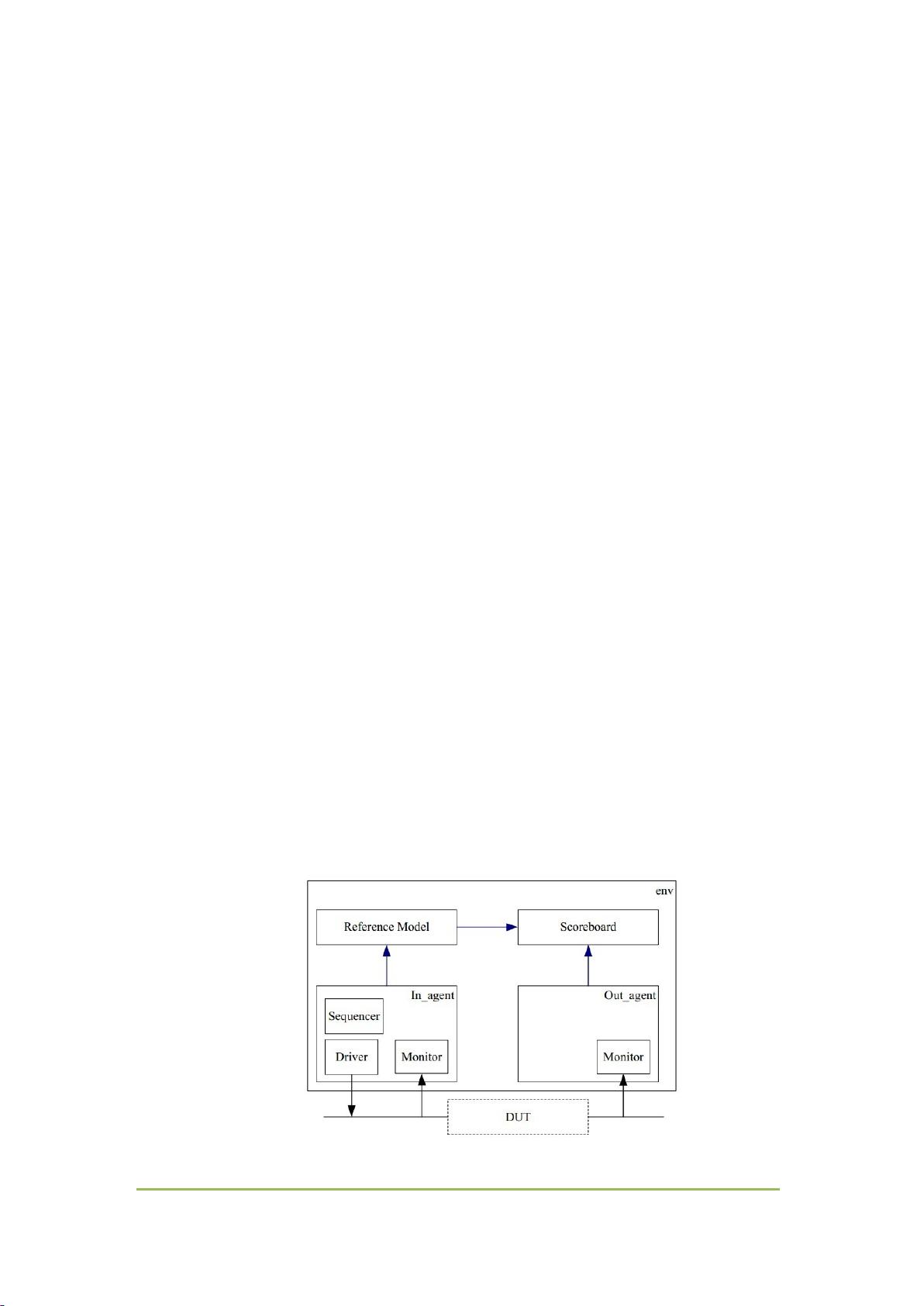

2. **Universal Verification Methodology (UVM)**: UVM是一种通用的验证方法论,为FPGA验证提供了结构化和可重复的方法。文章建议参考《UVM1.1应用指南及源码分析》和《UVM_CookBook_2013》,以便掌握UVM的基本框架,包括测试环境、接口层、 sequencer、 Coverage和分析模块等。

3. **Questasim 软件**: 作为FPGA开发和验证的常用工具,Questasim软件在文中被提及。它支持SystemVerilog设计和验证,文章强调了使用Questasim进行设计流程和批处理脚本的基础应用。

4. **验证项目流程**: 文章提到了验证项目的总体流程,这包括设计验证计划、编写测试bench、设置覆盖率目标、执行测试、分析结果和调试等步骤。这些是初学者理解FPGA验证的关键环节。

对于初次接触FPGA验证的人来说,本文旨在提供一个概览,通过阅读可以建立基本的概念框架。然而,由于内容较为泛泛,读者需要结合网络上的其他专业资料,如UVM和SV的官方文档以及书籍,进行深化学习。同时,作者也鼓励读者在遇到问题时积极寻求帮助,如联系guolehaohao@163.com。

文章还表达了作者对导师、项目组成员、北京大学实验室以及同事们的感激之情,他们的支持和指导对于作者的成长至关重要。本文是一份实用的FPGA验证入门教程,适合想要进入该领域的学习者参考和实践。

2021-07-13 上传

2021-07-13 上传

2021-09-25 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

haohao

- 粉丝: 5

- 资源: 37

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录