"2020数字逻辑实验报告模板1-实验方案设计:系列二进制加法器的设计与仿真"

需积分: 0 174 浏览量

更新于2023-12-30

收藏 1.02MB PDF 举报

实验方案设计如下:

实验名称:系列二进制加法器设计

实验目的:

- 采用传统电路的设计方法,设计四种二进制加法器(含封装)

- 利用Logisim软件的仿真功能来检查电路设计是否达到要求

- 培养学生传统逻辑电路设计、仿真和调试的能力

实验所用设备:

- Logisim 2.7.1 软件 1 套

- 微型计算机 1 台

课时安排:

- 课内:4 个课时

- 课外:4 个课时

实验内容:

实验要求学生设计电路并使用Logisim软件进行仿真。除逻辑门和触发器外,不能直接使用Logisim软件提供的其他逻辑组件库元件。

具体内容如下:

1. 一位二进制半加器:

设计一个一位二进制半加器,电路有两个输入A、B和两个输出S和C。

- 输入A和B分别为被加数和加数

- 输出S和C分别为本位和和向高位的进位信号

2. 一位二进制全加器:

设计一个一位二进制全加器,电路有三个输入A、B和Ci,两个输出S和Co。

- 输入A、B和Ci分别为被加数、加数和来自低位的进位

- 输出S和Co分别为本位和和向高位的进位信号

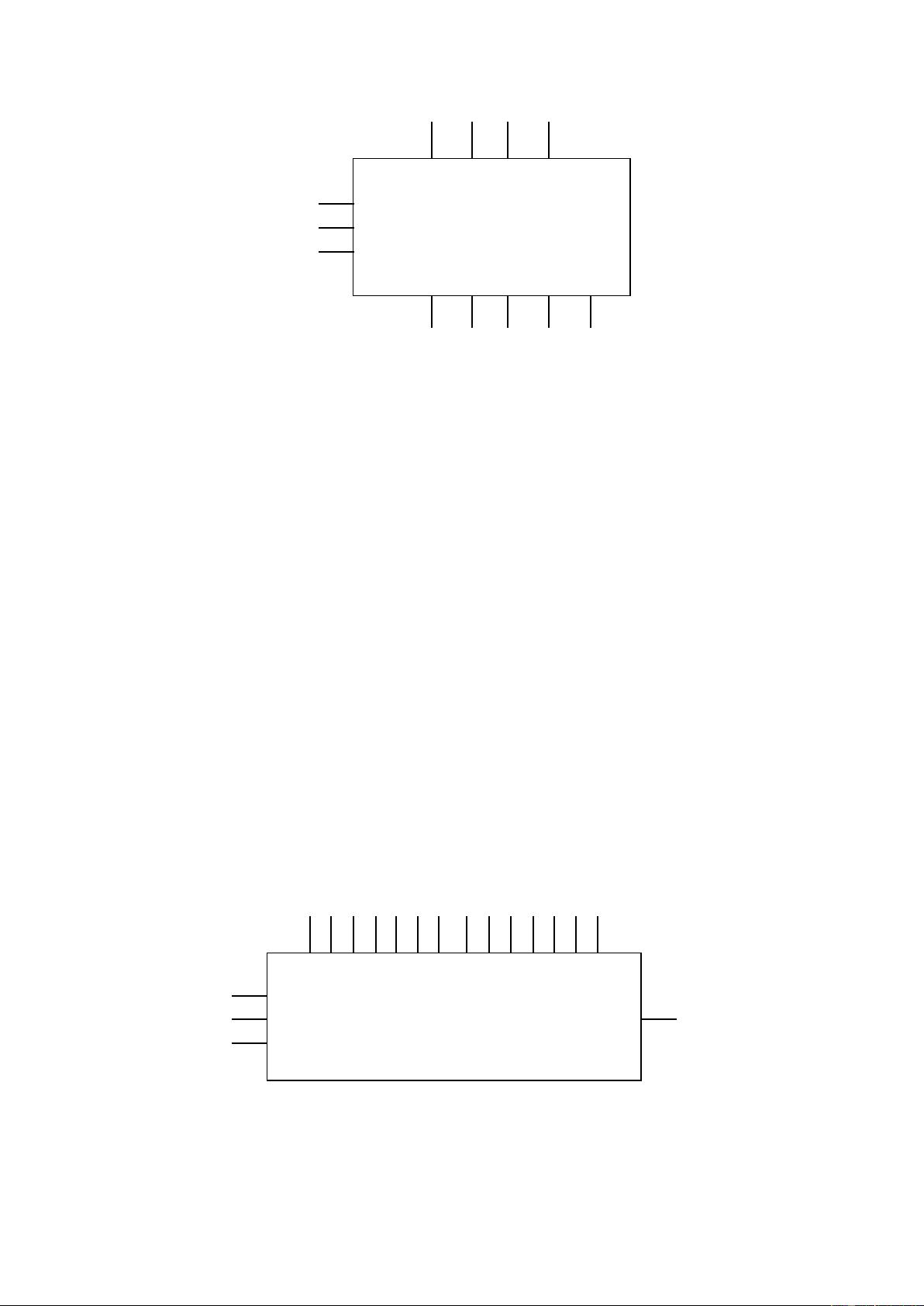

3. 四位二进制加法器:

设计一个四位二进制加法器,电路有八个输入A0~A3和B0~B3,及两个输出S0~S3和C4。

- 输入A0~A3和B0~B3分别为被加数和加数的四个位

- 输出S0~S3为和的四个位,C4为向高位的进位信号

4. 八位二进制加法器:

设计一个八位二进制加法器,电路有十六个输入A0~A7和B0~B7,及两个输出S0~S7和C8。

- 输入A0~A7和B0~B7分别为被加数和加数的八个位

- 输出S0~S7为和的八个位,C8为向高位的进位信号

通过以上实验的设计、仿真和验证等训练过程,学生将能够掌握传统逻辑电路的设计、仿真和调试的方法,并提升他们的电路设计能力和逻辑思维能力。同时,通过使用Logisim软件进行仿真,学生还能够更加直观地了解电路的运行原理和信号传输过程,提高他们的实践能力和问题解决能力。实验结果将被用于评估学生的实验能力和独立思考能力,确保他们对数字电路和逻辑设计的理解和应用。

2022-08-08 上传

130 浏览量

2022-08-08 上传

207 浏览量

2022-08-08 上传

2022-08-08 上传

2021-11-08 上传

2022-08-08 上传

嗨了伐得了

- 粉丝: 26

最新资源

- 自动生成CAD模型文件的测试流程

- 掌握JavaScript中的while循环语句

- 宜科高分辨率编码器产品手册解析

- 探索3CDaemon:FTP与TFTP的高效传输解决方案

- 高效文件对比系统:快速定位文件差异

- JavaScript密码生成器的设计与实现

- 比特彗星1.45稳定版发布:低资源占用的BT下载工具

- OpenGL光源与材质实现教程

- Tablesorter 2.0:增强表格用户体验的分页与内容筛选插件

- 设计开发者的色值图谱指南

- UYA-Grupo_8研讨会:在DCU上的培训

- 新唐NUC100芯片下载程序源代码发布

- 厂家惠新版QQ空间访客提取器v1.5发布:轻松获取访客数据

- 《Windows核心编程(第五版)》配套源码解析

- RAIDReconstructor:阵列重组与数据恢复专家

- Amargos项目网站构建与开发指南