数字电子技术作业解析:逻辑门电路与触发器

版权申诉

150 浏览量

更新于2024-09-10

收藏 412KB DOCX 举报

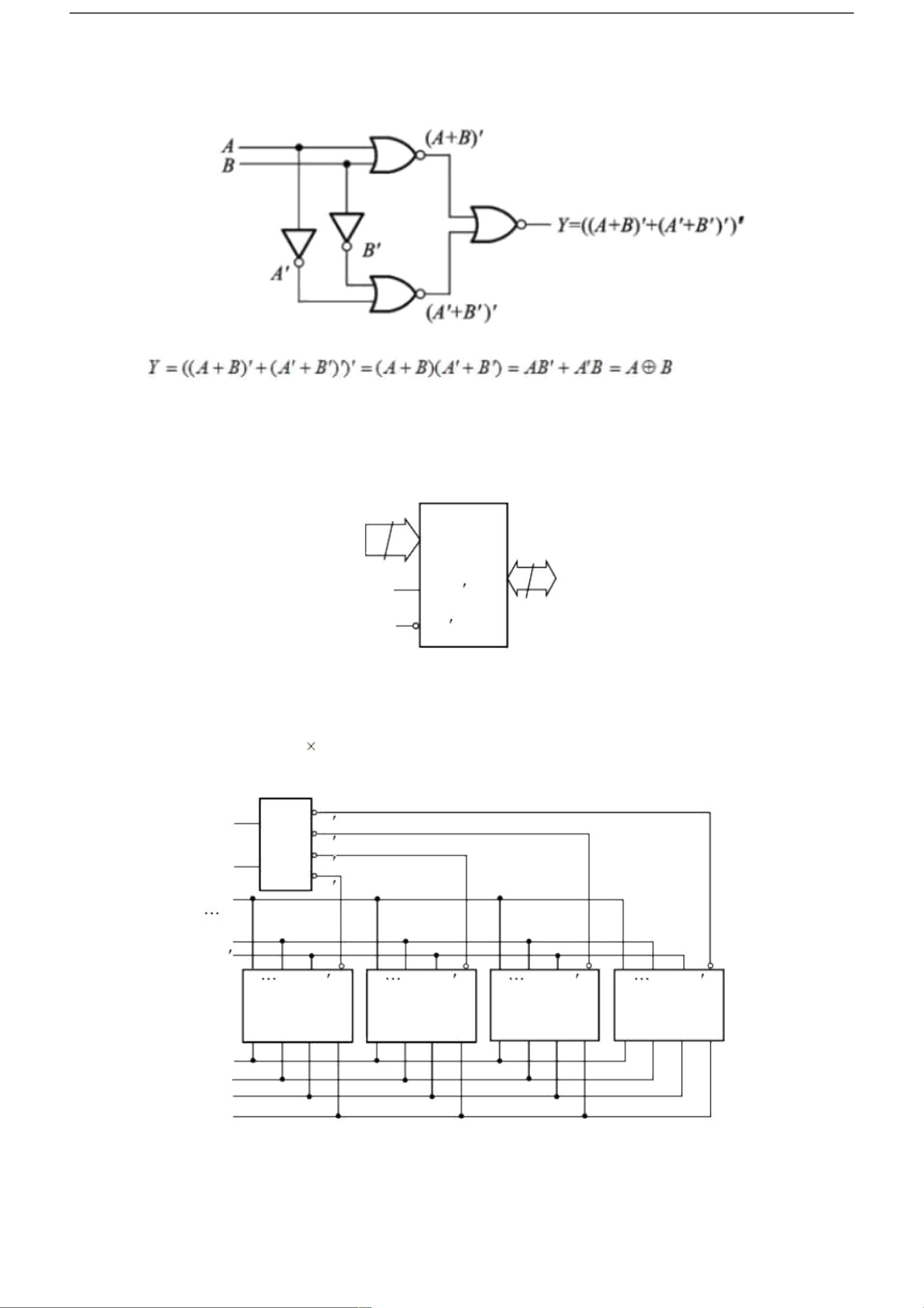

"华工网络2019下‘数字电子技术’作业包含了五个大题,共计16个小问题,涵盖了数字电路中的多个核心概念,包括三态门、触发器、存储器、数字模拟转换器(D/A)以及模拟数字转换器(A/D)等知识点。"

在数字电子技术中,三态门是一种特殊的门电路,它有第三个状态——高阻抗状态。在题目中,当控制信号EN为0时,三态与非门的Y1输出(AB)',Y2呈现高阻抗状态;当EN为1时,Y1变为高阻抗,Y2输出(CD)',整体输出Y与Y2相同,即为(CD)'。这种特性使得三态门可以在多路复用系统中,控制信号允许某一路信号通过而阻止其他路。

图2-2中未给出具体电路,但根据描述,需要分析的是EN信号对门电路类型及输出Y1、Y2、Y的影响,这通常涉及到三态门或类似电路的工作原理。

图2-3展示的电路是一个触发器,其输入D表达式为D=A异或Q,表明这是一个T触发器,因为Q的下一个状态Q(n+1)取决于当前状态Q(n)和输入D的异或结果。当CLK上升沿到来时,触发器状态更新,即为上升沿触发。

2114存储器的逻辑符号提示它是RAM(随机存取存储器),地址线由A9到A0共10根,数据线为4根,因此其容量为2^10=1024字节,每个字节包含4位,总共有4096位。

数字模拟转换器(D/A转换器)用于将数字信号转换为模拟信号,而模拟数字转换器(A/D转换器)则执行相反的过程。在第8题中,为了将最大幅值为5.1V的模拟信号转换为数字信号,每变化20mV就需要数字信号的最低位发生变化,计算得出需要至少8位的A/D转换器,因为255(即2^8-1)能提供足够的分辨率覆盖这个范围。转换器的分辨率是指最小可检测的模拟信号变化,这里是20mV。

在组合逻辑电路设计部分,例如全加器的设计,全加器是一个可以同时处理两个二进制位加法并考虑进位的逻辑电路。设计全加器需要完成以下步骤:

1) 列出真值表,包括输入A、B、C和进位输入CI,以及输出和CO的全部可能状态。

2) 写出输出S和CO的最小项之和表达式,这可以通过布尔代数简化得到。

3) 利用卡诺图进行化简,将S和CO的逻辑表达式转化为最简与或形式。

4) 分别得到S和CO的逻辑门电路实现,通常会包括与门、或门和非门的组合。

以上内容涉及了数字电子技术的基础知识,包括逻辑门电路、触发器、存储器、数模和模数转换器,以及组合逻辑电路设计。这些概念是理解和设计数字系统的关键要素。

2022-05-27 上传

2022-05-27 上传

2022-07-11 上传

m0_62183678

- 粉丝: 1

- 资源: 4万+

最新资源

- C++解析PDF文件的源码示例

- ClassStuffdotjpg:课堂博客

- choco-cpviz:Choco3的扩展以处理cpviz librairie

- 主要用于学习mysql.zip

- capstan:基于Apache Flink的项目

- InfInstall VC++ inf安装程序

- Jenkins-webapp

- 喵API

- jsCodeDemo:JavaScript 模拟实现前端常见函数,算法面试题

- dfs-proxy:杂草dfs代理

- lpnyc:学习 Python NYC 的 TDD(测试驱动演示)旨在成为一个元包,可以自动测试发现针对 Python 2 和 3 运行的单元测试

- 这是我在学习《php 和MySql Web 开发》过程中所写的代码.zip

- api-spec-modules:用于实现REST API的一组可重用的规范

- VC++ 6.0远程备份下载程序

- gxsd-android-tch_stu:高速速读_老师端和学生端

- guess-the-number