64

978-1-5090-4613-3/16/$31.00 ©2016 IEEE

Enhancement-mode Al

2

O

3

/InAlGaN/GaN MOS-HEMTs with a Record Drain Current Density of 1.7

A/mm and a Threshold Voltage of +1.5 V

Kai Zhang, Jianjun Zhou, Cen Kong, Yuechan Kong, and Tangsheng Chen

Science and Technology on Monolithic Integrated Circuits and Modules Laboratory,

Nanjing Electronic Devices Institute

NO. 524 Zhongshan East Road, Nanjing

haigui.34@163.com

Abstract

The paper reports high performance enhancement-mode

MOS-HEMT based on quaternary InAlGaN barrier. A self-

aligned gate technology is used for gate recessing, dielectric

deposition and gate electrode formation processes, where

improved digital recessing process as well as O

2

plasma-

assisted Al

2

O

3

gate dielectric is developed. Fabricated E-mode

MOS-HEMT delivers a record output current density of

1.7A/mm with a threshold voltage (V

TH

) of 1.5 V, and a small

on-resistance (R

on

) of 2.0 Ω·mm. Excellent V

TH

hysteresis and

greatly improved gate leakage characteristics are also

demonstrated.

1. Introduction

With their large bandgap, large breakdown field and high

electron velocity, group-III nitrides have been widely

explored as promising candidates for high-voltage power

switching. So far, based on AlGaN/GaN heterostructure,

various approaches such as gate recessing, p-type gate and

fluorine plasma treatment have been developed to convert the

inherent D-mode operation into the E-mode one. Gate recess

scheme achieves the normally-off operation by thinning the

barrier layer. With a proper depth control, “as-grown” channel

properties can be maintained, thus allowing a comparable on-

resistance with its normally-on counterpart. Nevertheless, the

degraded channel mobility is commonly observed, due to the

dry-etching damage. The gate recess technique has been much

improved by upgrading etching schemes with enhanced

controllability, such as O

2

-BCl

3

[1] or O

2

-HCl digital etching

[2].

Recently, InAlGaN or AlInN-based HEMTs have drawn

intensive attention for high-speed applications because of

higher two-dimentional electron gas (2DEG) density in the

channel induced by much stronger spontaneous polarization.

Similarly, the superior property can facilitate reducing the on-

resistance and thus power consumption, which is quite

desirable for power switching devices. To date, only a few

results about InAlN/GaN based E-mode devices have been

demonstrated [3]-[4].

In the work, we for the first time demonstrate the E-mode

quaternary barrier InAlGaN/GaN MOS-HEMTs combined

with an O

2

plasma-assisted Al

2

O

3

gate dielectric. A self-

aligned process was developed to avoid the damage to gate

dielectric in the process. High current driving capacity and

low on-resistance with a threshold voltage (V

TH

) of 1.5V were

shown.

2. Device and Process Description

The InAlGaN/GaN epilayer structure was grown on 3-in

SiC substrate by metal–organic chemical vapor deposition. It

consists of a 7-nm InAlGaN barrier, 1-nm AlN spacer, and a

1.2-μm-thick undoped GaN buffer layer. Hall measurements

yield a sheet concentration of 1.82×10

13

cm

-2

and a high

mobility of 1627 cm

2

/Vs, respectively, resulting in a sheet

resistance of 210 Ω/ □ . Device fabrication started with

source/drain ohmic contacts formed by Ti/Al/Ni/Au

metallization annealed at 840 ℃ for 30 s in N

2

ambient. Then,

the wafer was passivated with 60-nm Si

3

N

4

by plasma

enhanced chemical vapor deposition (PECVD) followed by

Ar

+

implantation isolation. After lithography definition of

footprint, Si

3

N

4

dielectric was selectively etched, and then the

exposed InAlGaN barrier was partially removed to shift the

threshold voltage. The gate recess process features 3-cylces

O

2

/BCl

3

plasma-based digital etching in combination with 1-

cycle O

2

plasma/HCl-based digital etching. Most of the

barrier removal was conducted by the BCl

3

-based digital

etching due to higher etching rate, while the last wet etching

cycle was utilized to reduce dry etching-induced damage.

Subsequently, a 12-nm Al

2

O

3

gate

dielectric was grown by

plasma-enhanced atomic-layer-deposition (PE-ALD) using

trimethylaluminum (TMA) and high-density O

2

plasma as

precursors at room temperature. The device process was

completed with Ni/Au/Ni metal deposition and liftoff. In our

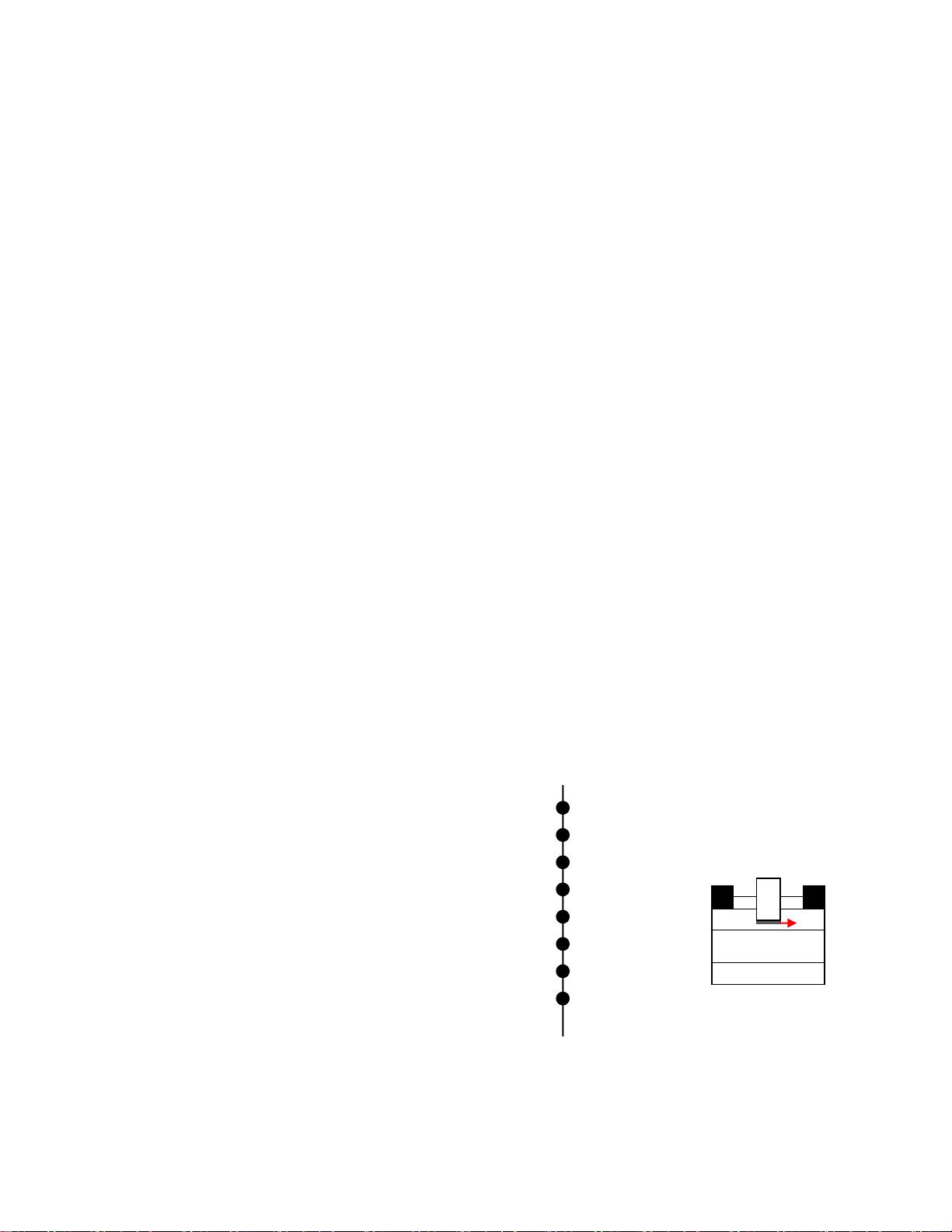

work, the above self-aligned gate process was developed (see

fig. 2.1), as we found that O

2

plasma-assisted Al

2

O

3

gate

dielectric was easily removed by the photoresist developer.

The devices investigated have a physical gate length (L

G

) of

1.0 μm, a gate-source distance of 1.5 μm, and a gate–drain

distance of 2.0 μm.

Fig. 2.1 Self-aligned fabrication process for E-mode

MOS-HEMTs

3. Results and Discussion

Al

2

O

3

has been considered to be one of the most

promising gate dielectrics for reducing the gate leakage

Ni/Au/Ni evaporation

and liftoff