MIPS流水线CPU设计与实现:武汉大学计算机学院实验报告

需积分: 0 103 浏览量

更新于2024-06-30

2

收藏 1.54MB DOCX 举报

"MIPS流水线CPU设计与实现1"

本实验报告详细介绍了张永康同学在武汉大学计算机科学与技术专业进行的计算机组成原理实验,其核心内容是设计并实现一个MIPS流水线CPU。实验旨在让学生深入理解现代处理器的工作原理,特别是MIPS指令集的特点、功能及其实现细节。

MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集计算机(RISC)架构,以其高效的流水线处理能力而闻名。在实验中,张永康同学首先设计了一个单周期MIPS处理器,然后进一步将其扩展为流水线MIPS处理器,以提高处理器的吞吐量和性能。

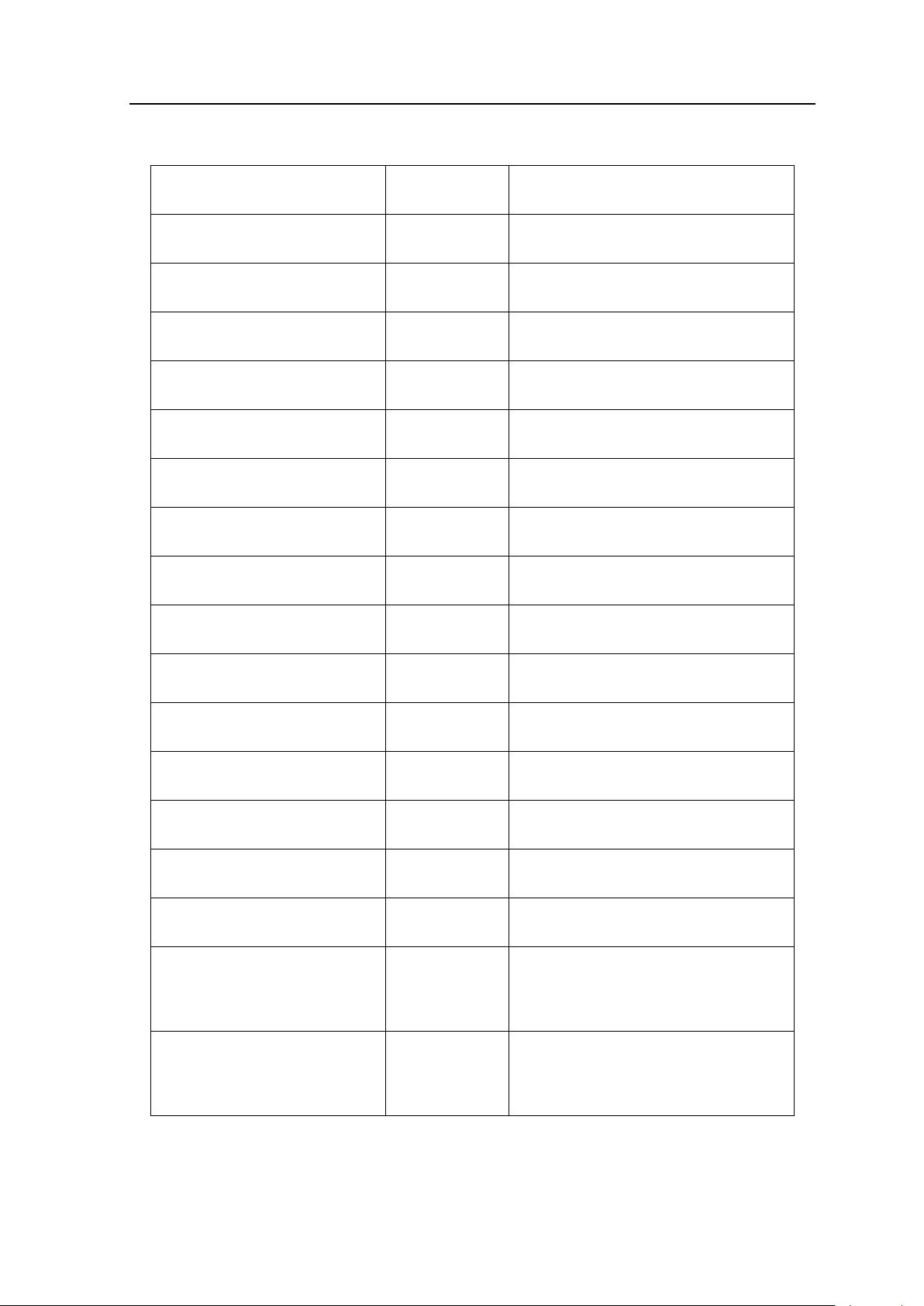

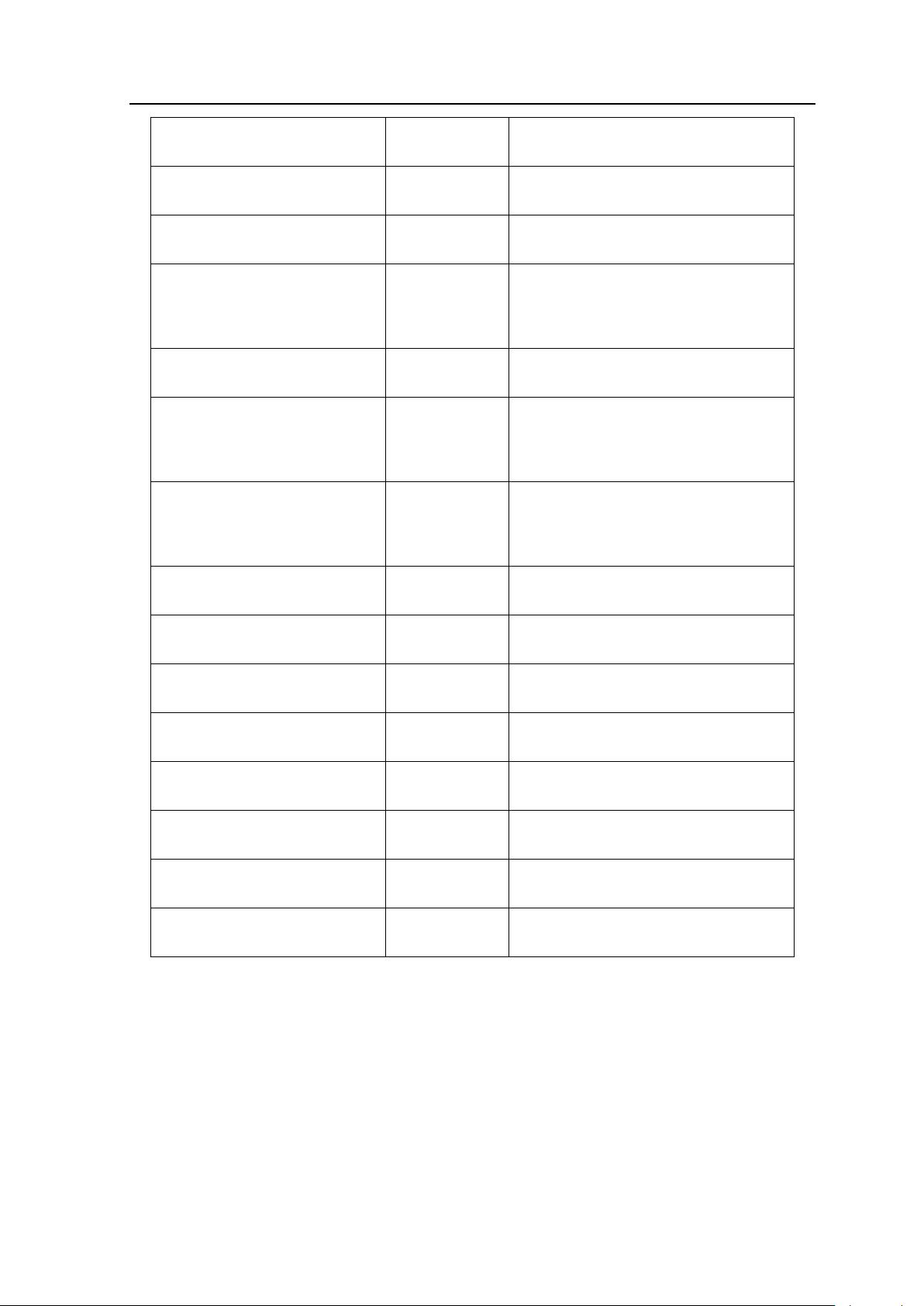

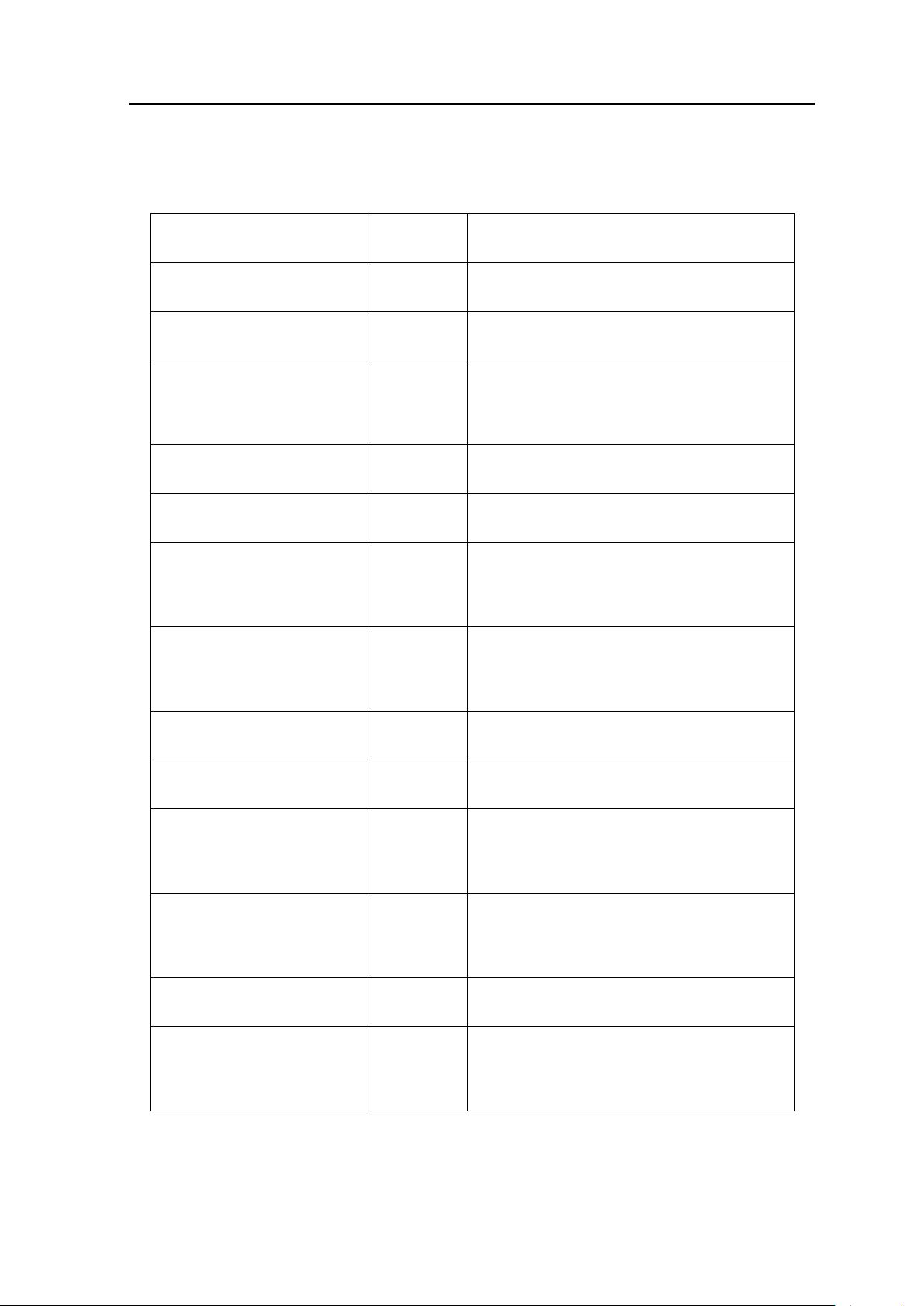

流水线技术是通过将指令执行过程划分为多个阶段(如取指(IF)、译码(ID)、执行(EX)、内存访问(MEM)和写回(WB)),使得每条指令在流水线的不同阶段同时进行,从而提高处理器效率。然而,流水线中存在数据相关性和控制冒险的问题。数据相关性指的是当一条指令的结果被后续指令使用时,可能出现的等待现象,通常分为RAW(Read After Write)、WAR(Write After Read)和WAW(Write After Write)三种类型。控制冒险则主要由分支指令引起,因为它可能改变指令的执行顺序。

在实验中,张永康同学采用了预测分支总不发生的方法来缓解控制冒险,即在ID级判断分支条件,提前决定是否需要阻塞流水线。同时,他还在ID级和EX级加入了全旁路电路来解决RAW类型的数据相关问题,确保数据的及时传递,避免延迟。

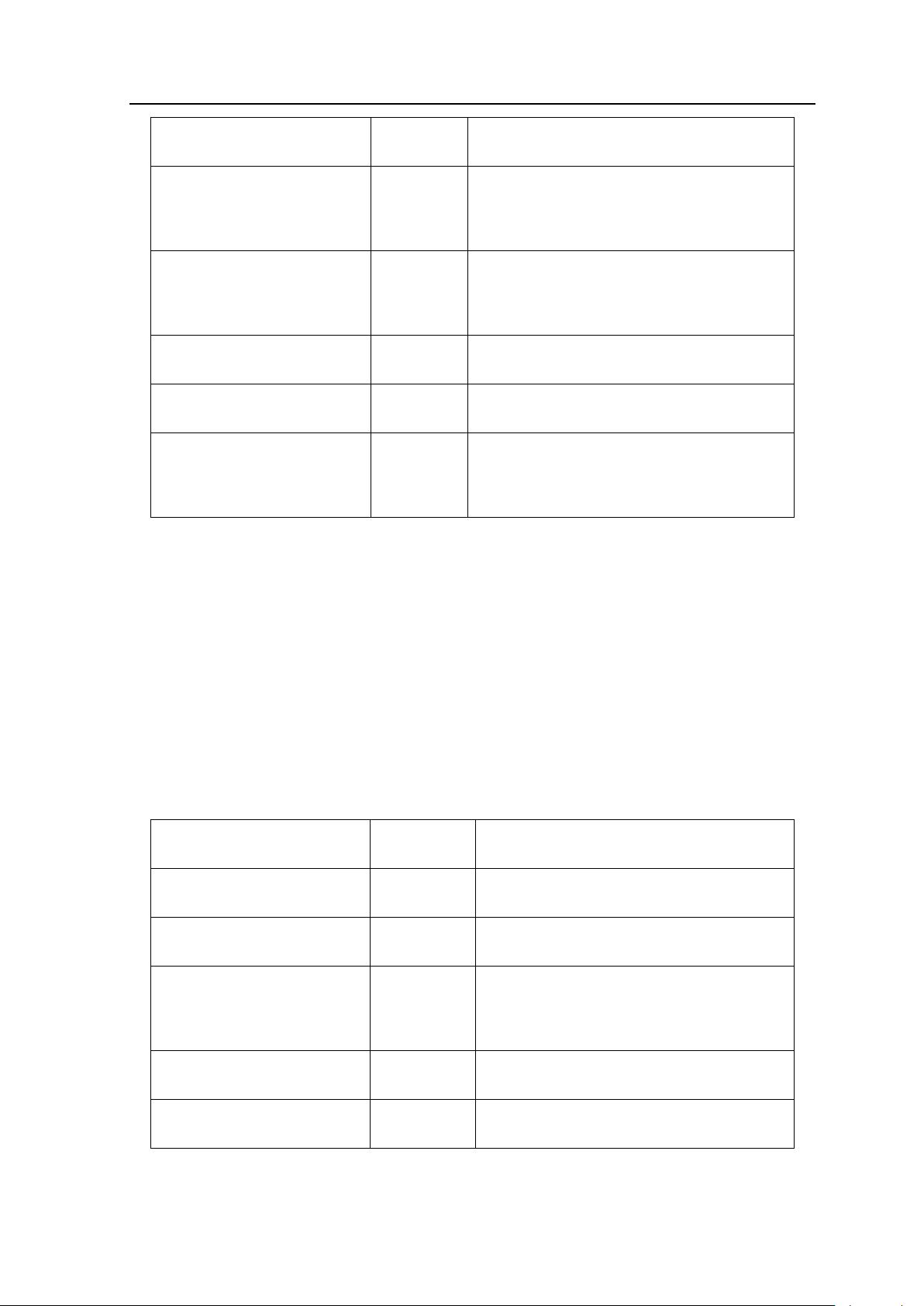

实验过程中,张永康使用了Verilog HDL进行硬件描述语言编程,这是一种广泛用于数字系统设计的语言。他还利用ModelSim进行功能仿真,该软件可以验证设计的正确性。此外,MARS软件则用于提供MIPS指令集的模拟运行环境,以对比和验证实验结果。

实验的最后阶段,设计的CPU模型被下载到FPGA(Field-Programmable Gate Array)开发板上进行实际测试,并成功执行了数组排序程序,其结果与MARS软件的预期结果一致,证明了设计的正确性和有效性。

关键词涉及到的核心概念包括:MIPS架构、处理器设计、流水线技术、分支预测、数据相关性解决方案、FPGA实现以及ModelSim和MARS工具的使用。这个实验不仅涵盖了理论知识,还锻炼了学生的实践能力和问题解决技巧,是计算机组成原理教学的重要组成部分。

2023-08-11 上传

2018-06-29 上传

2022-08-04 上传

2023-02-23 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

LauraKuang

- 粉丝: 22

- 资源: 334

最新资源

- 新代数控API接口实现CNC数据采集技术解析

- Java版Window任务管理器的设计与实现

- 响应式网页模板及前端源码合集:HTML、CSS、JS与H5

- 可爱贪吃蛇动画特效的Canvas实现教程

- 微信小程序婚礼邀请函教程

- SOCR UCLA WebGis修改:整合世界银行数据

- BUPT计网课程设计:实现具有中继转发功能的DNS服务器

- C# Winform记事本工具开发教程与功能介绍

- 移动端自适应H5网页模板与前端源码包

- Logadm日志管理工具:创建与删除日志条目的详细指南

- 双日记微信小程序开源项目-百度地图集成

- ThreeJS天空盒素材集锦 35+ 优质效果

- 百度地图Java源码深度解析:GoogleDapper中文翻译与应用

- Linux系统调查工具:BashScripts脚本集合

- Kubernetes v1.20 完整二进制安装指南与脚本

- 百度地图开发java源码-KSYMediaPlayerKit_Android库更新与使用说明

已收录资源合集

已收录资源合集