Quartus II 5.1实战:半加器设计与EDA流程解析

需积分: 24 17 浏览量

更新于2024-09-11

1

收藏 1.85MB DOC 举报

"半加器设计"

在数字电路设计中,半加器是一个基础且重要的组成部分,它用于执行二进制数的加法运算。半加器仅处理两位二进制数的加法,不考虑上一位的进位,因此得名"半加器"。这次实验主要目标是通过Quartus II 5.1软件设计平台,学习和掌握半加器的工作原理以及设计方法。

Quartus II是一款广泛使用的电子设计自动化(EDA)软件,适用于Altera FPGA和CPLD的开发。在5.1版本中,用户可以利用其图形用户界面(GUI)进行设计输入,这大大简化了数字逻辑电路的设计流程。实验过程中,首先需要启动Quartus II 5.1,然后创建新的工程,并为项目指定名称和保存路径。新建工程后,接着创建一个新的Block Diagram/Schematic File,这是用来绘制电路原理图的。

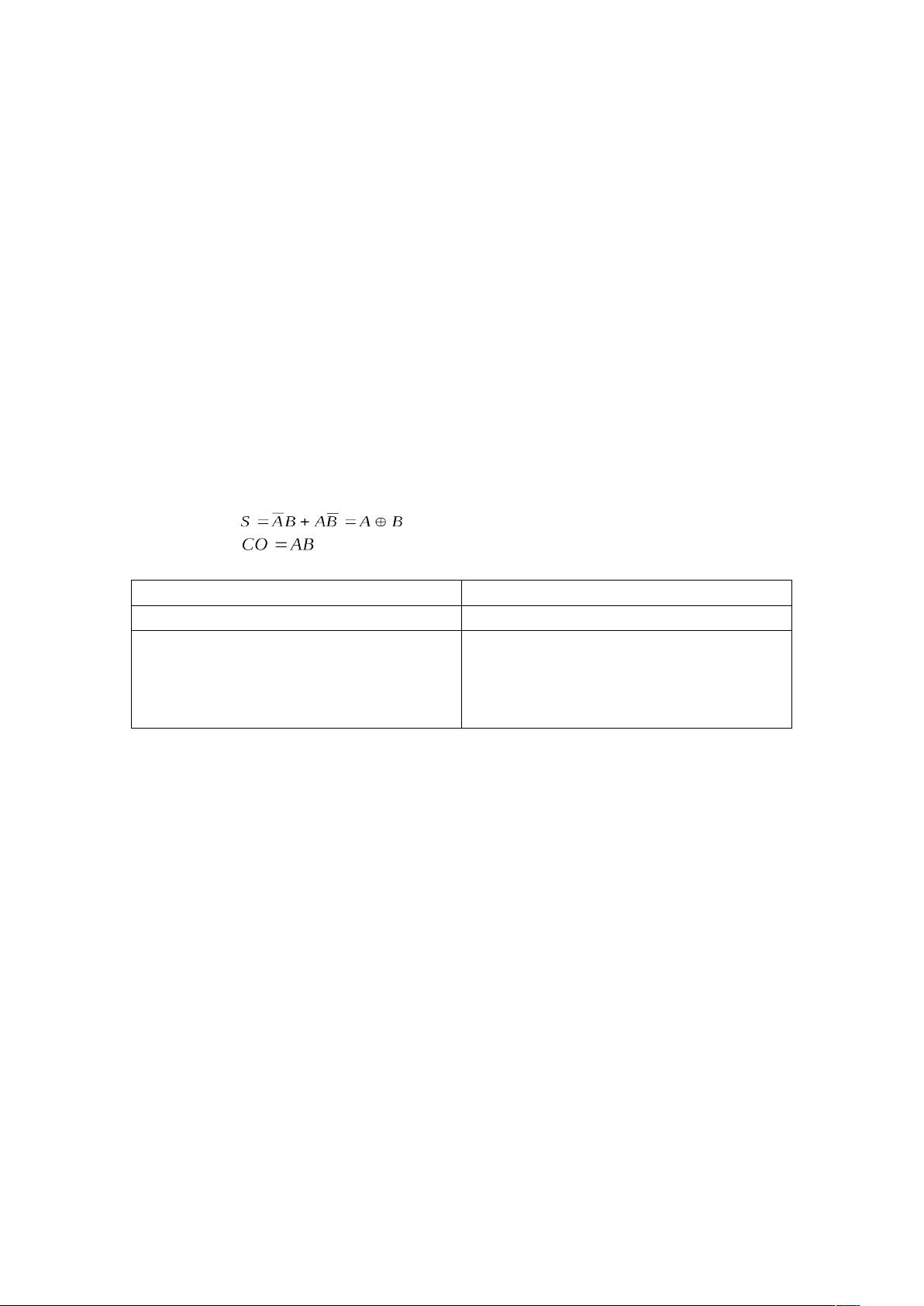

半加器的逻辑功能可以通过两个基本逻辑门——异或门和与门来实现。异或门负责计算两个输入A和B的异或结果,即无进位情况下的和S;而与门则计算两个输入的与操作,产生进位信号CO。根据二进制加法规则,半加器的真值表如下:

| 输入 | 输出 |

| ---- | ---- |

| A B | S CO |

| 0 0 | 0 0 |

| 0 1 | 1 0 |

| 1 0 | 1 0 |

| 1 1 | 0 1 |

从真值表可以看出,当A和B都为0时,和S为0,无进位(CO);当A和B不同时,S为1,无进位;只有当A和B都为1时,S为0,但会产生一个进位1。

在Quartus II中设计半加器,首先要放置所需的逻辑门符号。可以通过菜单栏的"Edit" -> "Insert Symbol"或者使用快捷键来添加异或门和与门。然后,将A和B输入连接到异或门,将A和B的与结果连接到与门,最后将异或门和与门的输出分别连接到S和CO,完成半加器的原理图设计。

设计完成后,保存文件并进行编译。Quartus II会分析设计,生成相应的逻辑等效电路,并给出逻辑仿真结果。通过仿真,可以验证设计是否正确实现了半加器的功能。如果一切正常,可以进一步进行综合和实现,将设计转化为实际的硬件描述语言(如VHDL或Verilog)代码,最后下载到FPGA或CPLD中进行硬件验证。

这个实验旨在通过Quartus II 5.1这个强大的工具,帮助学生理解和掌握半加器的设计,以及EDA设计流程,从而为更复杂的数字系统设计打下坚实的基础。

281 浏览量

265 浏览量

225 浏览量

点击了解资源详情

点击了解资源详情

sinat_28895827

- 粉丝: 0

- 资源: 1

最新资源

- vip会员统计表excel模版下载

- containerBooking

- like-me

- node-async-await-example:具有异步等待用法的Node.js应用程序的简单示例

- F460dll_for_TOT_KLS.rar

- NRRD 格式文件阅读器:NRRD 文件阅读器-matlab开发

- upptime:Up Upptime的正常运行时间监视器和状态页面,由@upptime提供支持

- 幼儿园财务报表excel模版下载

- Calculator:在Android Studio上使用Kotlin的基本计算器

- luckytuan-fast-loader-master.zip

- adc-analysis:SciCRT的跟踪分析

- SCANProject:堆叠式交叉注意项目页面

- 公司会议室3D模型

- pushNaNs:将 NaN 推送到 X 的每一列的底部。-matlab开发

- ManuelGil:个人资料

- 爱普生(Epson)L805 原版清零软件