计算机逻辑部件:布尔代数与逻辑门

下载需积分: 50 | PPT格式 | 1001KB |

更新于2024-07-25

| 12 浏览量 | 举报

"计算机逻辑部件主要涵盖了布尔代数基础、基本逻辑门的实现与表示、组合逻辑电路设计、时序逻辑电路设计以及阵列逻辑电路等内容。布尔代数是理解数字逻辑系统的基础,用于描述和分析逻辑关系。基本逻辑门包括与门、或门和非门,它们是所有逻辑电路的基础。组合逻辑电路和时序逻辑电路是数字系统设计中的关键部分,前者处理输入信号的即时组合,后者则涉及数据的存储和时间序列处理。阵列逻辑电路则提供了一种高效实现大规模逻辑功能的方法。"

布尔代数基础是计算机逻辑部件学习的起点,它由英国数学家乔治·布尔创立,主要用于处理二值逻辑系统,即只有真(1)和假(0)两种状态的逻辑变量。布尔代数的基本运算包括逻辑与(AND,表示为A·B或AB)、逻辑或(OR,表示为A+B)和逻辑非(NOT,表示为A'或/A)。这些运算符满足一系列定律,如0-1律、自等律、重叠律、互补律、交换律和结合律,这些定律在设计和分析逻辑电路时至关重要。

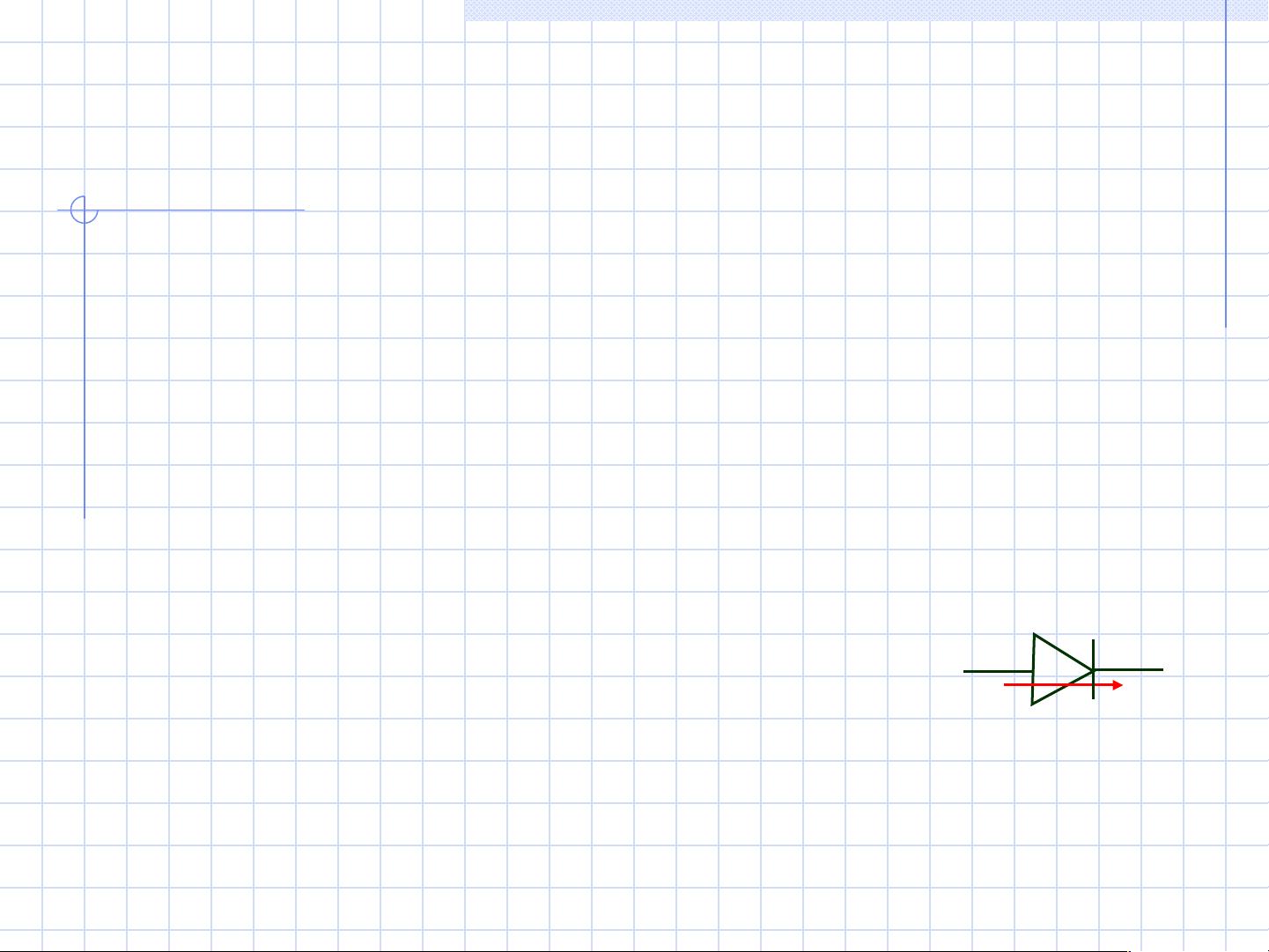

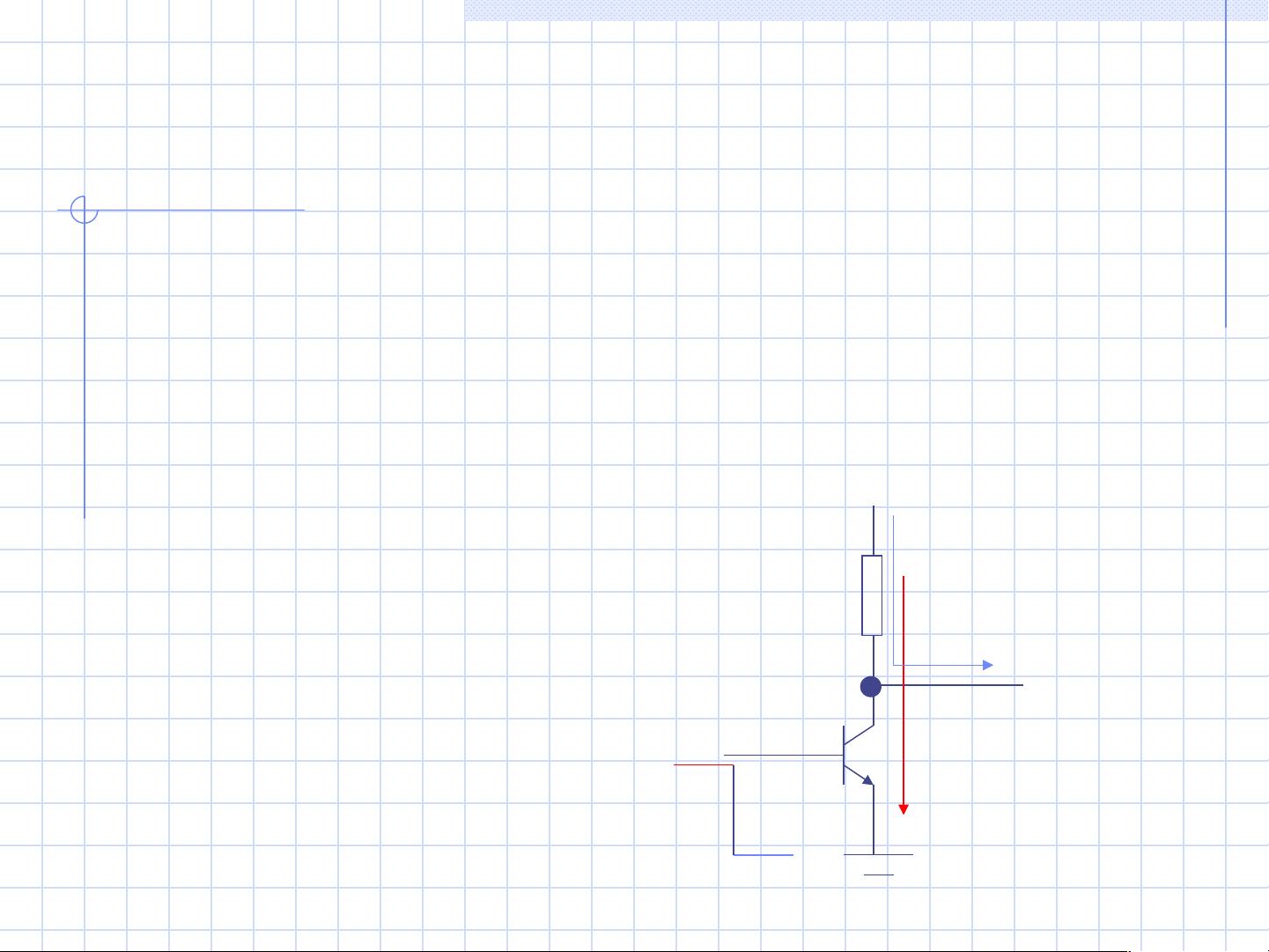

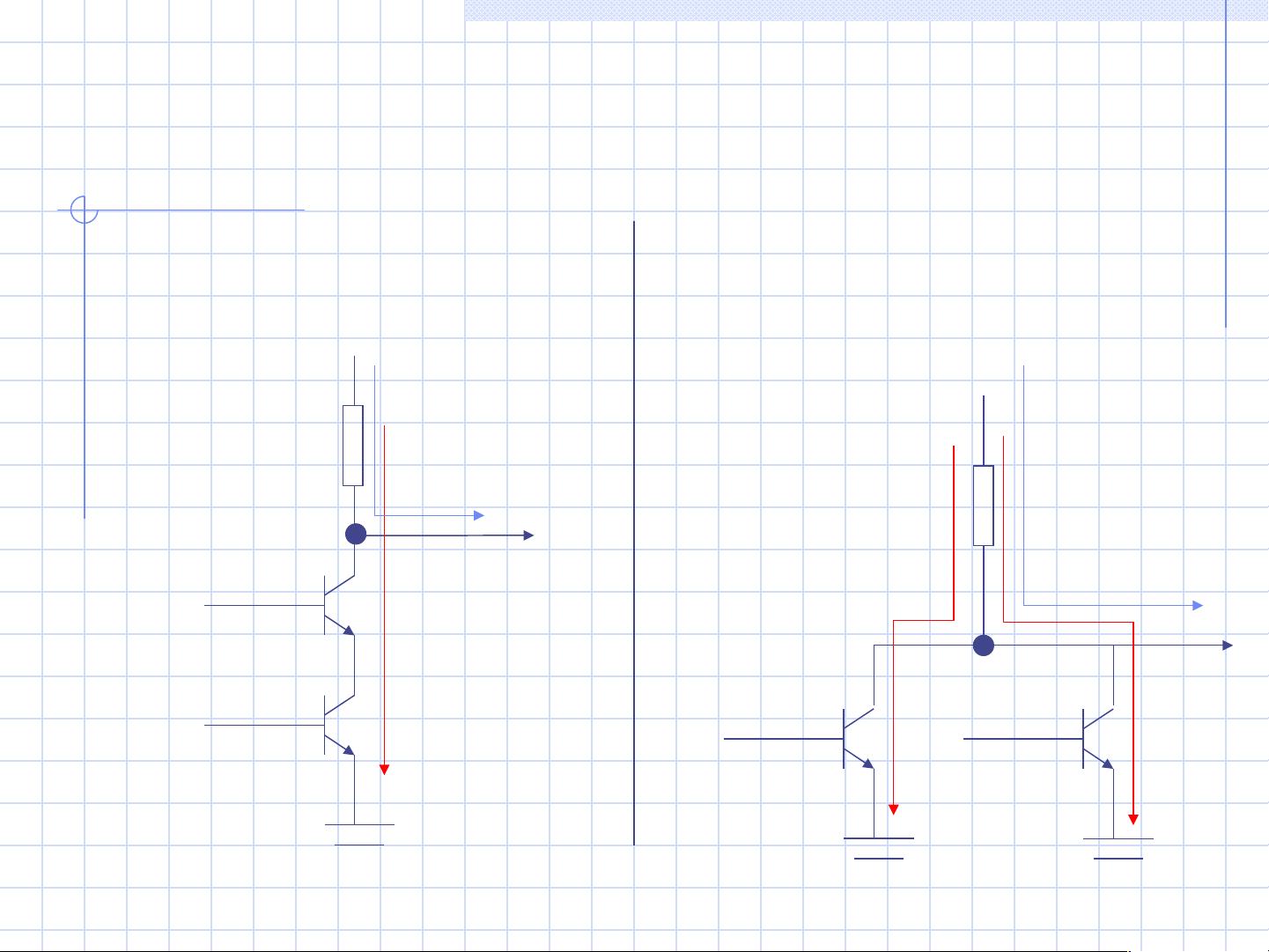

基本逻辑门是实现布尔运算的物理组件。与门执行逻辑乘法,只有当所有输入都为1时,输出才为1;或门执行逻辑加法,只要至少有一个输入为1,输出就为1;非门则反转输入的逻辑状态。除了这些基本门,还有其他复合逻辑门,如与非门(NAND)、或非门(NOR)、与或非门(XNOR)和异或门(XOR),它们通过组合基本门来实现更复杂的逻辑功能。

组合逻辑电路设计涉及到根据特定逻辑需求,利用基本逻辑门构建电路的过程。这通常包括分析逻辑表达式,简化表达式以减少门的数量和延迟,然后将简化后的表达式映射到实际的逻辑门网络。例如,使用卡诺图或布尔代数定律来简化逻辑表达式。

时序逻辑电路设计则更为复杂,因为它不仅考虑当前输入,还涉及电路的内部状态。这种类型的电路包括触发器、计数器、移位寄存器等,它们能够记忆信息并在不同的时间点改变输出。设计时序逻辑电路需要考虑同步和异步系统、状态机设计以及时钟同步等问题。

最后,阵列逻辑电路,如查找表(LUT)和可编程逻辑阵列(PLA),提供了高效的逻辑功能实现方式,特别是在大规模集成电路(VLSI)设计中。这些阵列允许设计者以更灵活的方式配置逻辑功能,以适应各种复杂的设计需求。

总结来说,计算机逻辑部件的学习涵盖了从基本逻辑概念到实际电路设计的广泛领域,是理解和设计数字系统的基石。无论是硬件工程师还是软件开发者,掌握这些知识对于理解和优化计算机系统性能都至关重要。

相关推荐

u010582871

- 粉丝: 0

最新资源

- Swift 5入门:iPhone开发高清电子书

- 台资灯饰厂用GPMRP$管理系统助力小型工厂运作优化

- 快速使用bat文件一键安装MySQL数据库教程

- 2018.12版eclipse与STS搭配,轻松搭建SpringBoot

- Web界面化耳部训练:无限练习曲平台介绍

- Sublime Text Ruby/Rails代码段插件升级版发布

- Java项目P1最终版深入解析

- Metalsmith插件实现React模板渲染技术

- runtimeviewer:Java运行时环境深度分析工具

- 掌握高性能PHP开发技术要点

- 掌握PSCAD直流线路建模仿真技巧

- 修复U盘RAW格式数据丢失的绿色工具

- 探索JavaScript中的错误代码及其解决方案

- 掌握静态时序分析STA技巧与应用

- 掌握Ruby编程:深入线程、SOLID、设计模式与数据结构

- 深入探索project-JS的JavaScript核心