LS-CPU-EXB-001实验指南:FPGA入门与数字逻辑设计

需积分: 0 112 浏览量

更新于2024-06-30

收藏 1.58MB DOCX 举报

本资源是一份名为"LS-数字逻辑实验指导手册-201710131"的文档,专注于FPGA开发领域的教育和实践。该手册涵盖了六个主要的实验部分,旨在帮助学生逐步熟悉和掌握数字逻辑电路的设计与实现,以及FPGA技术的入门知识。

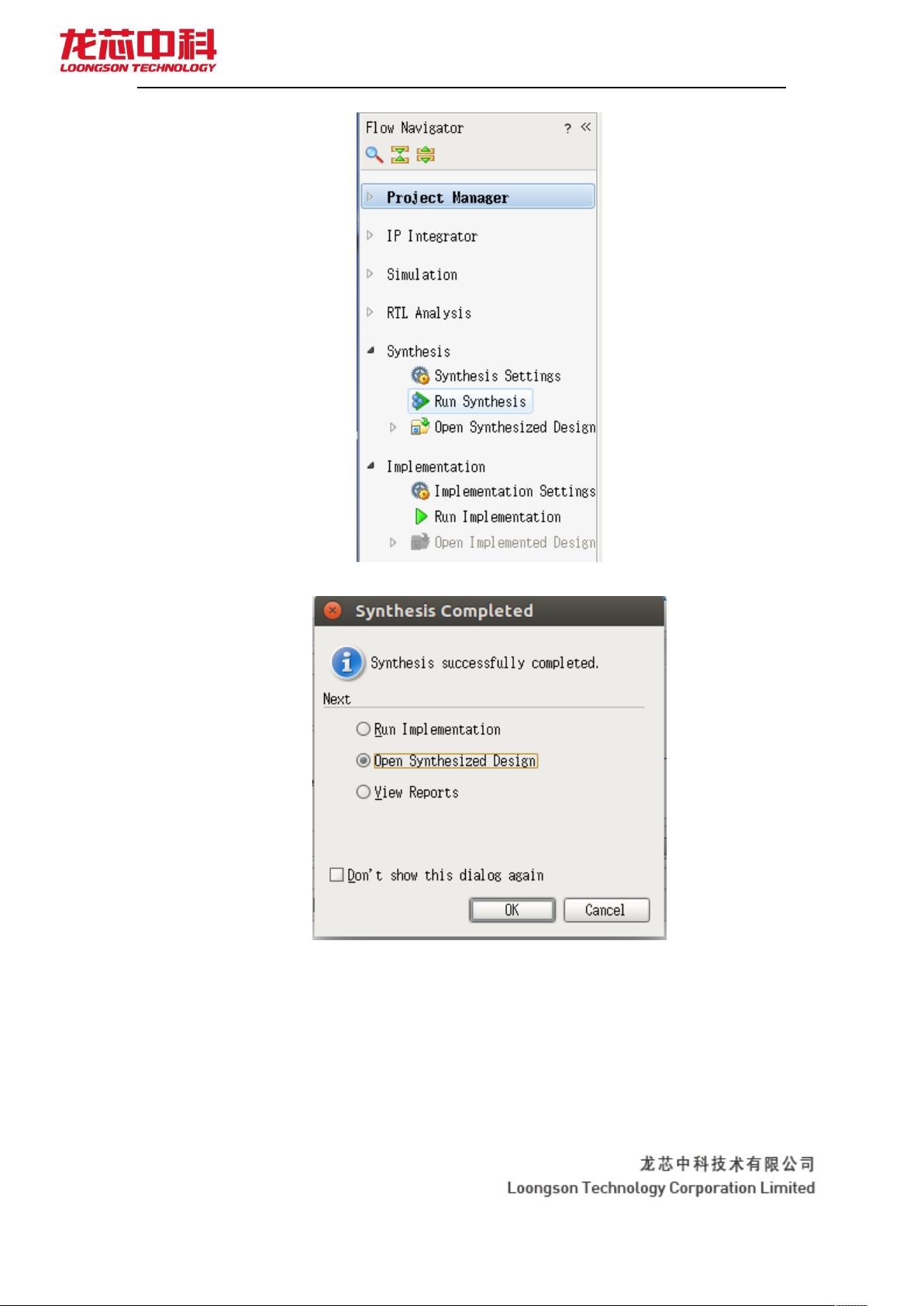

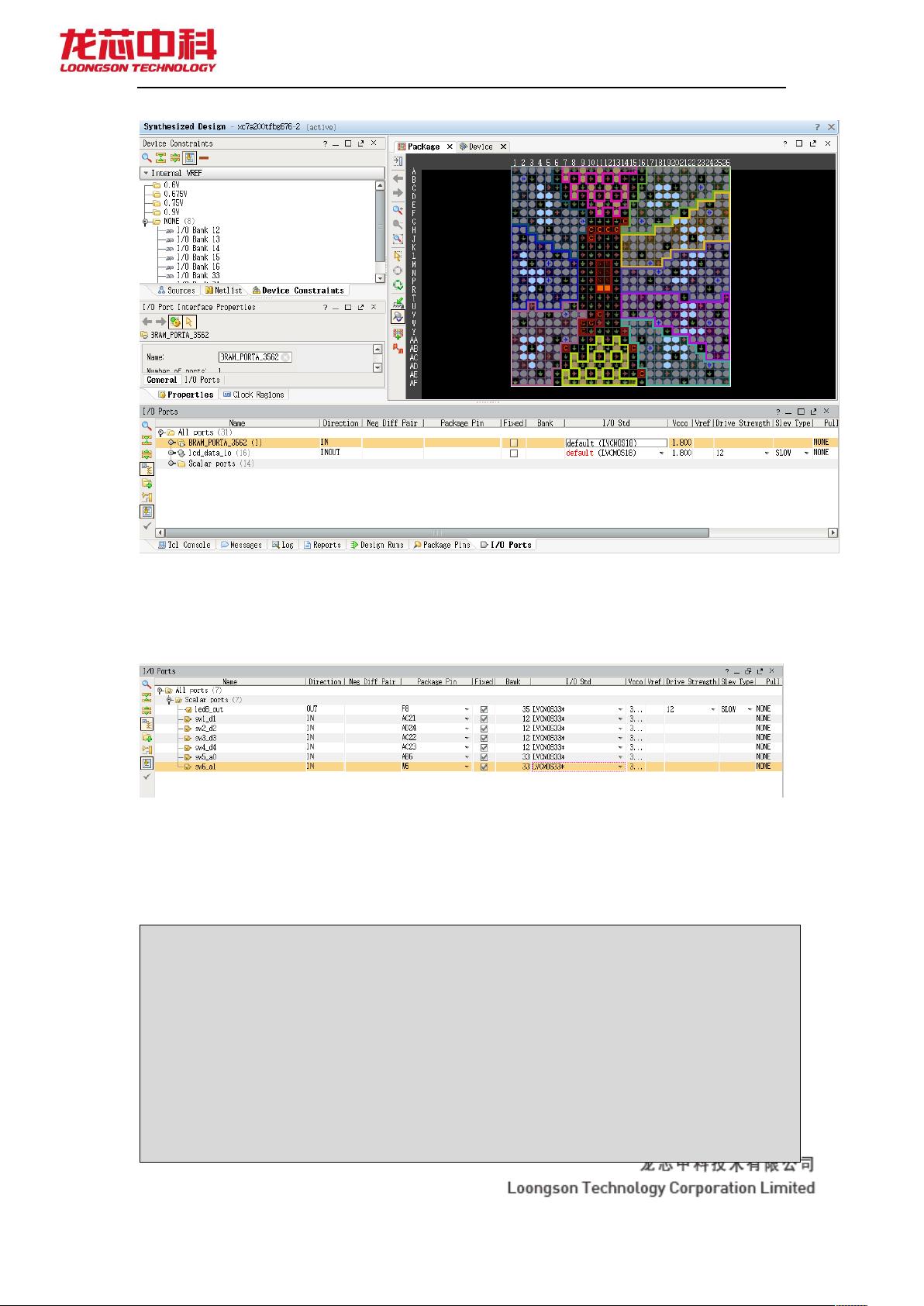

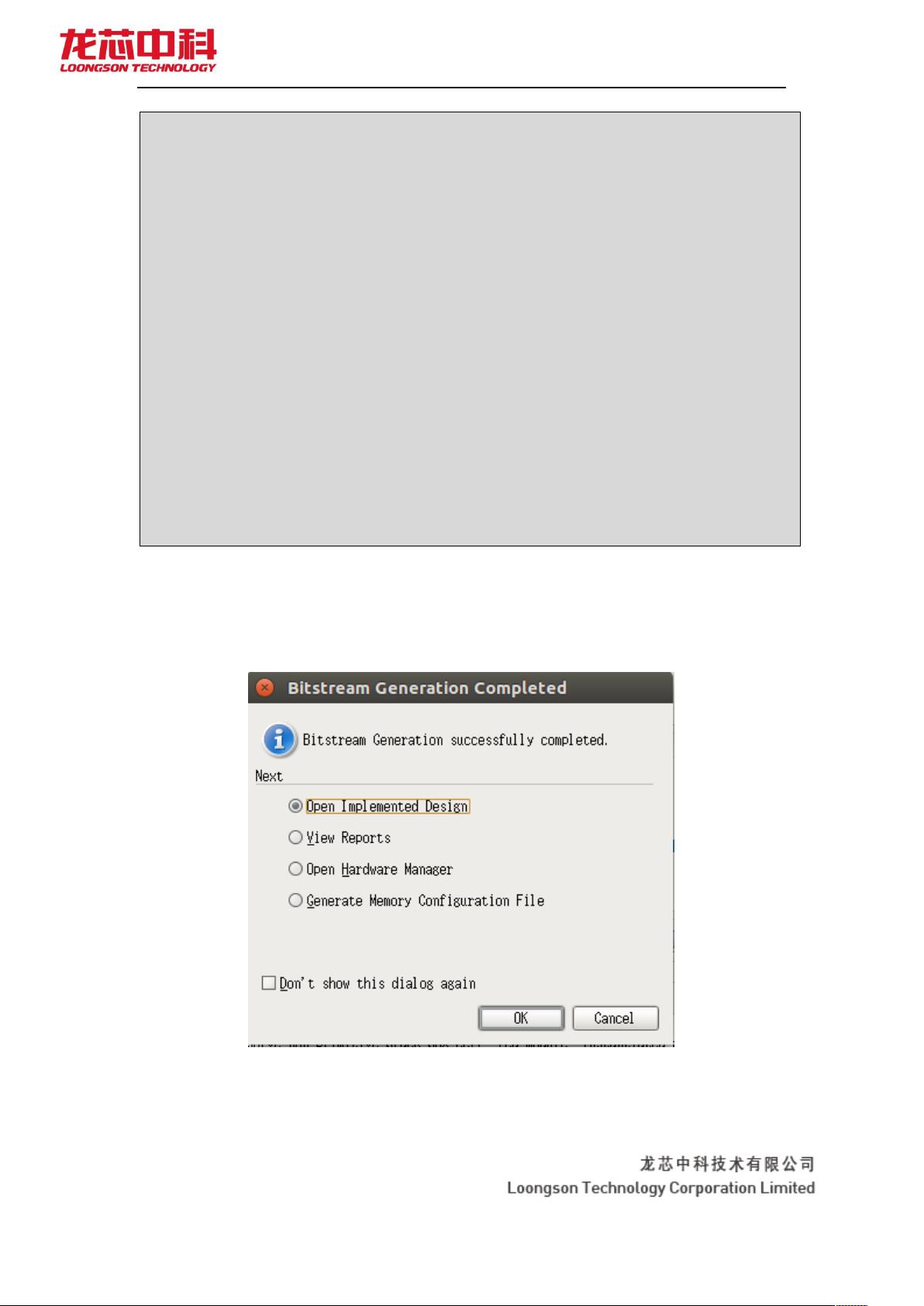

实验一,"基本门电路与FPGA环境熟悉",目标是让学生了解FPGA编程的基础,包括使用Xilinx公司的Vivado工具进行项目创建。在这个实验中,学生将学习如何设置工程、选择适合的器件型号(如Artix7的xc7a200tfbg676-2),并学会如何导入和编写Verilog代码。实验内容涉及4-1选择器、3-8译码器和8-3编码器的实现,这些电路均采用assign表达式和基本逻辑门(如与、或、非)来构建。

实验二至五分别探索组合逻辑电路、锁存器、时钟与触发器电路、以及存储器的设计,这些都是数字逻辑设计的重要组成部分,通过实际操作,学生可以深入理解它们的工作原理和在系统中的应用。

实验六,"综合实验(数字时钟)",可能涉及到时间敏感逻辑的设计,让学生能够综合运用前面所学,构建更复杂的时序逻辑系统,如设计一个数字时钟电路。

整个实验过程强调理论与实践相结合,通过实际动手操作,不仅提升了学生的编程技能,也锻炼了他们分析问题、解决问题的能力,为今后深入FPGA开发打下坚实的基础。这份手册不仅适合在校学生,对于初入FPGA领域的工程师或对数字逻辑感兴趣的爱好者也有很大的参考价值。

2022-07-09 上传

2022-08-03 上传

点击了解资源详情

2022-08-03 上传

2022-08-03 上传

2012-12-11 上传

2022-07-09 上传

食色也

- 粉丝: 37

- 资源: 351

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成