74LS279:四通道S-R锁存器技术详解

版权申诉

PDF格式 | 138KB |

更新于2024-08-02

| 87 浏览量 | 举报

"这是一份关于74LS279集成电路的文档,主要介绍了这款芯片在电子设计竞赛中的应用,适合大学生学习和参考。74LS279是四路S-R锁存器(Set-Reset Latches)的集成电路,常用于数字逻辑电路设计。文档包含了芯片的功能描述、特性、连接图以及功能表。"

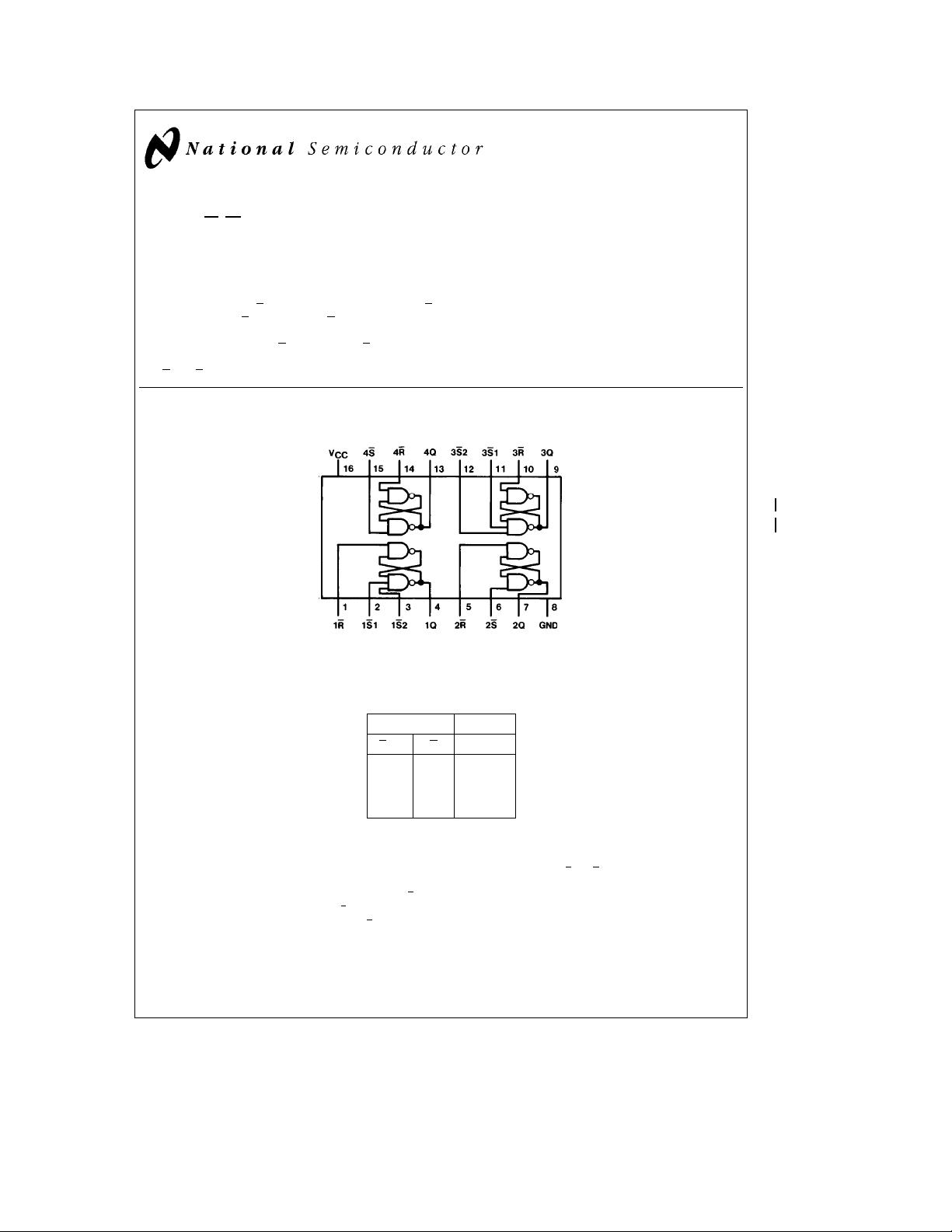

74LS279是一款由四个独立的S-R锁存器组成的集成电路,每个锁存器都有一个激活低电平的Set输入(S)和一个Reset输入(R)。S-R锁存器的主要作用是存储数据,在特定的时序控制下保持或改变输出状态。当R输入为高电平时,任何S输入的低电平都将被储存在锁存器中,并在对应的Q输出端表现为高电平。反之,如果S输入为高电平而R输入变为低电平,则会清除Q输出,使其变为低电平。如果R和S输入同时由低变高,则Q输出会处于不定状态。

该芯片的一个特殊之处在于其中两个锁存器具有额外的S输入,它与主S输入通过AND门连接,提供了更灵活的控制选项。S和R输入都采用电压电平触发,不依赖于输入数据的转换时间,这确保了电路的稳定性和可靠性。

74LS279的特性包括:

1. 提供了军用/航空航天版本(54LS279),具体规格需咨询国家半导体销售办公室或分销商。

2. 使用双列直插封装(Dual-In-Line Package)。

3. 具有明确的引脚连接图,方便用户进行电路设计。

4. 提供了清晰的功能表,明确了不同输入组合下的输出状态。

在实际应用中,74LS279常用于数据存储、信号缓冲、时序逻辑控制等场合。设计者可以根据提供的订单编号选择不同封装形式的芯片,如54LS279DMQB、54LS279LMQB等,以适应不同的电路需求。此外,为了确保电路设计的正确性,应参考相关封装图(如E20A、J16A等)进行引脚连接。

74LS279是数字电路设计中的一种基础元件,尤其对于参加电子设计竞赛的大学生来说,理解和掌握其工作原理和应用至关重要。通过这份文档,读者可以了解到74LS279的基本信息,为实际项目开发提供理论支持。

相关推荐

584 浏览量

2948 浏览量

2024-03-15 上传

280 浏览量

880 浏览量

206 浏览量

176 浏览量

2021-09-26 上传

2024-03-15 上传

阿拉伯梳子

- 粉丝: 2895

最新资源

- Linux下nginx 1.12版本负载均衡的部署与应用

- Laravel微服务日志处理器:附加相关ID

- Nginx1.9.7与Keepalive1.3.2搭建高可用集群

- C++进阶课程全新讲义:深入理解与实践

- Java数据分析项目源代码详解

- 实现PDF跳转打印功能的pdfobject.js技术解析

- 最新Navicat for SQLite 12.0.26版本mac下载

- Qt框架下的QWidget进程间通信技术详解

- 保护隐私:U盘移动硬盘加密与解密工具

- Linux进程调度算法设计与性能比较

- JavaMail必备:javamail1_4_5和jaf-1_1_1 Jar包使用指南

- C#实现邮箱发送与验证的源代码解析

- PHP节假日公告网页开发与MySQL数据库整合

- LabVIEW控制安捷伦直流电源教程

- Linux网络驱动开发技术文档详解

- Java单点登录(SSO)系统开发全流程教程