FPGA实现:分布式算法优化的低通FIR滤波器设计

22 浏览量

更新于2024-08-29

收藏 313KB PDF 举报

"基于FPGA分布式算法的滤波器设计"

本文主要探讨了如何利用FPGA(Field-Programmable Gate Array)的特性设计一种高效的分布式算法滤波器,特别是针对低通FIR(Finite Impulse Response)滤波器。传统的数字滤波器硬件实现通常依赖于ASIC(Application-Specific Integrated Circuit)和DSP(Digital Signal Processor),而FPGA因其内部的查找表(LUT)结构,提供了更高的并行处理能力和良好的可扩展性,成为了构建高性能可编程算法的优选平台。

分布式算法在FPGA设计中扮演着重要角色,尤其是在处理乘加运算时。由于FPGA的硬件乘法器资源有限,直接使用乘法会大量消耗资源。为此,文章提出了利用FPGA的存储器资源构建查找表运算,以此替代乘法操作,从而节省了硬件资源。通过这种方法,设计了一种基于分布式算法的低通FIR滤波器。

此外,为了进一步优化硬件规模,文章利用了线性相位FIR滤波器的对称性,这一特性使得部分计算可以复用,减少了所需的硬件元件。同时,通过分割查找表策略,减小了存储空间的需求,提高了设计的效率。

文章还提到了采用并行分布式算法结构和流水线技术来提升滤波器的运行速度。在FPGA上实现的这种滤波器,不仅具有较高的处理速度,而且通过合理的设计,能够在有限的硬件资源下实现复杂滤波功能。

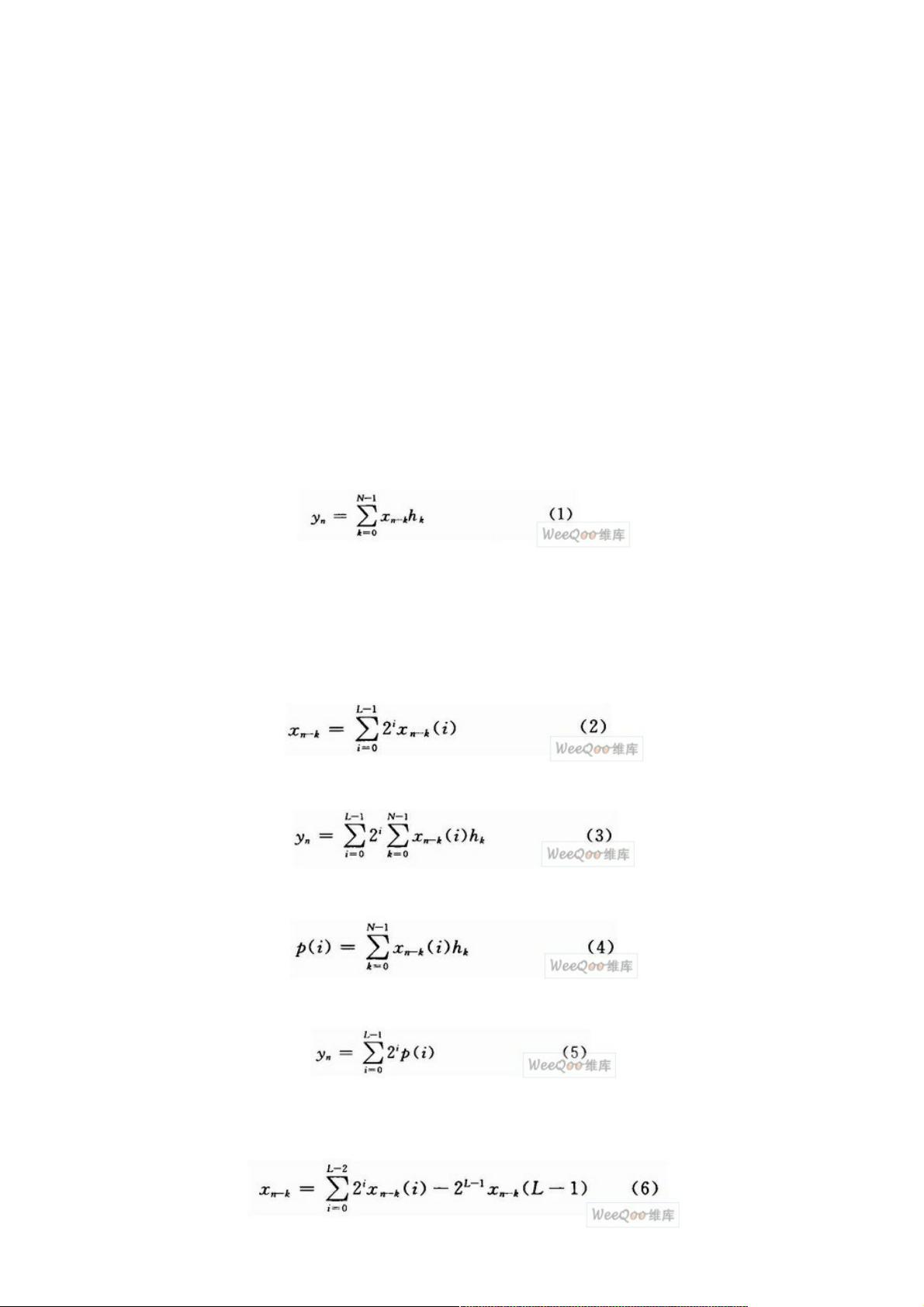

分布式算法在FIR滤波器中有两种常见的形式:无符号数的分布式算法和有符号数的分布式算法。在无符号数的分布式算法中,数据被并行处理,通过预计算和查找表,将乘法转换为常数乘法,大大降低了计算复杂度。而在有符号数的分布式算法中,考虑到补码表示,算法需要额外处理符号位,但仍能保持较高的效率。

本文详细介绍了一种基于FPGA的分布式算法滤波器设计方法,该方法充分利用了FPGA的并行处理能力,结合查找表和线性相位FIR滤波器的特性,实现了高效、节省资源的滤波器硬件实现。通过这种设计,可以在满足性能需求的同时,降低硬件成本,提高系统的实时处理能力。

440 浏览量

2013-10-01 上传

2021-07-04 上传

2023-07-12 上传

2024-10-27 上传

2024-10-27 上传

2024-11-04 上传

2024-11-03 上传

2024-11-03 上传

weixin_38583286

- 粉丝: 2

- 资源: 936

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器