SOPC驱动的JPEG2000实时编码器设计:基于小波变换与并行编码

下载需积分: 7 | PDF格式 | 697KB |

更新于2024-07-17

| 65 浏览量 | 举报

本文主要探讨了基于System-on-a-Programmable-Chip (SOPC) 的JPEG2000编码器设计。JPEG2000 是一种高效的数据压缩标准,特别适用于网络传输和多媒体应用,其硬件实现对于性能优化至关重要。作者王刚毅和胡小开在指导教师任广辉的指导下,针对这一需求,提出了一种创新的设计方法。

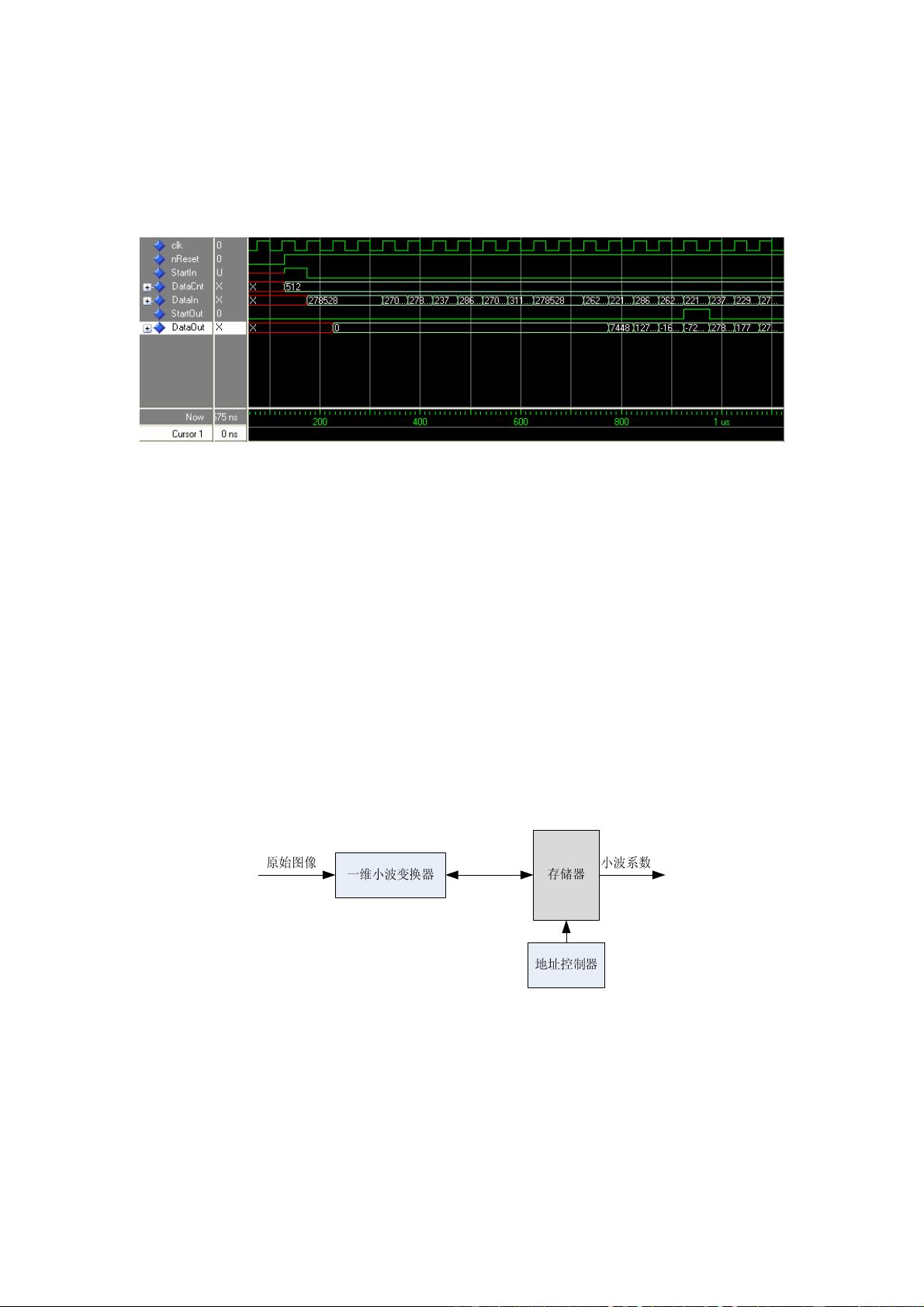

首先,他们优化了行式二维小波变换器结构,这在JPEG2000编码过程中用于信号的多尺度分析,能够捕捉图像的细节信息并进行高效编码。通过采用改进的结构,他们提高了变换的计算效率,这对于编码速度的提升至关重要。

其次,他们设计了一个位平面并行的位平面编码器,这种编码器能够在数据处理过程中充分利用硬件资源,同时实现数据的逐位编码,显著加快了编码过程。位平面编码是JPEG2000算法中的关键步骤,它通过分块和量化来减少数据冗余,提高编码效率。

接着,设计了一个四级流水线结构的算术编码器,流水线技术可以将多个操作并行化,使得编码过程中的每个阶段几乎同时进行,进一步提升了编码速度。算术编码是JPEG2000的另一个核心部分,通过连续逼近的方法,将熵编码与解码结合在一起,达到高效的编码效果。

整个设计被集成在一个SOPC平台上,即Altera公司的Stratix II系列EP2S60F1020C5,这个可编程片上系统允许设计师灵活地部署和优化各种功能模块,以适应特定的应用需求。通过实验验证,该编码器在98MHz的最高时钟频率下,能以每秒52帧的速度处理512x512灰度图像,达到了实时编码的要求,证明了设计的高效性和实用性。

这篇论文的核心知识点包括SOPC技术在JPEG2000编码器中的应用、优化的二维小波变换、位平面并行编码器和流水线算术编码器的设计,以及如何通过硬件加速实现JPEG2000标准的高效实时编码。这项研究对于推动JPEG2000在嵌入式和实时应用中的广泛应用具有重要的实际价值。

相关推荐

drjiachen

- 粉丝: 172

最新资源

- 武汉大学数字图像处理课程课件精要

- 搭建个性化知识付费平台——Laravel开发MeEdu教程

- SSD7练习7完整解答指南

- Android中文API合集第三版:开发者必备指南

- Python测试自动化实践:深入理解更多测试案例

- 中国风室内装饰网站模板设计发布

- Android情景模式中音量定时控制与铃声设置技巧

- 温度城市的TypeScript实践应用

- 新版高通QPST刷机工具下载支持高通CPU

- C++实现24点问题求解的源代码

- 核电厂水处理系统的自动化控制解决方案

- 自定义进度条组件AMProgressView用于统计与下载进度展示

- 中国古典红木家具网页模板免费下载

- CSS定位技术之Position-master解析

- 复选框状态持久化及其日期同步技术

- Winform版HTML编辑器:强大功能与广泛适用性