Spartan-3 FPGA Family: Functional Description

DS312 (4.0) October 29, 2012 www.xilinx.com

Product Specification 18

PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

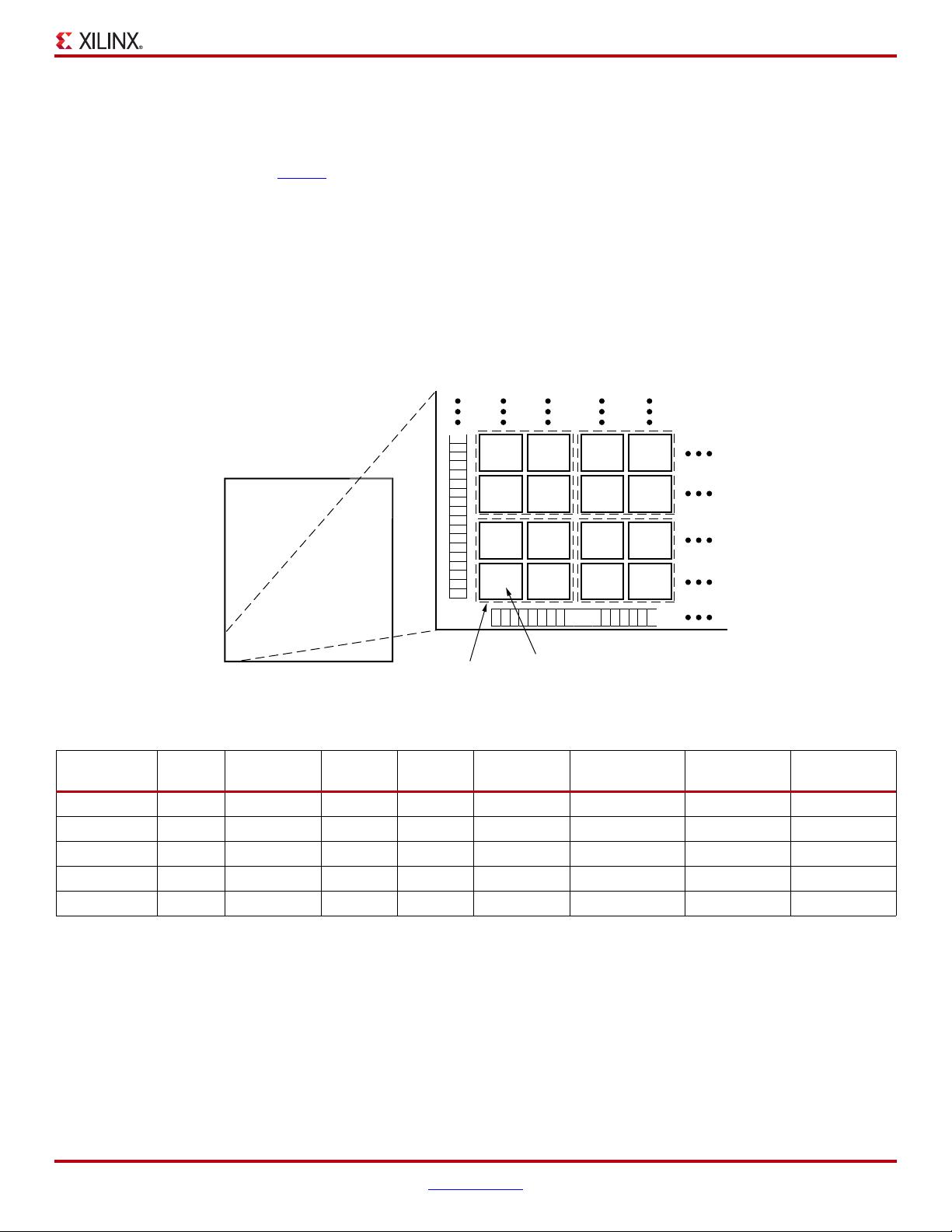

IOBs Organized into Banks

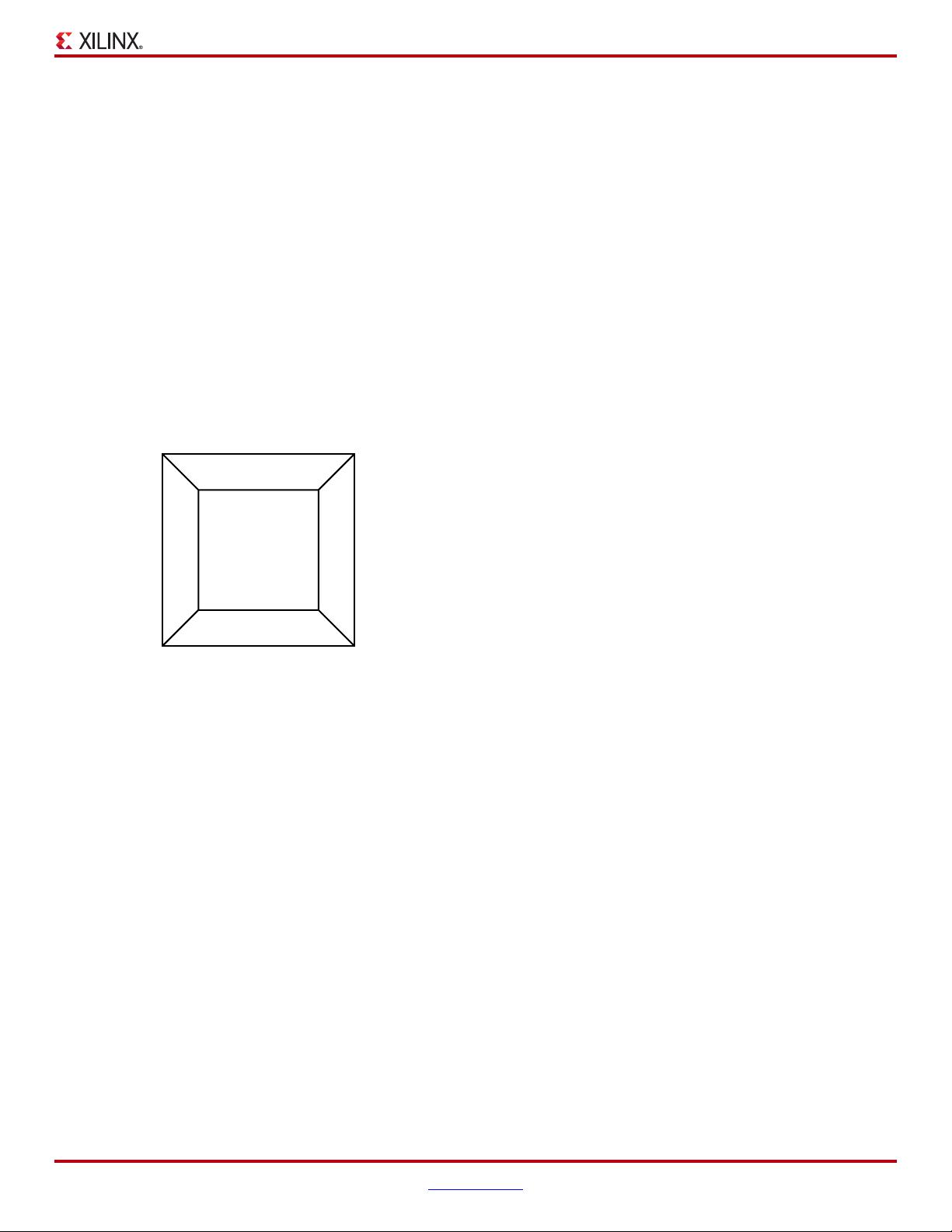

The Spartan-3E architecture organizes IOBs into four I/O

banks as shown in Figure 13. Each bank maintains

separate V

CCO

and V

REF

supplies. The separate supplies

allow each bank to independently set V

CCO

. Similarly, the

V

REF

supplies can be set for each bank. Refer to Ta bl e 6

and Tab l e 7 for V

CCO

and V

REF

requirements.

When working with Spartan-3E devices, most of the

differential I/O standards are compatible and can be

combined within any given bank. Each bank can support

any two of the following differential standards: LVDS_25

outputs, MINI_LVDS_25 outputs, and RSDS_25 outputs. As

an example, LVDS_25 outputs, RSDS_25 outputs, and any

other differential inputs while using on-chip differential

termination are a valid combination. A combination not

allowed is a single bank with LVDS_25 outputs, RSDS_25

outputs, and MINI_LVDS_25 outputs.

I/O Banking Rules

When assigning I/Os to banks, these V

CCO

rules must be

followed:

1. All V

CCO

pins on the FPGA must be connected even if a

bank is unused.

2. All V

CCO

lines associated within a bank must be set to

the same voltage level.

3. The V

CCO

levels used by all standards assigned to the

I/Os of any given bank must agree. The Xilinx

development software checks for this. Ta bl e 6 and

Tabl e 7 describe how different standards use the V

CCO

supply.

4. If a bank does not have any V

CCO

requirements,

connect V

CCO

to an available voltage, such as 2.5V or

3.3V. Some configuration modes might place additional

V

CCO

requirements. Refer to Configuration for more

information.

If any of the standards assigned to the Inputs of the bank

use V

REF

, then the following additional rules must be

observed:

1. All V

REF

pins must be connected within a bank.

2. All V

REF

lines associated with the bank must be set to

the same voltage level.

3. The V

REF

levels used by all standards assigned to the

Inputs of the bank must agree. The Xilinx development

software checks for this. Ta bl e 6 describes how different

standards use the V

REF

supply.

If V

REF

is not required to bias the input switching thresholds,

all associated V

REF

pins within the bank can be used as

user I/Os or input pins.

Package Footprint Compatibility

Sometimes, applications outgrow the logic capacity of a

specific Spartan-3E FPGA. Fortunately, the Spartan-3E

family is designed so that multiple part types are available in

pin-compatible package footprints, as described in

Module 4, Pinout Descriptions. In some cases, there are

subtle differences between devices available in the same

footprint. These differences are outlined for each package,

such as pins that are unconnected on one device but

connected on another in the same package or pins that are

dedicated inputs on one package but full I/O on another.

When designing the printed circuit board (PCB), plan for

potential future upgrades and package migration.

The Spartan-3E family is not pin-compatible with any

previous Xilinx FPGA family.

Dedicated Inputs

Dedicated Inputs are IOBs used only as inputs. Pin names

designate a Dedicated Input if the name starts with IP, for

example, IP or IP_Lxxx_x. Dedicated inputs retain the full

functionality of the IOB for input functions with a single

exception for differential inputs (IP_Lxxx_x). For the

differential Dedicated Inputs, the on-chip differential

termination is not available. To replace the on-chip

differential termination, choose a differential pair that

supports outputs (IO_Lxxx_x) or use an external 100Ω

termination resistor on the board.

ESD Protection

Clamp diodes protect all device pads against damage from

Electro-Static Discharge (ESD) as well as excessive voltage

transients. Each I/O has two clamp diodes: one diode

extends P-to-N from the pad to V

CCO

and a second diode

extends N-to-P from the pad to GND. During operation,

these diodes are normally biased in the off state. These

clamp diodes are always connected to the pad, regardless

of the signal standard selected. The presence of diodes

limits the ability of Spartan-3E I/Os to tolerate high signal

voltages. The V

IN

absolute maximum rating in Table 7 3 of

Module 3, DC and Switching Characteristics specifies the

voltage range that I/Os can tolerate.

X-Ref Target - Figure 13

Figure 13: Spartan-3E I/O Banks (top view)

DS312-2_26_021205

Bank 0

Bank 2

Bank 3

Bank 1