DDR内存关键技术解析:差分时钟与DQS的作用

需积分: 25 138 浏览量

更新于2024-09-07

收藏 696KB PDF 举报

"本文档主要介绍了DDR内存技术的关键特性,包括差分时钟技术和数据选取脉冲(DQS)的功能及作用。"

DDR内存技术自推出以来,经历了一系列的升级,如DDR2、DDR3、DDR4等,这些升级带来了诸多关键性的技术改进,以提升内存的性能和效率。本文主要探讨了DDR内存的两个核心技术:差分时钟技术和DQS信号。

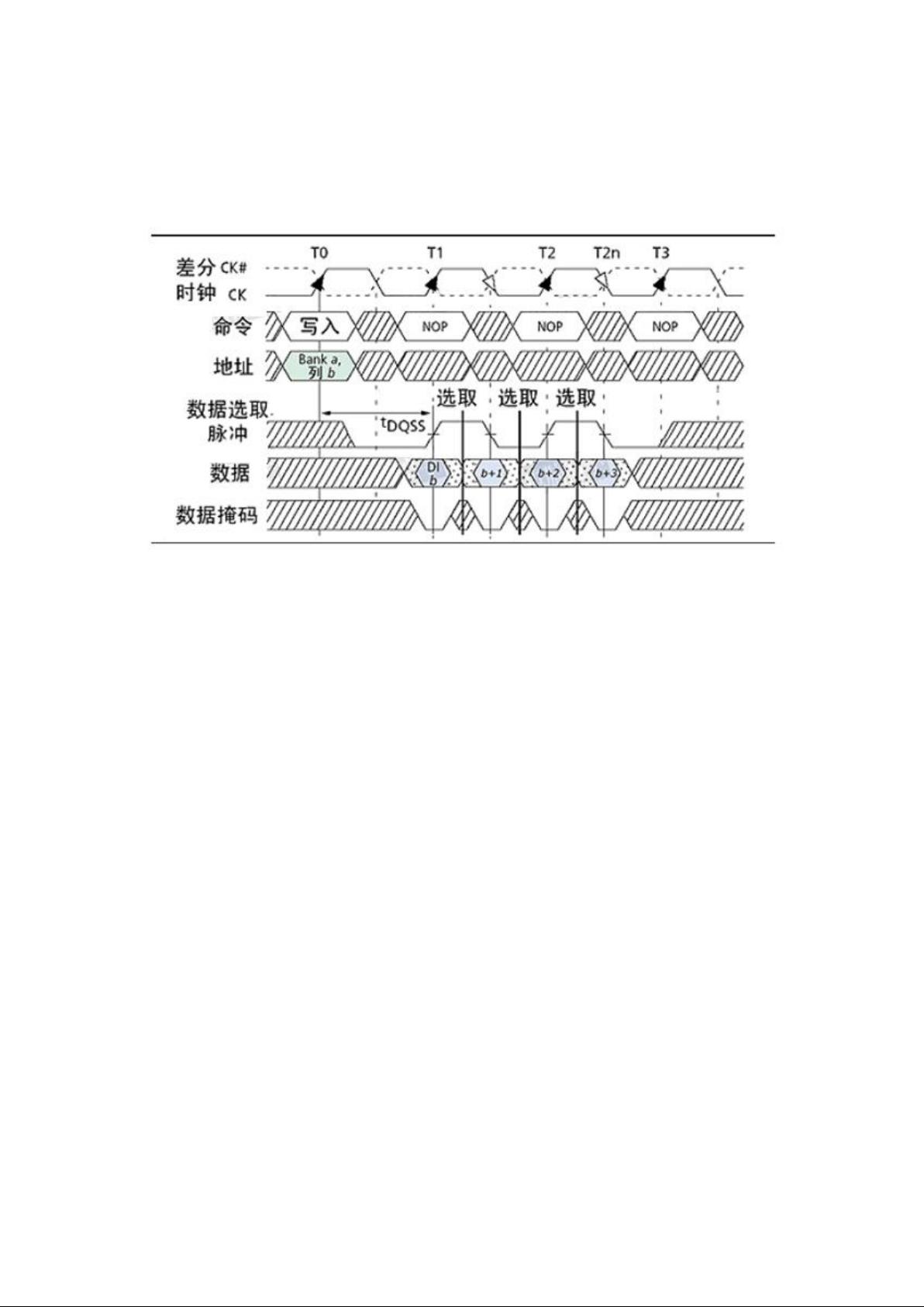

首先,差分时钟技术是DDR内存高速传输的基础。DDR内存采用双倍数据速率,即数据在时钟的上升沿和下降沿都被传输,这使得数据传输速率翻倍,但同时也对时钟精度提出了更高要求。CK#(CKN)作为差分时钟的一部分,起到了关键的时钟校准作用。当环境因素如温度变化或电阻性能变动导致CK的上下沿间距不稳定时,CK#通过其相反的上升和下降速度进行补偿,确保数据传输的准确性。这一机制保证了即使在各种环境下,数据也能被正确地捕获和处理。

其次,数据选取脉冲(DQS)是DDR内存中不可或缺的一部分,它充当数据传输的同步信号。每一颗8bit DRAM芯片都有一条DQS信号线,用于在读写操作中协调数据传输。在写入时,DQS线接收来自主控器的信号;在读取时,DRAM芯片生成DQS信号回传给主控器。DQS的生成与CK和CK#的交叉点相对应,确保数据传输的精确时序。DQS的延迟时间(tAC)定义了数据相对于DQS触发的实际延迟,预取操作使得数据可能在DQS信号之前就已经准备好。对于DDR内存,tAC的允许误差范围是严格的,以确保并行传输的多个数据线上的数据同步性。

在接收端,数据接收不是简单地依据DQS的上下沿,而是根据设定的tAC来确保数据的正确采样。由于预取操作和并行传输的特性,数据在各个I/O端口的出现时间可能存在差异,因此需要DQS作为参考点来分割数据周期,确保接收的同步性。在写入操作中,DRAM芯片会按照传来的DQS信号调整自身的数据周期,以DQS的中间点作为数据传输的分割点,从而保证传输的准确性和一致性。

DDR内存的关键技术在于其差分时钟系统和DQS同步机制,这两者共同确保了数据的高效、准确和稳定传输,是DDR内存性能提升的重要基石。了解这些技术对于理解和优化系统性能至关重要。

1513 浏览量

2539 浏览量

2023-04-24 上传

2021-07-13 上传

1749 浏览量

2021-05-25 上传

2019-05-21 上传

2022-09-14 上传

七月草

- 粉丝: 0

- 资源: 4

最新资源

- 【容智iBot】8iBot=RPA+AI:数字化生产力为企业赋能.rar

- 操作系统课件+实验.rar_mightpol_wonsps_操作系统_操作系统实验

- TestYo:测试

- iocage-plugin-zabbix5-server

- 时代变频器在纺织机械行业中的应用.rar

- 【容智iBot】7你知道AI人工智能对我们的意义吗?.rar

- gimp-plugin-pixel-art-scalers:Gimp插件,用于使用hqx,xbr和scalex等Pixel Art Scalers重新缩放图像

- SpringBoot2.7整合SpringSecurity+Jwt+Redis+MySQL+MyBatis完整项目代码

- tarsnapper:tarsnap包装器,使用gfs-scheme使备份失效

- HC110110017 链路状态路由协议-OSPF-ospf.rar

- AreSolutionsClinicMobile:Spring世博会命令行界面,API消费和Spring启动

- Map-Fu-开源

- webbrowser自动填表,并获取网页源码(iframe框架也可获取网页源码)

- janeway::milky_way:具有对象检查和许多其他功能的Node.js控制台REPL

- 批量单词翻译

- indicator:财务指标(EMA,MACD,SMA)