QuartusⅡ9.0初学者教程:从启动到3-8译码器设计

需积分: 16 109 浏览量

更新于2024-09-09

收藏 818KB DOC 举报

"Quartus使用教程"

QuartusⅡ是Altera公司开发的一款强大的电子设计自动化(EDA)工具,适用于数字系统的设计与实现。它支持多种输入方式,包括原理图输入和硬件描述语言(如VHDL或Verilog)。本教程主要针对初学者,介绍如何使用QuartusⅡ9.0进行基本操作。

首先,启动QuartusⅡ软件。软件界面由几个关键部分组成:快捷工具栏提供了常用功能的快捷方式,如设置和编译;菜单栏包含所有功能的控制选项,用户可以通过下拉菜单找到所需功能;编译及综合进度栏显示了编译和综合的进度,100%表示任务已完成;信息栏则会显示编译和综合过程中的详细信息,包括错误和警告。

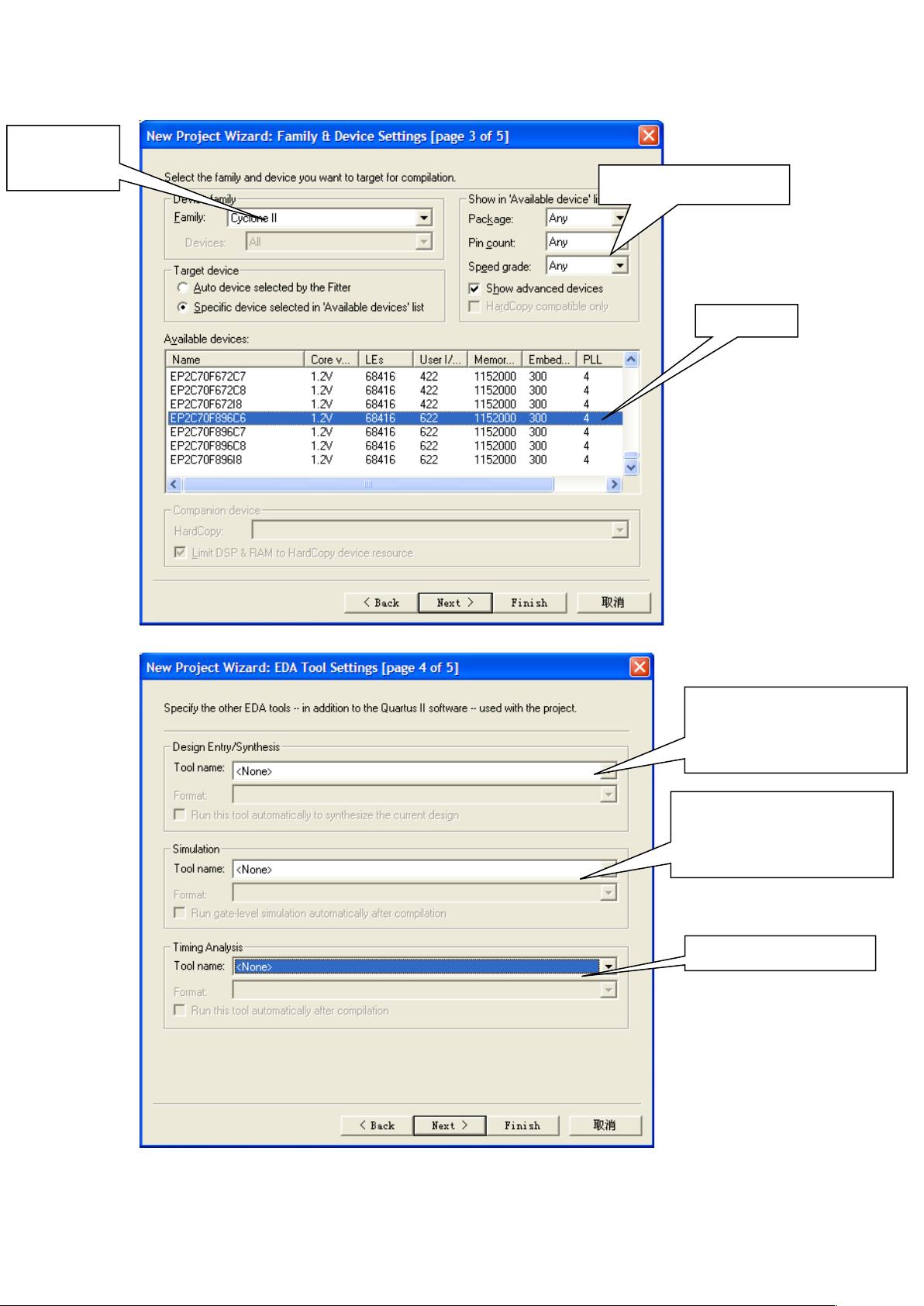

创建新工程是使用QuartusⅡ的第一步。在“File”菜单中选择“New Project Wizard”,然后按照向导进行操作。在工程名称中输入项目名称,如果有已有的文件,可以选择添加;接着选择合适的芯片型号,例如MAX3000A系列下的EPM3256AQC208-10;在选择仿真、综合工具的步骤中,初学者可以选择不使用任何工具,直接点击“Next”;最后点击“Finish”完成工程的创建。

接下来是添加文件到工程中。在“File”菜单中选择“New”,然后选择“VHDL File”。新建完成后记得保存文件。VHDL是一种广泛使用的硬件描述语言,用于描述数字系统的逻辑行为。

以3-8译码器为例,VHDL源代码如下:

```vhdl

library ieee;

use ieee.std_logic_1164.all;

entity decoder3_8 is

port(

A: in std_logic_vector(2 downto 0); -- 输入信号

EN: in std_logic; -- 使能信号

Y: out std_logic_vector(7 downto 0) -- 输出信号

);

end decoder3_8;

architecture example_1 of decoder3_8 is

signal sel: std_logic_vector(3 downto 0);

begin

sel <= A & EN; -- 合并输入信号A和使能信号EN

with sel select

Y <= "11111110" when "0001",

"11111101" when "0011",

"11111011" when "0101",

"11110111" when "0111",

"11101111" when others; -- 其他情况的默认输出

end example_1;

```

这段代码定义了一个3-8译码器,它有3个输入(A[2:0])和1个使能输入(EN),以及8个输出(Y[7:0])。根据输入信号的不同组合,输出信号Y会呈现不同的状态。

在完成代码编写后,需要进行编译和仿真以验证设计的正确性。在QuartusⅡ中,可以使用快捷工具栏的编译按钮或在菜单栏中选择“Assignments” -> “Settings”来配置编译选项。编译完成后,可以通过信息栏查看编译结果,如果出现错误,根据提示进行修改。

此外,QuartusⅡ还支持逻辑优化、时序分析、引脚分配等功能,以确保设计满足性能和物理限制。一旦设计通过了所有测试,可以生成编程文件并下载到目标设备中实现实际应用。

QuartusⅡ是一款功能强大的工具,它为数字系统的设计者提供了便捷的环境。通过这个基础教程,初学者可以逐步掌握使用QuartusⅡ进行VHDL设计的基本流程,为进一步深入学习和实践打下坚实的基础。

点击了解资源详情

2444 浏览量

点击了解资源详情

143 浏览量

2024-11-21 上传

2024-11-15 上传

525 浏览量

1040 浏览量