逻辑电平设计规范详解:GTL与LVDS

需积分: 9 157 浏览量

更新于2024-07-28

收藏 1.53MB PDF 举报

“逻辑电平设计规范,源自华为内部资料,涵盖GTL、LVDS、ECL等逻辑电平的原理、特点、设计与测试。”

在电子设计领域,逻辑电平设计规范是至关重要的,它确保不同组件之间的通信有效且可靠。这份资料详细介绍了多种逻辑电平标准,包括TTL、CMOS、LVDS、ECL及其衍生类型,这些都是数字电路中常见的电平标准。以下是各部分的详细说明:

1. **逻辑电平简介**:逻辑电平定义了数字电路中信号高低状态的电压范围,如TTL(晶体管-晶体管逻辑)和CMOS(互补金属氧化物半导体)电平。它们是数字系统的基础,决定了电路如何识别“1”和“0”。

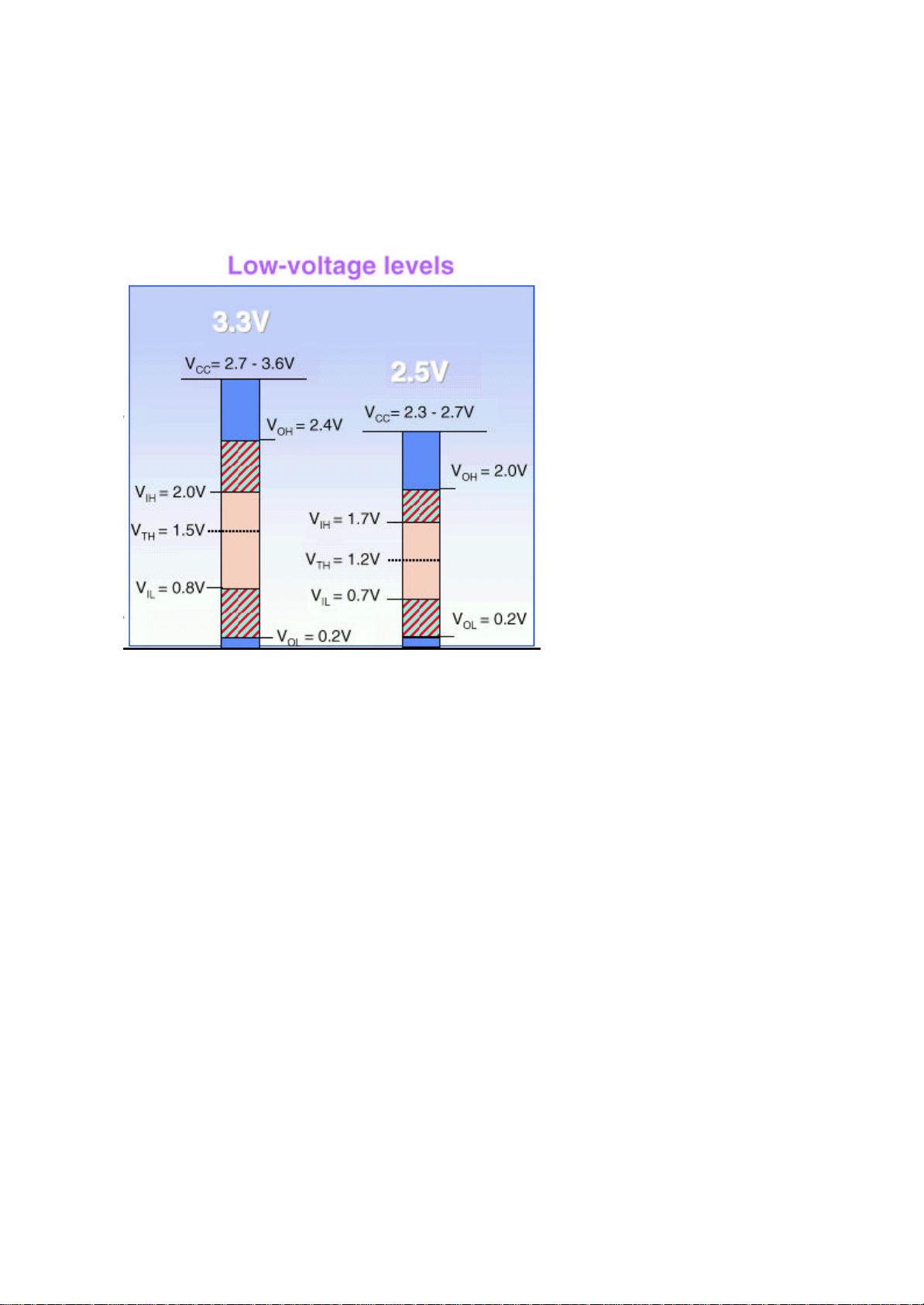

2. **TTL和CMOS逻辑器件**:TTL以其高速度和高功耗著称,而CMOS则以低功耗和高集成度见长。它们有不同的电平分类特点,工艺分类特点以及功能分类,如图1-1所示,涵盖了各种常见的逻辑系列器件。

3. **TTL和CMOS器件的互连**:这部分详细讲解了如何正确连接不同电平的TTL和CMOS器件,包括使用不同电压等级的TTL门作为驱动源,如5V TTL和3.3V TTL/CMOS,以及对互连总则的介绍,确保信号在传输过程中不失真。

4. **ECL器件**:ECL(Emitter-Coupled Logic)是一种高速逻辑技术,其特点是速度快但功耗大。ECL电路的特性包括ECL器件的原理、互连方式、匹配方法,以及使用原则和实例,旨在帮助设计者理解和应用ECL技术。

5. **PECL/LVPECL**:PECL(Positive Emitter-Coupled Logic)和LVPECL(Low-Voltage Positive Emitter-Coupled Logic)是ECL的低电压版本,具有更低的功耗。这部分讲解了PECL/LVPECL的工作原理、特点以及匹配和使用方法。

6. **LVDS器件**:LVDS(Low-Voltage Differential Signaling)是低电压差分信号的缩写,用于高速数据传输。LVDS器件的介绍包括其工作原理、特点、设计和测试方法,以及应用举例,帮助设计者掌握LVDS系统的实现。

7. **GTL器件**:GTL(Gated Transistor Logic)是一种高速、低功耗的接口技术。GTL信号的讨论涉及其特点、电平、PCB设计以及测试和时序要求,这些内容对于优化高速数字系统的设计至关重要。

8. **附录**:可能包含了更详细的技术参数、表格或补充信息,以供设计者参考。

了解和遵循这些逻辑电平设计规范能确保电路设计的兼容性和稳定性,减少潜在的信号完整性问题,提高系统的整体性能。无论是硬件工程师还是软件工程师,对这些电平标准的理解都对于开发高效、可靠的电子设备至关重要。

2010-05-12 上传

2008-09-01 上传

2011-08-09 上传

2020-01-11 上传

2010-06-25 上传

2019-12-03 上传

点击了解资源详情

点击了解资源详情

五星老管

- 粉丝: 2

- 资源: 13

最新资源

- curso-backend-nodejs

- astropy:Astropy核心软件包的存储库

- labor:作业服务,看起来很轻巧

- 码头工人麋鹿

- DbExporterHelper:这个小的库可帮助您导出db,导出到csv以及导入db,还可以与Room db一起使用

- spvdeconv.zip_图形图像处理_Visual_C++_

- codesnippet-api

- pivottablejs-airgap:适用于气隙系统的数据透视表

- idiots.win:Google自动完成猜游戏

- electron-serialport:在电子应用程序中如何使用串行端口的示例

- sufyanfarea:程序员产品组合

- Simple bookmark-crx插件

- qtile:用Python编写和配置的功能齐全的可破解平铺窗口管理器

- bpmndemo2020

- r2ddi:使用R从各种数据格式提取DDI

- A java based CMPP implement-开源