降低ASIC缺陷率:测试、ATPG与成本分析

需积分: 17 60 浏览量

更新于2024-07-07

收藏 655KB PDF 举报

本文档主要关注于测试与故障诊断在集成电路设计中的重要性,特别是针对ASIC(Application-Specific Integrated Circuit)的设计流程。章节14.1探讨了测试的重要性,着重于降低缺陷密度对成本的影响。文档引用了SmithText的部分章节,尤其是14.1、14.3和14.4,强调了在ASIC设计过程中预防和减少缺陷对于确保产品质量和系统可靠性至关关键。

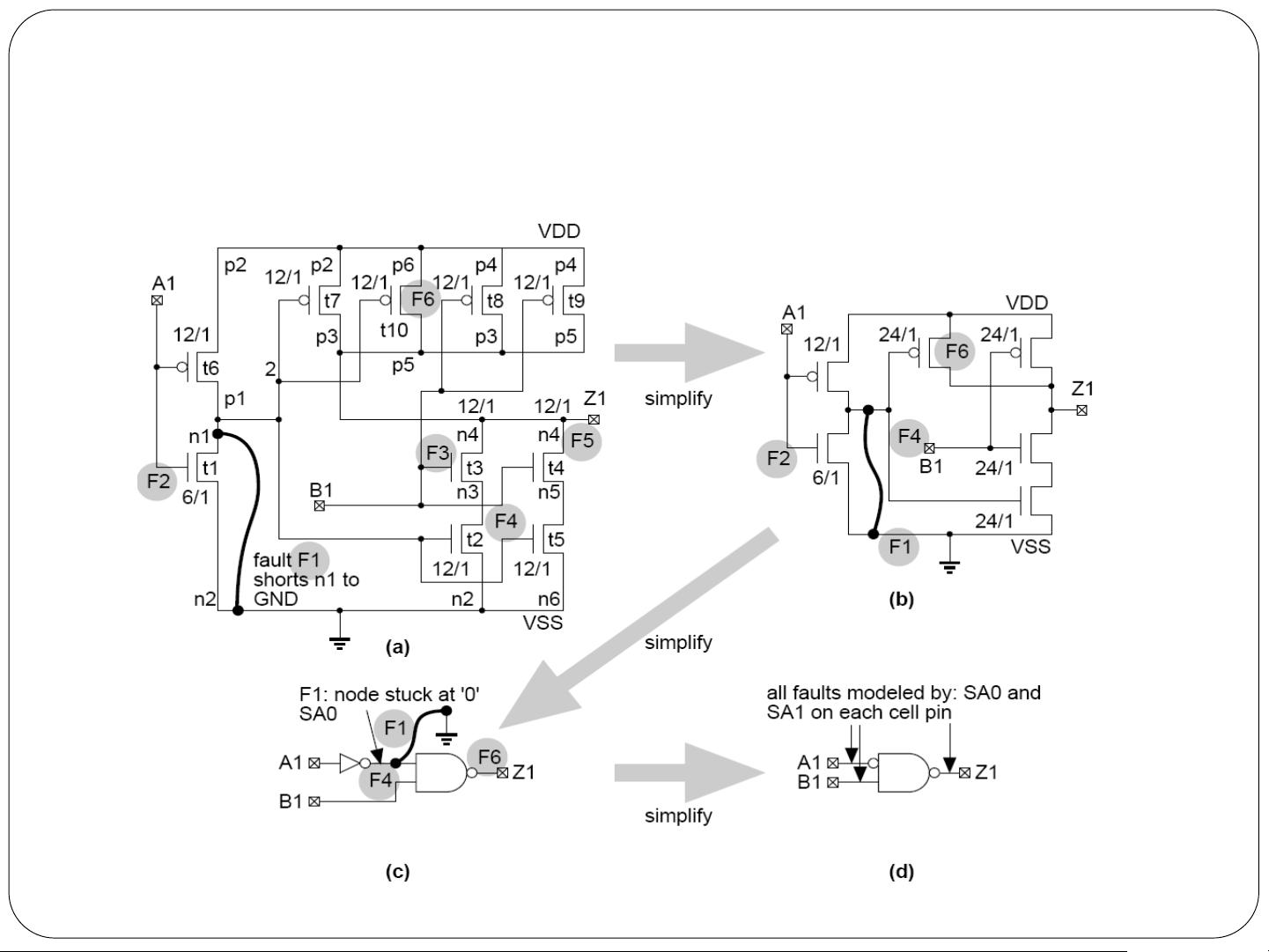

MentorGraphics/Tessent提供的资源包括《Scan and ATPG Process Guide》和《ATPG and Failure Diagnosis Tools Reference Manual》,这些手册通过mgcdocs平台获取,提供了关于静态时序分析(Scan and ATPG)以及故障诊断工具的详细指导。静态时序分析(Scan Test and ATPG, Automatic Test Pattern Generator)是验证电路功能和时序的关键步骤,它在行为模型、VHDL/Verilog的门级网表、晶体管级网表和物理布局等层次上进行。

从成本角度来看,降低缺陷密度从5%到1%会带来显著的节省。根据提供的数据,当前的缺陷率导致总PCB修复成本为$1 million,如果能将缺陷率降至1%,这个成本将下降到$200,000,节省了$800,000。同时,系统总维修成本也将从$5 million降低到$1 million,节省$4 million。这表明了测试在预防和减少缺陷方面对整体项目经济效益的巨大影响。

测试设计流程包括从行为模型(如VHDL/Verilog)到门级、晶体管级和物理布局的映射、放置、布线(Map/Place/Route),以及使用DFT(Design for Testability)和BIST( Built-In Self-Test)技术来集成测试能力。此外,文档还提到了验证函数、时序验证、DRC(Design Rule Checking)和LVS(Layout Versus Schematic)的重要性,这些都是确保设计符合规范和性能要求的必要步骤。

对于标准单元IC和FPGA/CPLD,测试向量(Test Vectors)的生成是定制集成电路设计不可或缺的一部分。而针对全定制IC,维修或替换整个系统的成本显著高于替换部分组件,这突出了预防性测试和早期发现缺陷的紧迫性。

文档还提及了制造环节的成本细节,例如每批100,000个零件的生产成本为$10,PCB成本为$200,系统成本为$5,000,总计$5,200 per unit。系统维修/更换成本为$10,000,表明了整个供应链的经济影响。

总结来说,Test_ATPG.pdf文件深入剖析了ASIC设计中的测试和故障诊断策略,重点关注了其在成本效益分析中的角色,特别是在减少缺陷密度和提高整体产品可靠性的过程中所扮演的关键作用。理解并优化测试流程、选择合适的故障模型和支持工具,对于降低缺陷率并确保产品商业成功至关重要。

2022-09-24 上传

2021-03-13 上传

2023-09-18 上传

2019-11-01 上传

2020-07-16 上传

2023-04-24 上传

2023-08-06 上传

2021-09-24 上传

2021-09-16 上传

zhuangdk

- 粉丝: 1803

- 资源: 14

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍