FPGA实现的通用SPI通信接口设计

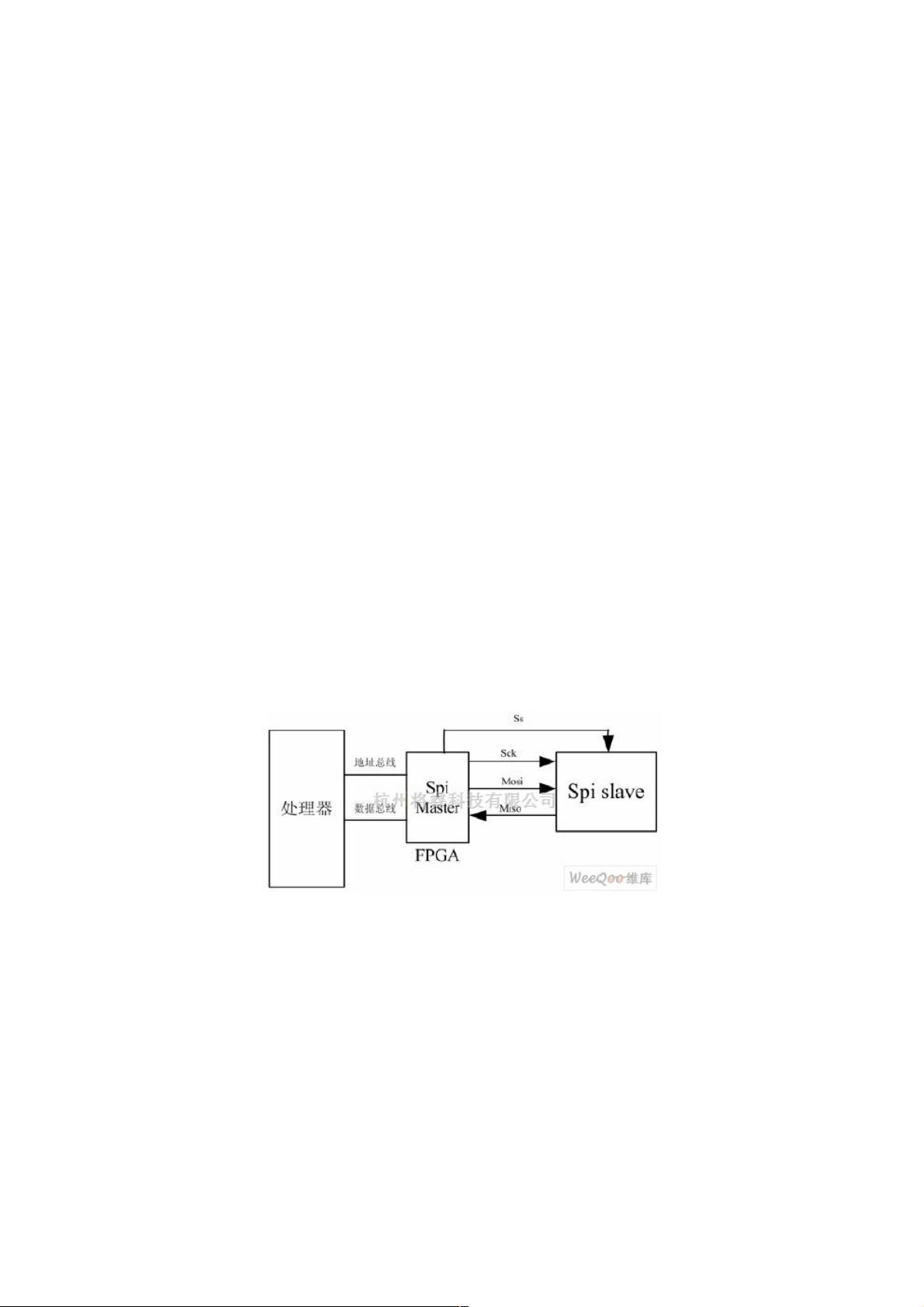

"EDA/PLD中的基于FPGA的可复用通信接口设计" 在当前的集成电路设计领域,系统级设计已经成为主流趋势,而如何有效地解决不同模块之间的接口问题成为关键。SPI(Serial Peripheral Interface)串行外设接口因其简洁的结构和广泛的适用性,成为了设计师们青睐的通信协议。本文探讨了一种创新的FPGA实现SPI总线的通用方法,旨在提升系统的灵活性和效率。 SPI接口是一种全双工同步串行通信接口,它通常由主机(Master)和从机(Slave)组成,支持多从机配置,数据传输速率可调,且只需四根信号线——时钟(SCLK)、主设备输出从设备输入(MISO)、主设备输入从设备输出(MOSI)、片选(CS)。由于这些特性,SPI在嵌入式系统和各种传感器、存储器等外设之间通信中被广泛采用。 传统的SPI接口实现方式通常是通过微处理器的GPIO端口配合软件模拟SPI协议,但这会占用大量的CPU资源,降低系统性能,并且在需要与多个SPI设备交互时,管理复杂度显著增加。FPGA(Field-Programmable Gate Array)的出现为解决这一问题提供了新思路。FPGA的可编程特性使得我们可以定制硬件逻辑,实现高效、专用的SPI控制器,从而减轻CPU负担,提高数据传输速率和系统整体性能。 FPGA的优势在于可以灵活地集成多种接口IP核,包括高速物理I/O,能够满足高速通信需求。通过在FPGA内部构建SPI主控制器和从控制器,可以实现与多个SPI设备的并行通信,大大提高了系统的并行处理能力和吞吐量。同时,FPGA还可以动态调整SPI参数,如时钟频率、数据位宽等,以适应不同的外设需求。 在设计基于FPGA的SPI接口时,需要考虑以下几个关键点: 1. 时序设计:确保SPI时钟信号(SCLK)与数据传输的正确同步,避免数据丢失或错误。 2. 片选逻辑:设计适当的片选控制逻辑,以便在多从机环境中正确地选择和通信。 3. 数据缓冲区:为了实现并行通信,可能需要在FPGA内部设置数据缓冲区,以存储待发送或接收的数据。 4. 错误检测与校验:加入CRC(Cyclic Redundancy Check)或其他错误检测机制,确保数据传输的可靠性。 5. 配置灵活性:设计应允许用户通过配置寄存器来改变SPI接口的参数,如时钟极性和相位、数据顺序等。 6. 可扩展性:考虑到未来可能添加的新设备,接口设计应具备良好的可扩展性,允许轻松添加新的SPI从机接口。 基于FPGA的SPI通信接口设计是解决模块间接口问题的有效途径,它能够提供高效、灵活的通信解决方案,尤其适用于对实时性和性能要求较高的应用场景。通过利用FPGA的可编程优势,设计者可以创建出高度定制化的SPI接口,适应不断变化的系统需求,提升整体系统性能。

下载后可阅读完整内容,剩余3页未读,立即下载

- 粉丝: 4

- 资源: 975

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 深入理解23种设计模式

- 制作与调试:声控开关电路详解

- 腾讯2008年软件开发笔试题解析

- WebService开发指南:从入门到精通

- 栈数据结构实现的密码设置算法

- 提升逻辑与英语能力:揭秘IBM笔试核心词汇及题型

- SOPC技术探索:理论与实践

- 计算图中节点介数中心性的函数

- 电子元器件详解:电阻、电容、电感与传感器

- MIT经典:统计自然语言处理基础

- CMD命令大全详解与实用指南

- 数据结构复习重点:逻辑结构与存储结构

- ACM算法必读书籍推荐:权威指南与实战解析

- Ubuntu命令行与终端:从Shell到rxvt-unicode

- 深入理解VC_MFC编程:窗口、类、消息处理与绘图

- AT89S52单片机实现的温湿度智能检测与控制系统

信息提交成功

信息提交成功