Cyclone V器件DDR3接口详解

需积分: 50 117 浏览量

更新于2024-07-21

1

收藏 797KB PDF 举报

“altrea Cyclone V DDR3接口中文档提供了关于Cyclone V器件中DDR3 SDRAM等外部存储器接口的详细信息,包括软核和硬核控制器的支持标准、性能参数以及相关的设计资源。”

在Cyclone V系列 FPGA 中,外部存储器接口(EMIF)是一个关键特性,它使得器件能与各种外部存储器如DDR3 SDRAM进行高效通信。DDR3 SDRAM 是一种双倍数据速率同步动态随机存取存储器,以其高速度和低功耗而广泛应用于现代电子系统中。Cyclone V 器件不仅支持DDR3 SDRAM,还支持DDR2 SDRAM 和 LPDDR2 SDRAM,适应不同应用场景的需求。

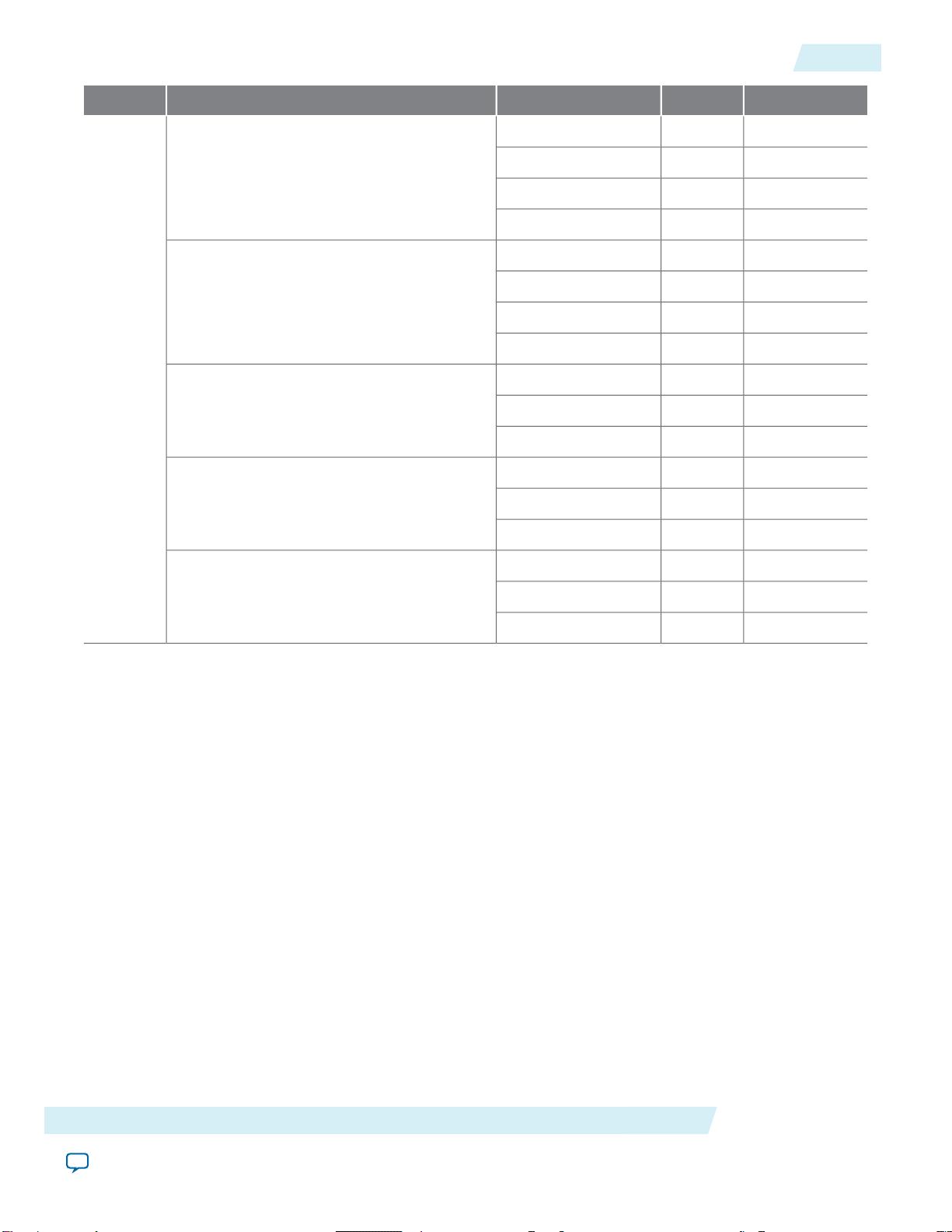

表6-1 显示了Cyclone V器件支持的外部存储器标准,包括半速率和全速率模式。这意味着用户可以根据应用需求选择合适的工作速度。对于DDR3 SDRAM,Cyclone V 支持1.5V和1.35V两种电压等级,这与DDR3 SDRAM的标准电压相符,有助于实现低功耗设计。

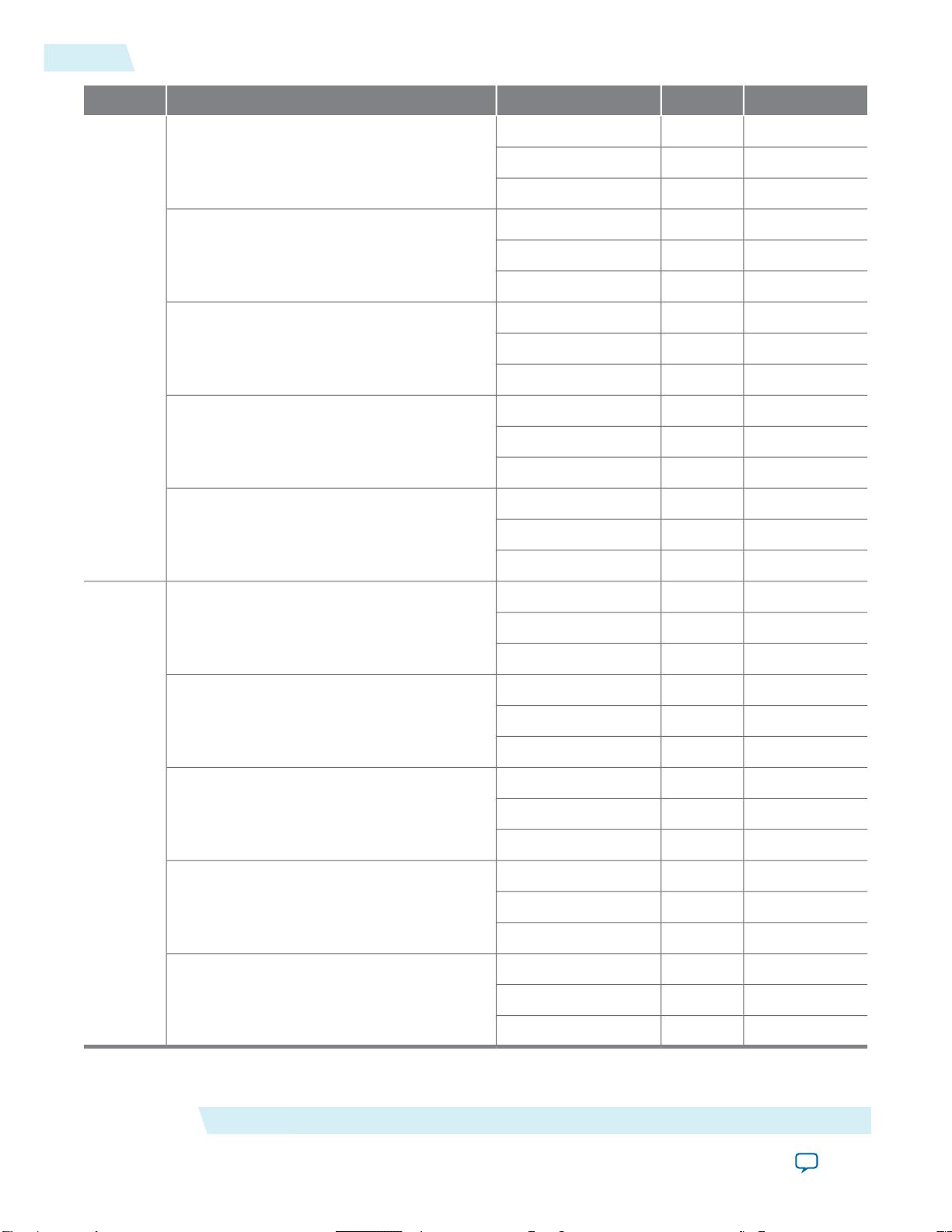

表6-2 提供了Cyclone V器件中外部存储器接口的性能指标。最大和最小操作频率取决于所选用的存储器接口标准以及器件数据表中列出的支持DLL(延迟锁相环)频率。例如,DDR3 SDRAM 的最大工作频率可以达到400MHz,最小工作频率则为300MHz,这些性能参数对于评估系统整体带宽至关重要。

为了帮助设计者优化存储器系统性能,Altera 提供了一些设计工具和资源,如外部存储器接口指标估算器,它可以帮助估算外部存储器系统的性能指标。此外,外部存储器接口手册提供了详细的存储器类型信息、电路板设计指导、时序分析、仿真和调试步骤。对于可能遇到的问题,Cyclone V器件手册的已知问题章节列出了对手册章节的更新和解决方案。

在设计过程中,考虑存储器接口的时序约束、电源管理、信号完整性和热管理是非常重要的。Cyclone V FPGA 的I/O bank 结构允许灵活的布线,以适应不同的外部存储器布局,同时保持高性能。设计师需要仔细阅读相关文档,理解存储器接口的时序要求,并结合DLL和PLL(锁相环路)来正确配置接口。

Cyclone V DDR3 接口提供了强大的外部存储器连接能力,通过软核和硬核控制器支持多种存储器标准,且具备出色的性能指标。设计人员可以通过利用Altera提供的工具和文档,确保其设计满足系统性能需求,同时优化功耗和成本。

119 浏览量

点击了解资源详情

点击了解资源详情

2010-03-08 上传

239 浏览量

2025-03-13 上传

2025-03-13 上传

qq_31327349

- 粉丝: 0

最新资源

- Vue.js波纹效果组件:Vue-Touch-Ripple使用教程

- VHDL与Verilog代码转换实用工具介绍

- 探索Android AppCompat库:兼容性支持与Java编程

- 探索Swift中的WBLoadingIndicatorView动画封装技术

- dwz后台实例:全面展示dwz控件使用方法

- FoodCMS: 一站式食品信息和搜索解决方案

- 光立方制作教程:雨滴特效与呼吸灯效果

- mybatisTool高效代码生成工具包发布

- Android Graphics 绘图技巧与实践解析

- 1998版GMP自检评定标准的回顾与方法

- 阻容参数快速计算工具-硬件设计计算器

- 基于Java和MySQL的通讯录管理系统开发教程

- 基于JSP和JavaBean的学生选课系统实现

- 全面的数字电路基础大学课件介绍

- WagtailClassSetter停更:Hallo.js编辑器类设置器使用指南

- PCB线路板电镀槽尺寸核算方法详解