Modelsim与Quartus II合作验证CPU设计:优化仿真流程

版权申诉

134 浏览量

更新于2024-07-07

收藏 524KB DOC 举报

本实验报告主要围绕"Modelsim仿真风险及CPU验证"展开,针对的是计算机硬件设计中的一个关键环节——CPU验证。实验目标是使用Modelsim软件对一个自定义的CPU设计进行测试,该CPU包含存放器、计数器、存储器、多路选择器、时序控制和算术逻辑单元(Alu)等多个子模块。实验工具选择Quartus II和Modelsim的协同工作,这是因为Quartus II专长于处理大型FPGA项目,而Modelsim在处理复杂代码和外部测试文件时效率较低,但其强大的仿真功能对于调试逻辑设计非常关键。

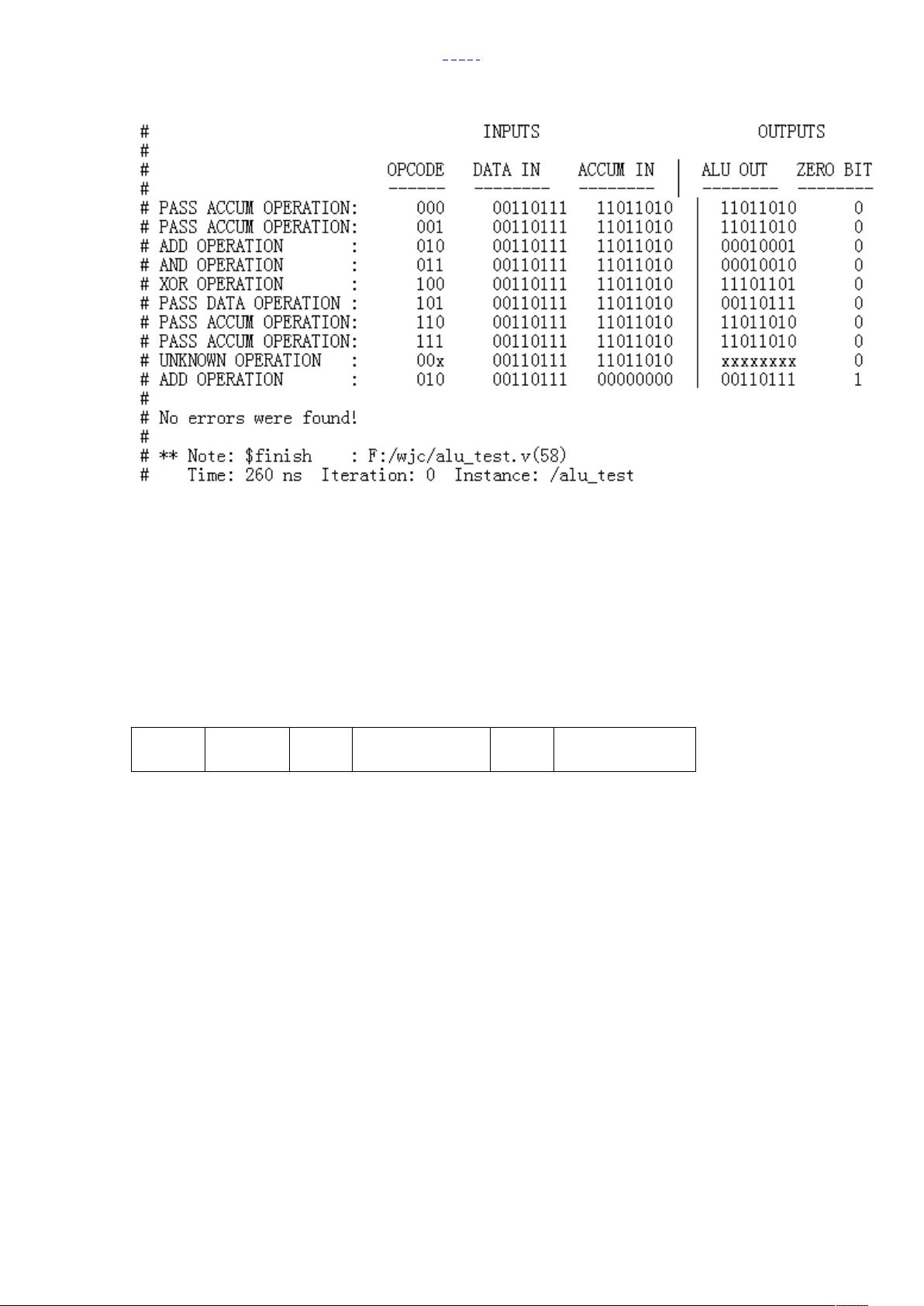

首先,实验的重点是Alu模块的设计和验证。Alu是一个组合逻辑模块,它接受四个输入:操作码(opcode)、数据(data)、累加器(accum)以及零标志位(zero)。操作码为3位,具有多种功能,如加法、与非、异或和数据保持等。其中,当操作码为011时执行ADD操作,其余操作码对应不同的逻辑运算。特别值得注意的是,当累加器变化时,零标志位会有1.2ns的延迟更新,这对于理解和调试ALU的正确性至关重要。

设计过程使用了SystemVerilog语言,其中`timescale1ns/100ps`语句设置了时间尺度,表明仿真将以1纳秒为单位,每100皮秒为一个仿真步。模块定义部分包括了输入和输出端口,以及alu_out、zero、opcode和data、accum等信号的声明。

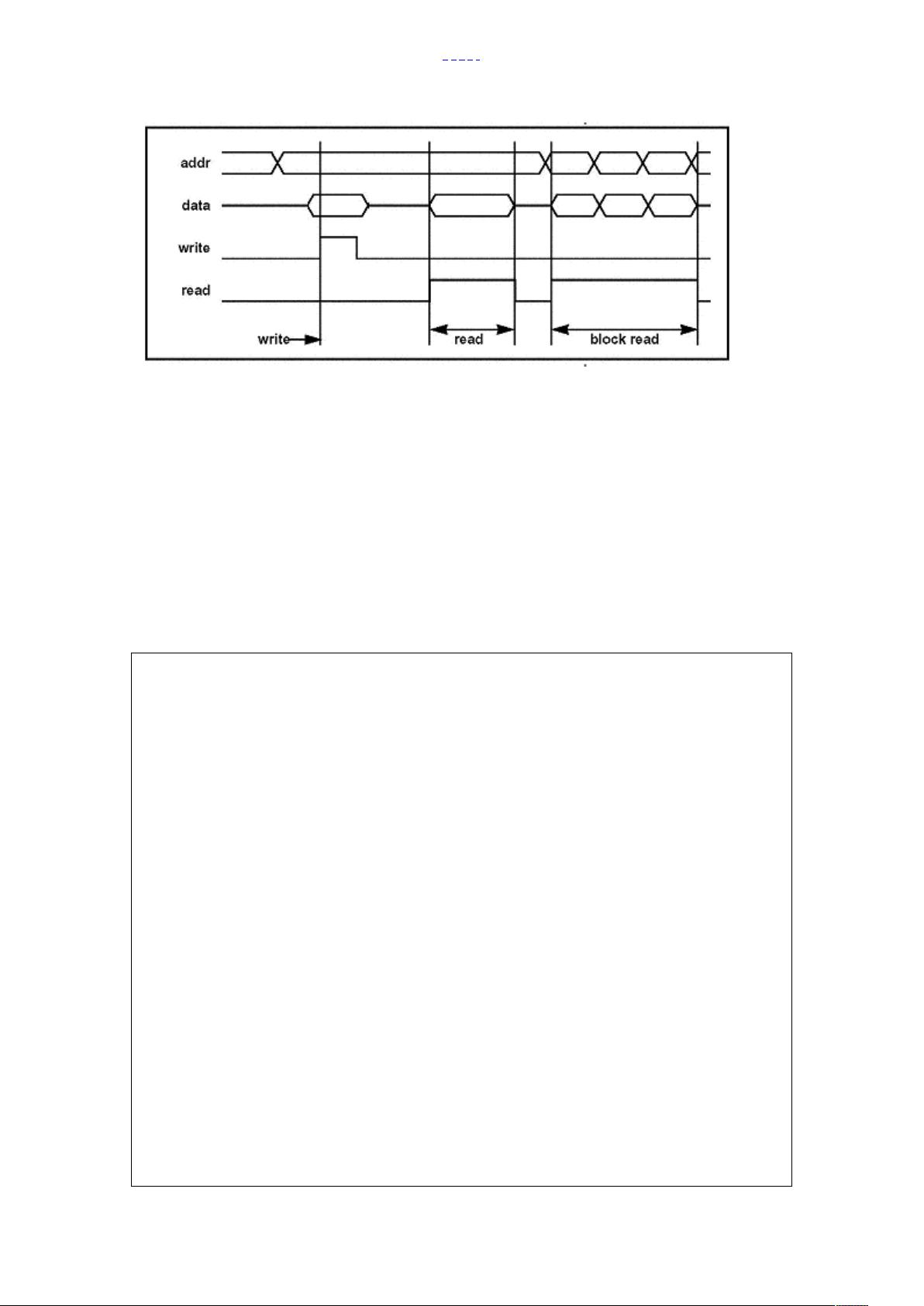

在实验步骤中,首先会利用Quartus II进行整体工程管理,编写并编译包含Alu在内的CPU模块代码,然后在Quartus II中通过.bdf文件进行模块连接或.v文件中实例化。在Modelsim中,模型被导入到Quartus II的环境中,通过写入诊断程序作为激励信号,来测试CPU的各个子模块的功能。由于Modelsim的长响应时间和初始化速度问题,结合使用两个工具可以在仿真过程中实现更高效的性能优化。

最后,实验中会利用Quartus II自带的逻辑分析仪进行初步的波形仿真和校验,确保设计的准确性。整个过程体现了现代硬件设计中对于仿真工具的充分利用,以提高设计质量和效率。

通过这次实验,学生不仅能够掌握集成电路原理和设计的基础知识,还能学习如何在实际工程中有效地运用Modelsim进行系统级的验证,提升硬件设计的实践能力。

2021-10-03 上传

2021-10-12 上传

2023-06-22 上传

2021-08-28 上传

2021-10-03 上传

2019-08-06 上传

2019-05-23 上传