高速电路信号完整性分析:反射与串扰的解析与IBIS仿真

下载需积分: 1 | DOC格式 | 382KB |

更新于2024-09-08

| 192 浏览量 | 举报

"高速电路信号完整性分析"

在高速电路设计中,信号完整性是一个至关重要的概念,它关乎着电路能否正常、高效地传输数据。信号完整性问题通常由多种因素引起,包括反射、串扰、振铃和地弹等。随着电子设备工作频率的不断提升,这些问题对系统性能的影响越来越大。

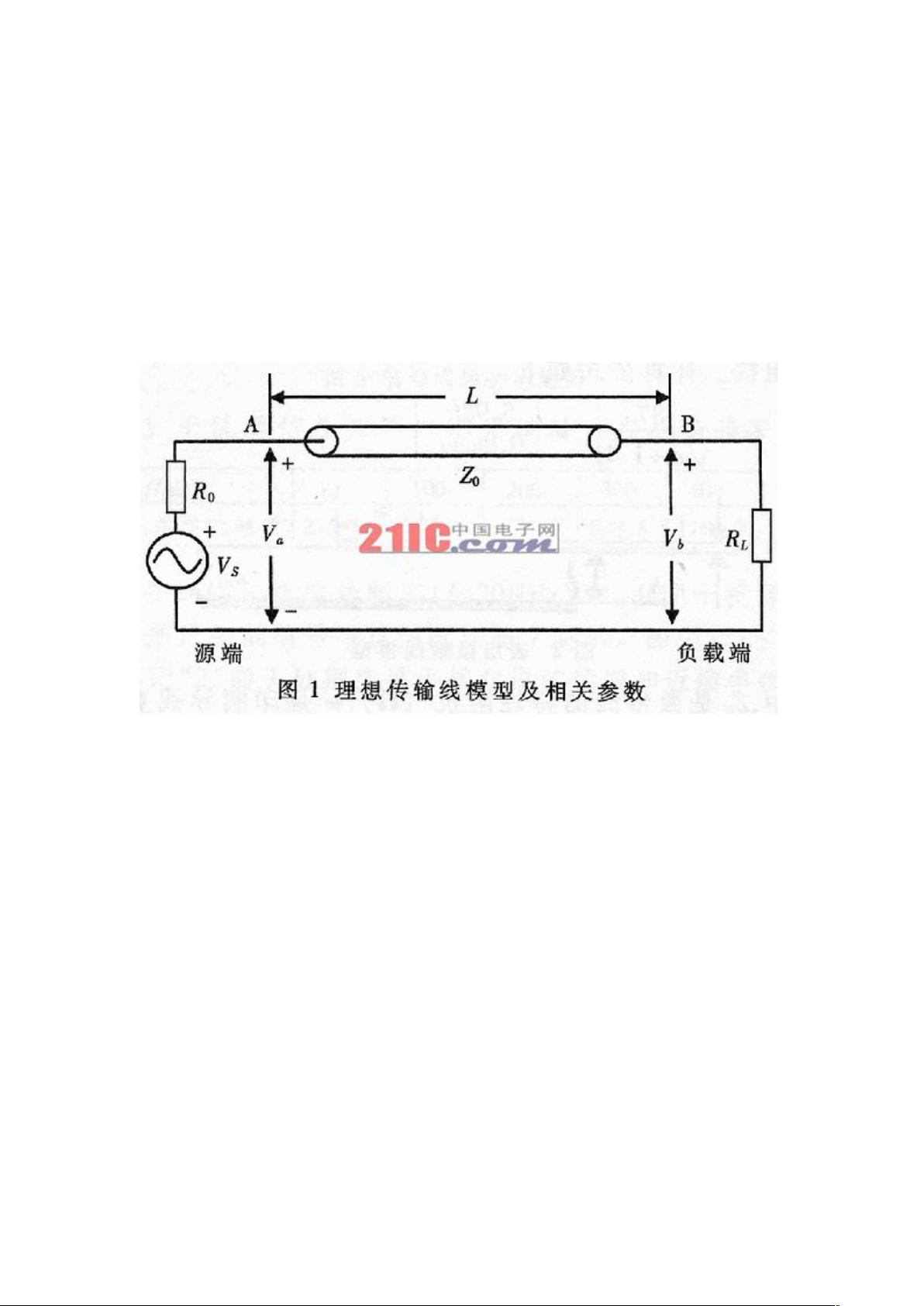

反射是由于传输线上的阻抗不连续性导致的,当信号源与负载之间的阻抗不匹配时,部分电压会反射回去。负载反射系数ρL和源反射系数ρs可以通过公式(1)和(2)计算,这两个系数决定了反射电压的大小。传输线的特性阻抗Z0是一个关键参数,它受到印制线的电阻、电容和电感,以及在高频下的超肤效应和电介质损耗等因素的影响。微带线和带状线是高速PCB设计中常见的两种传输线类型,它们的特性阻抗计算需要考虑这些因素。

微带线是印制在接地层之上,由电介质隔开的导线。它的特性阻抗取决于导线的宽度W、厚度t、电介质的相对介电常数εr以及导线与接地层之间的距离h。通过这些参数,可以使用微波工程中的公式来计算微带线的特性阻抗。

串扰是相邻信号线之间的耦合效应,当一条信号线上的电压变化时,会在邻近的信号线上产生干扰电压。高速PCB设计中,为了避免串扰,需要考虑信号线之间的间距、信号的上升时间以及线路的屏蔽措施。

为了分析和解决高速电路的信号完整性问题,工程师常常采用仿真工具,如IBIS (Input/Output Buffer Information Specification) 模型。IBIS提供了一种标准的模型格式,用于描述集成电路的输入输出行为,包括信号的上升时间、下降时间和电流驱动能力等。通过IBIS模型,设计师可以在早期设计阶段进行信号完整性仿真,预测并优化电路性能,避免在实际制造后出现信号完整性问题。

高速电路信号完整性分析涉及多个层面,包括理论计算、仿真工具的使用以及对传输线特性的深入理解。在设计高速PCB时,确保信号完整性需要综合考虑电路的物理布局、材料属性以及信号传输的动态特性,通过精确计算和仿真来优化设计,确保电路能够无误地高速传输数据。

相关推荐

yaoge212012

- 粉丝: 0

最新资源

- Visual Studio 2008:十大革新特性,包括LINQ和代码段编辑器

- CMPP2.0短信网关接口开发详解:协议结构与消息定义

- InfoQ出品:免费在线《深入浅出Struts2》教程

- Windows服务器2003数字证书与PKI实战指南

- C++TEST中文文档:代码标准分析和单元测试报告

- JS表单验证技巧集:字符限制、字符类型检测

- 一键式解决Java桌面应用的部署难题

- Android程序设计大赛I:20佳获奖作品展示与创新应用解析

- Oracle DBA基础教程:从开机到管理全记录

- 《人件》:软件工程中的人的因素与团队生产力

- 全球移动通信系统GSM:原理与频段解析

- 《Linux内核0.11完全注释》:深入理解操作系统核心

- 浅析计算机键盘构造与PS/2接口原理详解

- SIMATIC S7-300编程手册:STL指令详解

- Visual Source Safe (VSS) 在软件开发中的应用

- Java命令参数详解:从基础到扩展