嵌入式技术工程法课件:Verilog HDL电路设计及实例详解

版权申诉

170 浏览量

更新于2024-04-03

收藏 1.24MB PPT 举报

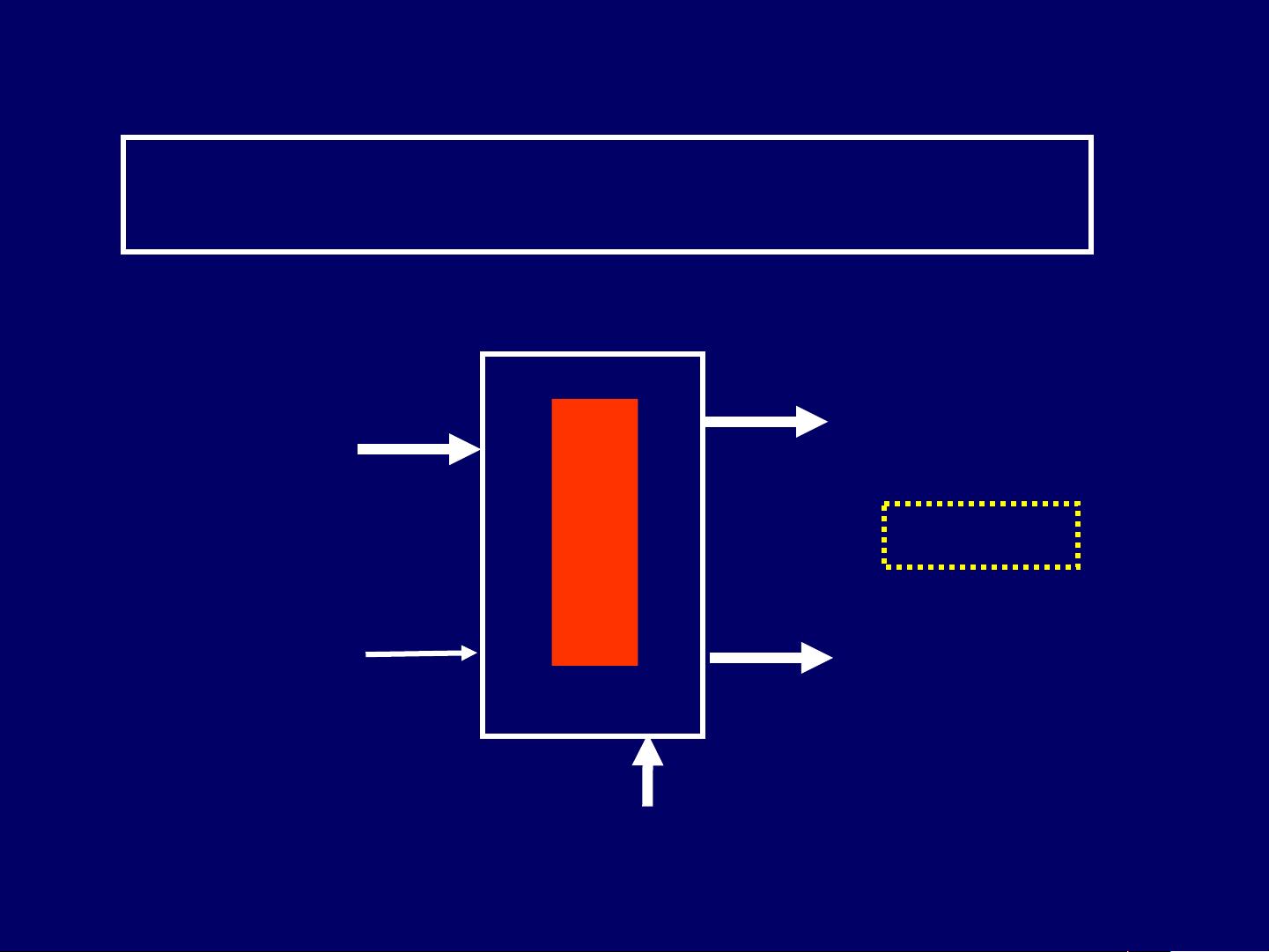

"基于Verilog HDL的电路设计是嵌入式技术的重要组成部分,通过课程第二章的学习,我们可以掌握典型的组合电路设计实例、时序电路设计实例以及基于有限状态机的设计方法。在典型组合电路设计实例部分,我们学习了译码器的原理和实现方法。译码器是一种常见的电路组件,可以实现将输入信号转换为一定数量的输出信号。通过Verilog HDL编程,我们可以轻松实现译码器的设计,包括高有效使能和高有效输出的设计。例如,我们可以编写Verilog代码实现一个2 - 4译码器,通过输入信号的不同组合实现不同的输出信号。在实际应用中,译码器可以被广泛应用于数字电路中,提高系统的灵活性和可扩展性。

在典型时序电路设计实例部分,我们学习了时序电路的设计原理和实现方法。时序电路是一种需要考虑信号传输时间和顺序的电路,通过Verilog HDL编程可以更加精确地控制时序电路的设计。通过学习典型时序电路设计实例,我们可以掌握时序逻辑电路的设计技巧,包括时钟信号的同步和异步处理、时序约束的设置等。时序电路在数字系统中具有重要作用,可以实现数据的精确处理和同步传输,保证系统的正确运行和稳定性。

在基于有限状态机的设计方法综述部分,我们学习了有限状态机的原理和设计方法。有限状态机是一种描述系统状态和状态转移的数学模型,通过Verilog HDL编程可以方便地实现有限状态机的设计。有限状态机在数字电路中被广泛应用,可以实现复杂的控制和逻辑功能。通过学习有限状态机的设计方法,我们可以更好地理解系统行为和控制流程,提高系统的可靠性和性能。

在实用电路设计举例部分,我们可以通过具体案例学习Verilog HDL的应用和技巧。通过实际的电路设计案例,我们可以更加深入地理解Verilog HDL的语法和编程规范,提高代码的可读性和可维护性。通过实用电路设计举例的学习,我们可以积累丰富的实践经验,为今后的电路设计工作奠定坚实基础。

综上所述,基于Verilog HDL的电路设计是嵌入式技术领域中的重要内容,通过学习第二章的课件,我们可以掌握丰富的电路设计技巧和方法。在实际工作中,我们可以运用所学知识设计和实现各类数字电路,提高系统的性能和稳定性,推动嵌入式技术的发展与应用。"

2022-06-22 上传

1202 浏览量

2022-06-22 上传

2021-09-21 上传

2022-06-17 上传

智慧安全方案

- 粉丝: 3849

- 资源: 59万+

最新资源

- 高质量C/C++编程指南(作者:林锐博士,PDF完整版)

- PHP中的代码安全和SQL Injection防范3

- PHP中的代码安全和SQL Injection防范2

- PHP中的代码安全和SQL Injection防范1

- 51单片机指令系统,方便查阅

- 高级Bash脚本编程指南

- 升级PHP5的理由:PHP4和PHP5性能大对比

- oracle常用命令

- PHP上传文件涉及到的参数

- SymtemC user guide

- 联想内部独家资料windows XP 各个文件夹详细介绍.pdf

- VFP的功能及特点.ppt

- Windows 2008中文版安装实录.doc

- Spring开发指南

- Java Script 高端程序设计(精华).pdf

- 第6章 ASP.NET与XML讲解 C#