基于FPGA的FIR滤波器设计实现

版权申诉

165 浏览量

更新于2024-06-26

收藏 1.75MB PDF 举报

"基于FPGA的FIR滤波器设计"

**FPGA的FIR滤波器设计**

**设计目的**

本设计的目的是为了帮助学生深入理解和消化基本理论,并进一步提高综合应用能力和独立解决问题的能力。通过本设计,学生将学习如何使用FPGA来完成FIR滤波器的设计、程序设计和实验调试任务。

**设计要求**

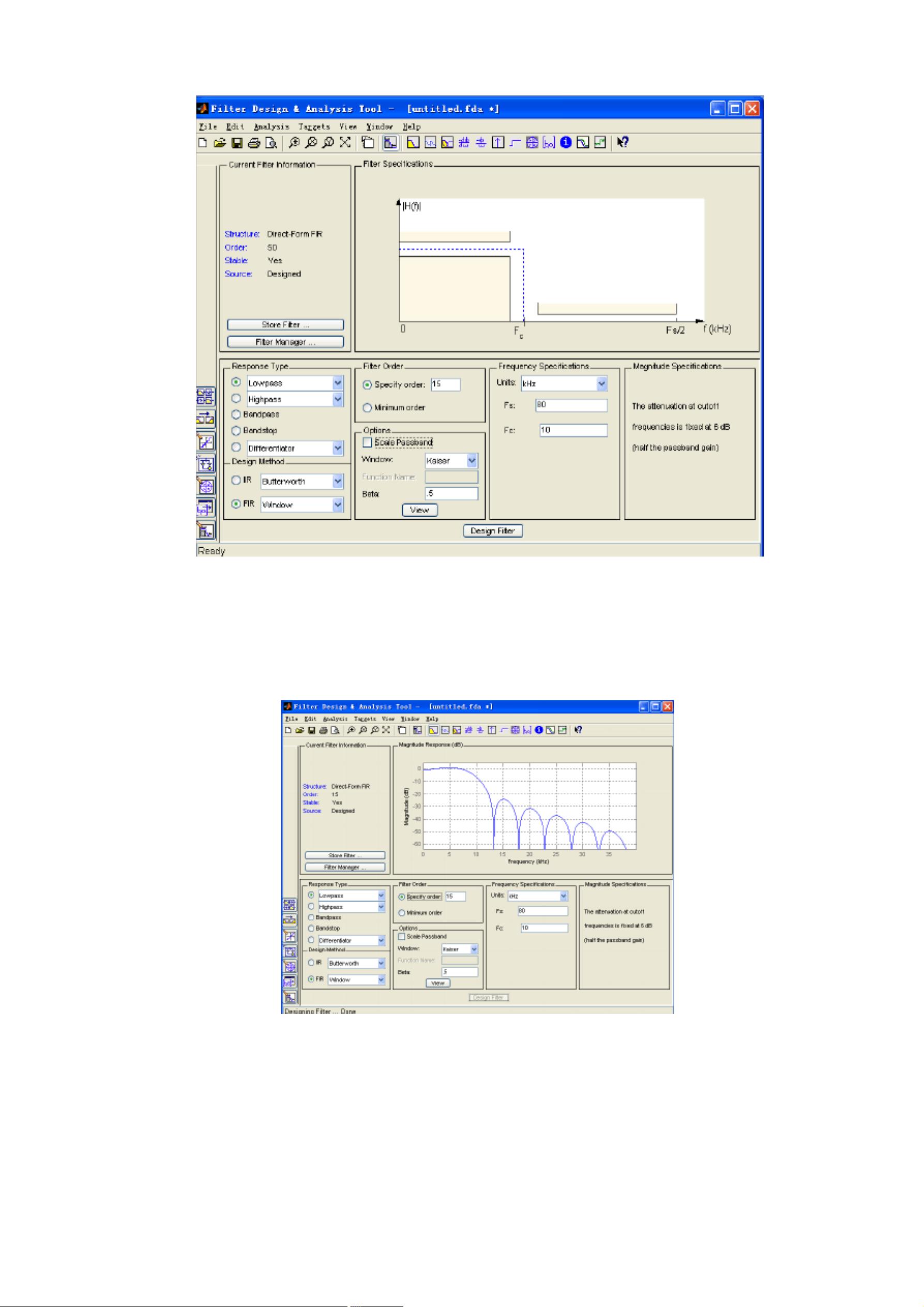

本设计的基本要求是利用所学知识,采用VHDL语言完成FIR滤波器的设计仿真。具体设计指标如下:

1. 采样频率Fs = 80KHz

2. 截止频率Fc = 10KHz

3. 输入序列为10位(最高位为符号位)

4. 窗口类型为kaiser窗,β = 0.5

5. 滤波器长度为16

6. 输出结果保留10位

**提高部分**

根据所学知识,设计出一个具有频率控制功能DDS,要求输出频率分别为10KHz和100KHz,将输出的两路数字信号进行叠加,并通过所设计的FIR滤波器进行滤波,将滤波输出的数字信号通过D/A转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

**设计原理**

**FIR滤波器**

FIR滤波器是根据线性系统理论设计的。线性系统理论表明,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

**线性FIR滤波器原理**

FIR滤波器响应(简称FIR)系统的单位脉冲响应h(n)为有限长序列,系统函数H(z)在有限z平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。如果h(n)的长度为N,则它的系统函数和差分方程一般具有如下形式:

H(z) = ∑h(n)z^-n

n = 0

N-1

y(n) = ∑h(m)x(n-m)

m = 0

根据差分方程直接画出FIR滤波器的结构图。

**FPGA的应用**

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,能够根据需要进行配置和编程。FPGA在数字信号处理领域中的应用非常广泛,特别是在实现FIR滤波器时,FPGA可以提供高速、灵活和可靠的解决方案。

**VHDL语言**

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统的行为。VHDL语言可以用于描述FPGA的设计,实现FIR滤波器的设计和仿真。

**MATLAB和QUARTUS II**

MATLAB是一种高级数学软件,能够用于仿真和分析数字信号处理系统。QUARTUS II是一种FPGA开发工具,能够用于设计、仿真和实现FPGA系统。在本设计中,我们将使用MATLAB和QUARTUS II来仿真和实现FIR滤波器的设计。

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2019-09-05 上传

hhappy0123456789

- 粉丝: 77

- 资源: 5万+

最新资源

- training-github-actions:一个可以与github动作一起玩的仓库

- EscapeRoom

- 华为简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 行业分类-设备装置-跨虚拟化平台迁移虚拟机的方法和装置.zip

- tapwizard.github.io:包含TAPBuilds中的自定义版本的向导

- codeGenerationCompared:Java regex Groovy ANTLR 代码生成对比

- qq-tabbar-drag:qq的tabbar拖动动画效果

- 投影价值应用

- 【WordPress插件】2022年最新版完整功能demo+插件v1.4.5.zip

- 数据结构(C语言版)(第2版)_PPT课件.rar

- 疯狂java2源码-javaBook:java各种电子书籍

- package-booking-backend

- SharePoint 2013客户端渲染:列表表单和布局

- 100-days-of-code-in-python:Angela Yu的课程涵盖了完整的Python PRO Bootcamp,其中包含100个项目,每天有2个小时的课程。 该存储库将包含所有相关的Project作品。 快乐编码!

- 设计模式大作业.zip

- gamergain-android-sdk