掌握TimeQuest:FPGA设计中的静态时序分析利器

需积分: 10 69 浏览量

更新于2024-07-27

收藏 3.39MB PDF 举报

"Riple的TimeQuest学习笔记,讲解了TimeQuest在FPGA设计中的重要性和使用技巧,对比了TimeQuest与Timing Analyzer的功能差异,并介绍了TimeQuest采用的Synopsys Design Constraints (SDC)文件格式的优势。"

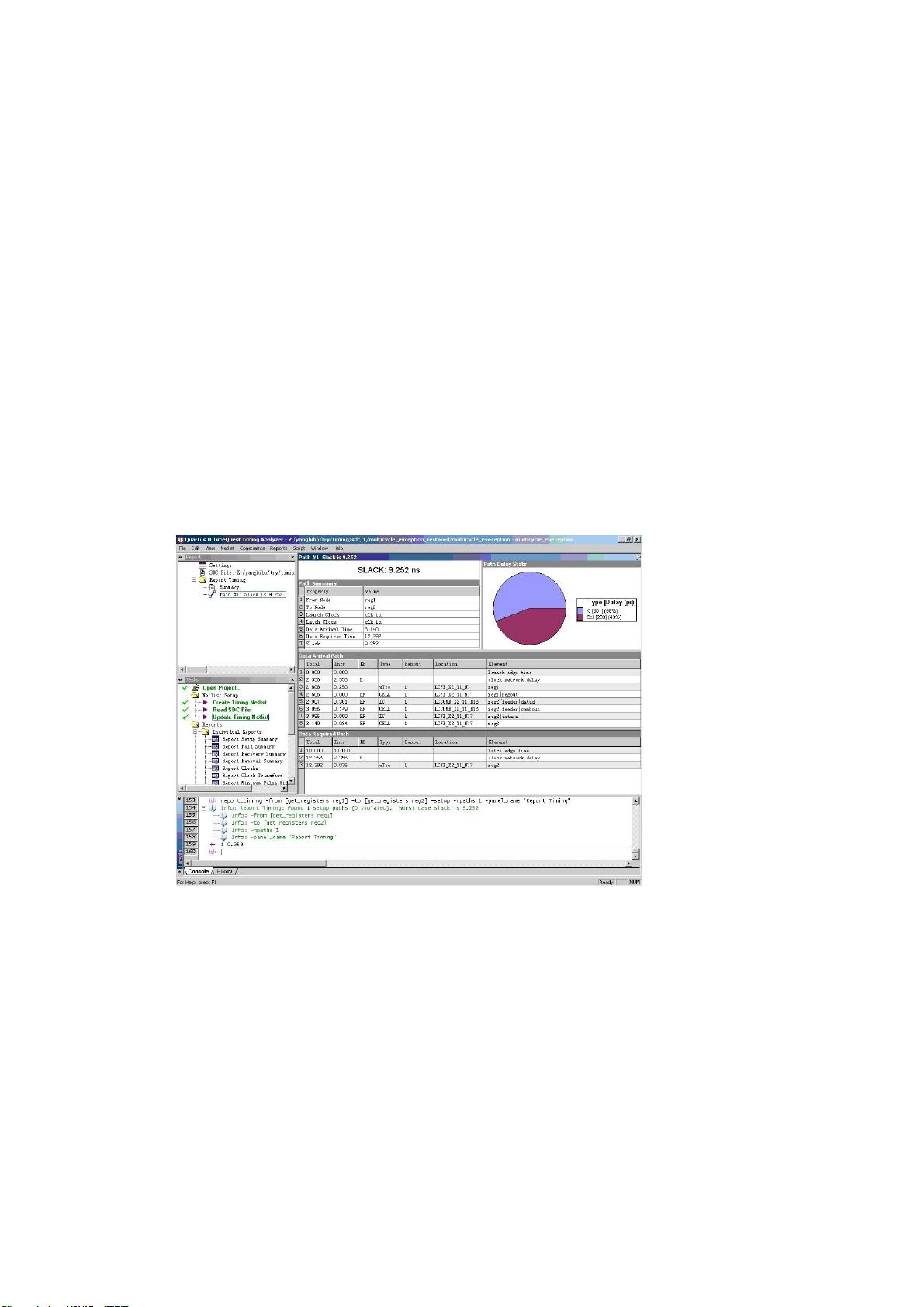

在FPGA设计中,确保时序正确性是至关重要的,因为这直接影响到设计的性能和稳定性。TimeQuest是Altera在6.0版本中引入的一款静态时序分析工具,它借鉴了ASIC设计中的方法,提供了比Timing Analyzer更强大的功能和用户友好的界面,使设计师能够更深入地进行时序约束和结果分析。

TimeQuest的一个显著特点是它使用Synopsys Design Constraints (SDC)文件格式进行时序约束,这是业界广泛接受的标准,相比Timing Analyzer的Quartus Settings File (QSF),SDC允许更灵活、更精细的约束设置,同时也方便了设计从FPGA向ASIC的转换。这种通用性使得设计者可以更轻松地在不同的设计流程中应用相同的约束,提高了设计的可移植性。

在学习和使用TimeQuest时,理解基本的时序概念是基础。时序分析主要关注的是信号从输入到输出的延迟,以及系统能否在规定的时间内完成所有操作。在FPGA设计中,通常的目标是达到最大的工作频率(Fmax),这需要对时钟路径、组合逻辑路径和各种时序边界的精确控制。TimeQuest能够帮助设计者识别关键路径,优化布局布线,确保设计满足时序要求。

通过TimeQuest,设计者可以设置多种类型的时序约束,如最大延迟约束(setup和hold)、时钟树约束、时钟偏移约束等。这些约束可以指导编译过程,使综合和布局布线工具能更好地优化设计,从而达到最佳的性能表现。同时,TimeQuest的报告功能可以帮助设计者分析时序违规,找出性能瓶颈,进行针对性的改进。

在实际使用中,可能会遇到各种问题,比如不正确的时序约束设置、时序违规或者难以理解的分析结果。Riple在博客中计划分享的学习内容将涵盖这些挑战,包括如何创建有效的时序约束,如何解析TimeQuest的报告,以及如何解决时序问题。这不仅对初学者有极大的帮助,也能促进经验丰富的设计者进一步提升他们的设计技能。

掌握TimeQuest的使用对于提升FPGA设计的质量和效率至关重要。通过深入理解和实践,设计者可以更好地利用TimeQuest来优化他们的设计,实现更高效、更可靠的工作流程。

2021-04-02 上传

2021-03-13 上传

2010-04-11 上传

2021-03-29 上传

2015-10-08 上传

fresird

- 粉丝: 0

- 资源: 2

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍