FPGA设计: DDR存储器接口时序优化关键

需积分: 50 16 浏览量

更新于2024-09-12

收藏 181KB DOC 举报

"成功解决FPGA设计时序问题的三大要点"

在FPGA设计中,时序问题至关重要,尤其是在高速接口技术的应用下。当工作频率超过200兆赫兹时,时序分析变得尤为关键,因为它能帮助识别并解决可能导致系统故障的问题。设计师需要创建并精确控制时序空余,即在数据采集和演示窗口之间留出最小的间隔,以确保数据传输的准确性。同时,随着边缘速率的提高,物理设计的影响也会被放大,这可能导致信号完整性问题,需要更长的沉降时间和更精细的时序管理。

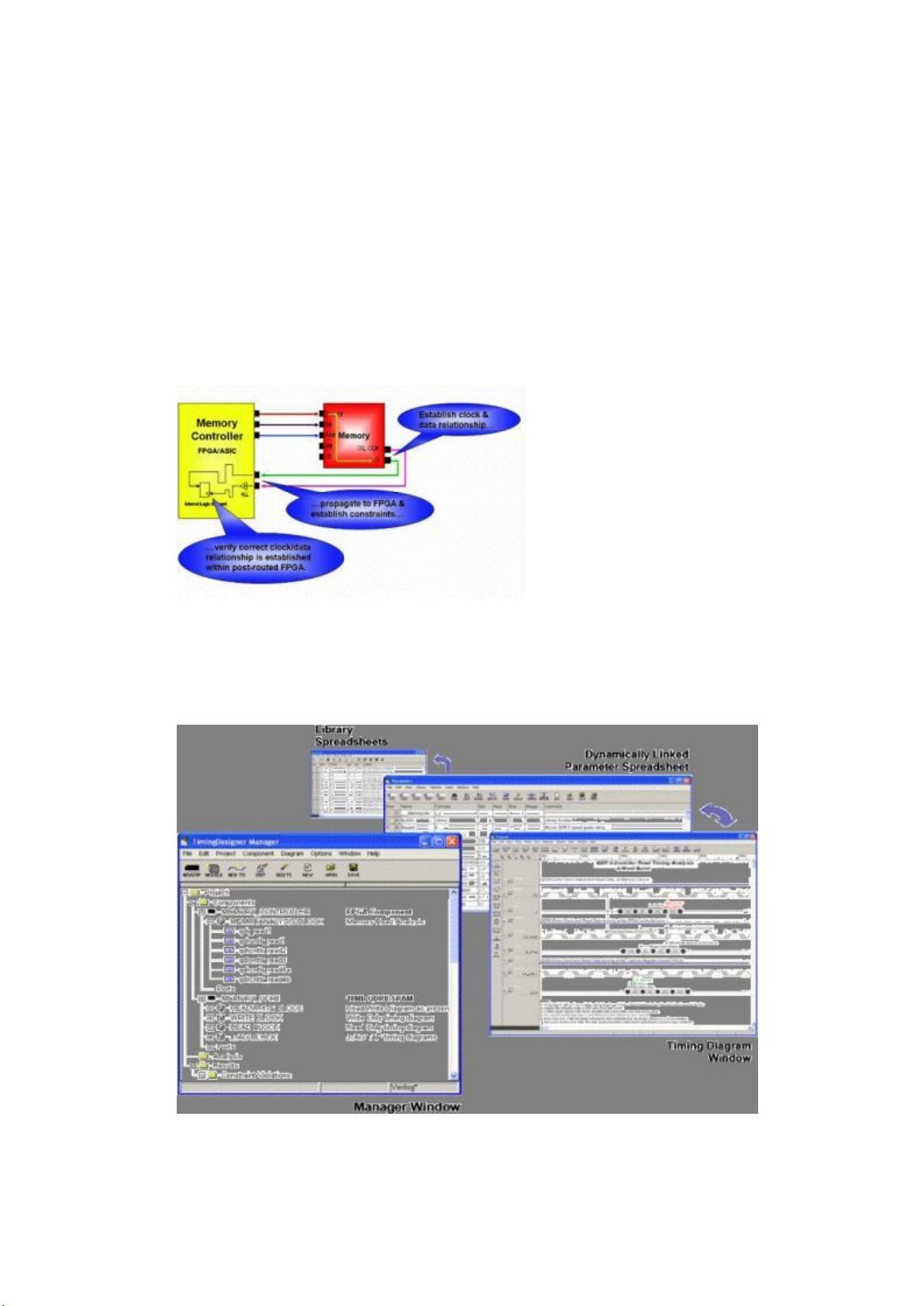

FPGA器件的高级特性,如支持DDR(双倍数据速率)和PLL(锁相环)网络,为设计者提供了更复杂的接口模块和精确的时钟控制。DDR/QDR存储器接口允许数据在时钟的上升沿和下降沿同时传输,因此需要精确的时钟偏移调整,以保证正确的时钟与数据关系。在设计中,通过I/O单元接口和PLL网络,可以实现对存储器接口的精确控制。

TimingDesigner等软件工具提供了可视化的界面,帮助设计师捕捉和分析设计的关键特性。这些工具在处理DDR/QDR存储器接口时特别有用,因为它们能够帮助调整时钟中心,确保数据在正确的时间窗口内被正确捕获。例如,在QDRII SRAM源同步接口设计中,数据相位需要旋转90度以与时钟同步,这通常通过调整时钟信号的中心位置来实现。

在同步存储器系统中,中心对齐的时钟与数据关系可以最大化满足建立和保持时序的要求。然而,实际设计中,由于温度变化和其他因素的影响,可能需要微调时钟信号以避免破坏时序约束。通过适当的时钟延迟,可以实现数据采集的中心对齐,确保在各种条件下都能满足时序要求。

解决FPGA设计时序问题的三大要点包括:理解并应用时序分析以识别潜在问题,掌握并利用先进的FPGA特性如DDR接口和PLL网络,以及有效地使用设计工具如TimingDesigner来优化时序管理。遵循这些要点,设计师能够确保FPGA设计在高速数据传输环境下稳定且高效地运行。

795 浏览量

1695 浏览量

421 浏览量

108 浏览量

238 浏览量

2025-01-11 上传

2024-11-10 上传

2024-11-07 上传

2024-11-07 上传

鬼谷清泉

- 粉丝: 5

最新资源

- 深入解析JavaWeb中Servlet、Jsp与JDBC技术

- 粒子滤波在视频目标跟踪中的应用与MATLAB实现

- ISTQB ISEB基础级认证考试BH0-010题库解析

- 深入探讨HTML技术在hundeakademie中的应用

- Delphi实现EXE/DLL文件PE头修改技术

- 光线追踪:探索反射与折射模型的奥秘

- 构建http接口以返回json格式,使用SpringMVC+MyBatis+Oracle

- 文件驱动程序示例:实现缓存区读写操作

- JavaScript顶盒技术开发与应用

- 掌握PLSQL: 从语法到数据库对象的全面解析

- MP4v2在iOS平台上的应用与编译指南

- 探索Chrome与Google Cardboard的WebGL基础VR实验

- Windows平台下的IOMeter性能测试工具使用指南

- 激光切割板材表面质量研究综述

- 西门子200编程电缆PPI驱动程序下载及使用指南

- Pablo的编程笔记与机器学习项目探索