Verilog经典教材:ASIC/FPGA设计中的数字信号处理与逻辑设计

需积分: 50 61 浏览量

更新于2024-07-22

1

收藏 1.73MB PDF 举报

Verilog经典教材深入探讨了数字逻辑设计在当今电子工程领域的核心地位。随着ASIC和FPGA技术的发展,设计复杂的电路系统变得越来越依赖于标准化的描述语言和模块化设计方法。Verilog作为一种工业标准,为逻辑设计提供了统一的框架,使得设计者可以专注于算法和功能的实现,而将底层的硬件实现留给专门的工具和工艺技术。

章节一开篇,教材介绍了数字信号处理的基础概念,包括滤波、变换、加密等操作,这些本质上是数学运算,可以通过编程语言如C、Pascal或汇编语言来实现。然而,对于实时性要求极高的应用,比如军用无线通信和雷达系统,通用计算机的性能无法满足快速处理和加密解密的需求,因此,专用硬件设计,如硬线逻辑电路、FPGA和ASIC,显得尤为重要。

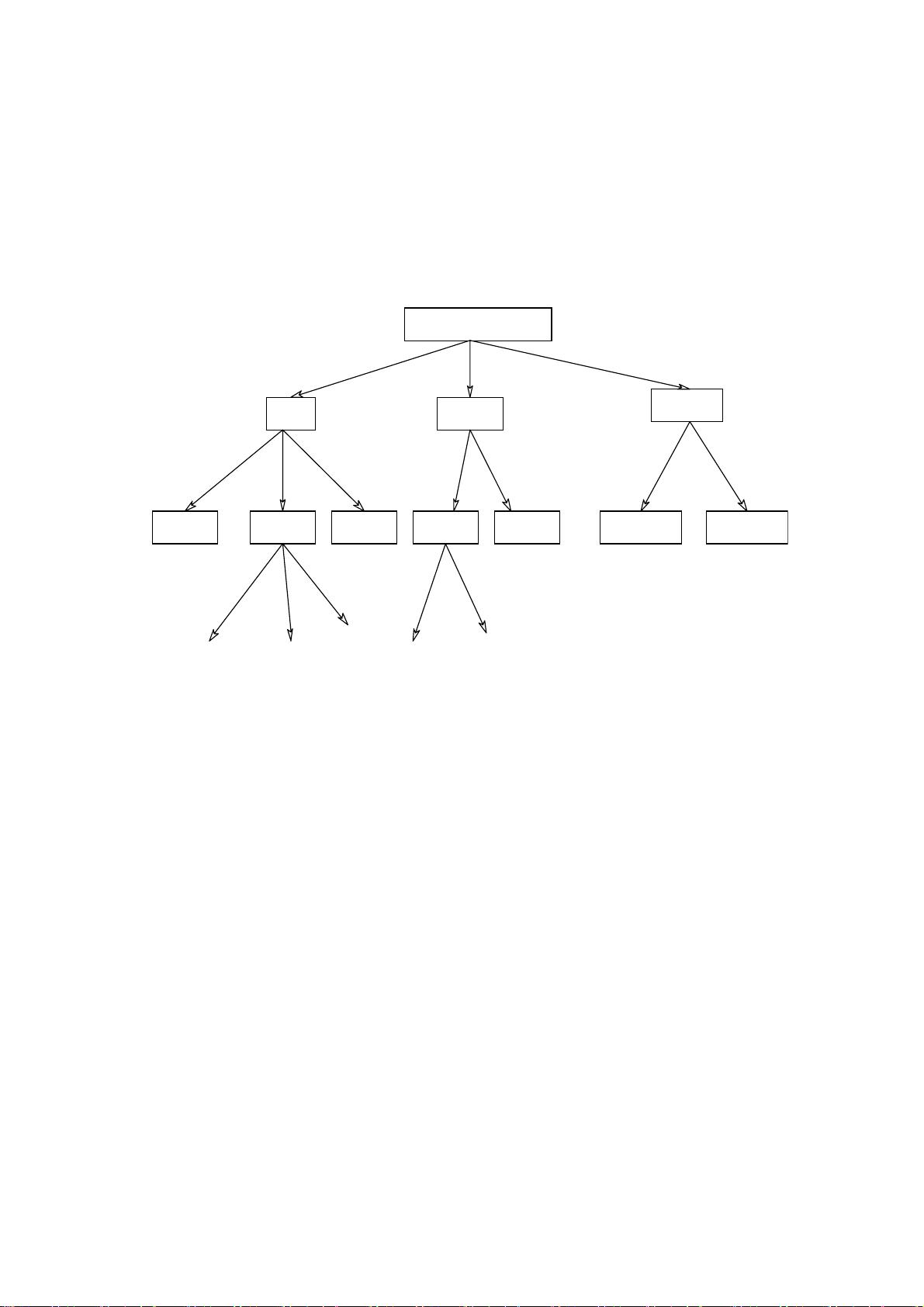

在硬线逻辑设计中,设计师可以构建宏单元或软核库,将常见的逻辑电路和系统组件标准化,如FFT和DCT算法,以提高效率并减少重复劳动。这样的模块化设计使得不同领域的专家能够共享和复用这些组件,加速了系统开发进程。

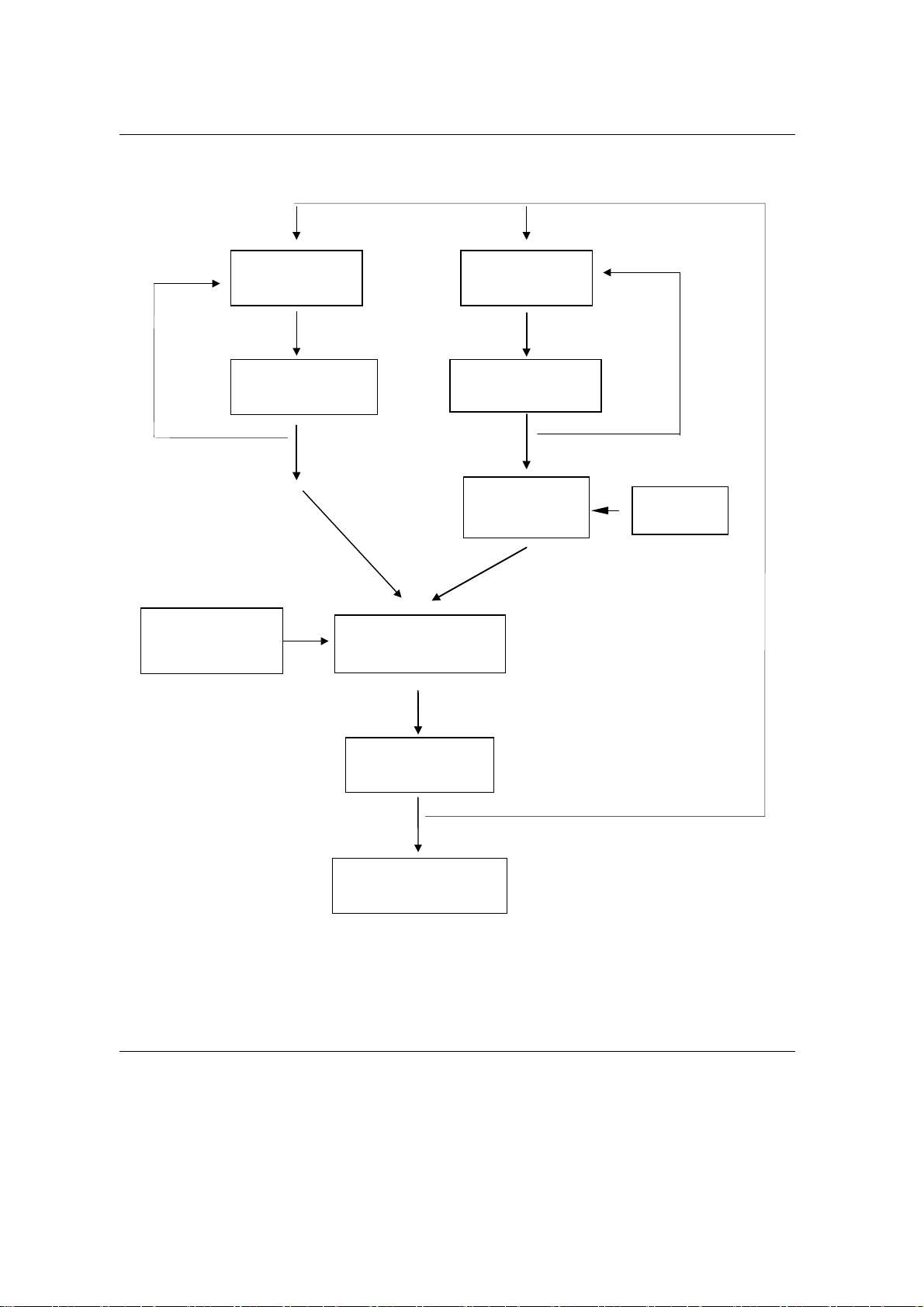

通用微处理器,如Cortex系列,虽然强大,但其执行机制决定了其在处理实时信号处理任务时可能存在瓶颈。微处理器需要通过编译器转换成机器码,再由时钟驱动执行,这对于速度敏感的应用来说并不理想。相比之下,FPGA和ASIC能够提供定制化的硬件结构,能直接映射算法,实现低延迟、高带宽的信号处理,是实时信号处理的理想选择。

总结来说,Verilog经典教材强调了在数字逻辑设计中,尤其是在实时信号处理领域,理解和掌握Verilog语言的重要性,以及如何通过模块化、标准化的设计方法,结合专用硬件来应对不断提高的复杂度和性能需求。同时,它也揭示了在快速发展的电子工程行业中,逻辑设计与电路实现之间的分工协作,以及如何通过技术创新来提升整体系统的效能。

2012-04-04 上传

2019-03-18 上传

2019-09-05 上传

2020-04-04 上传

qq_25996441

- 粉丝: 0

- 资源: 1

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载