"基于51单片机的数字频率合成设计与实现"

需积分: 0 145 浏览量

更新于2024-03-11

收藏 3.16MB DOC 举报

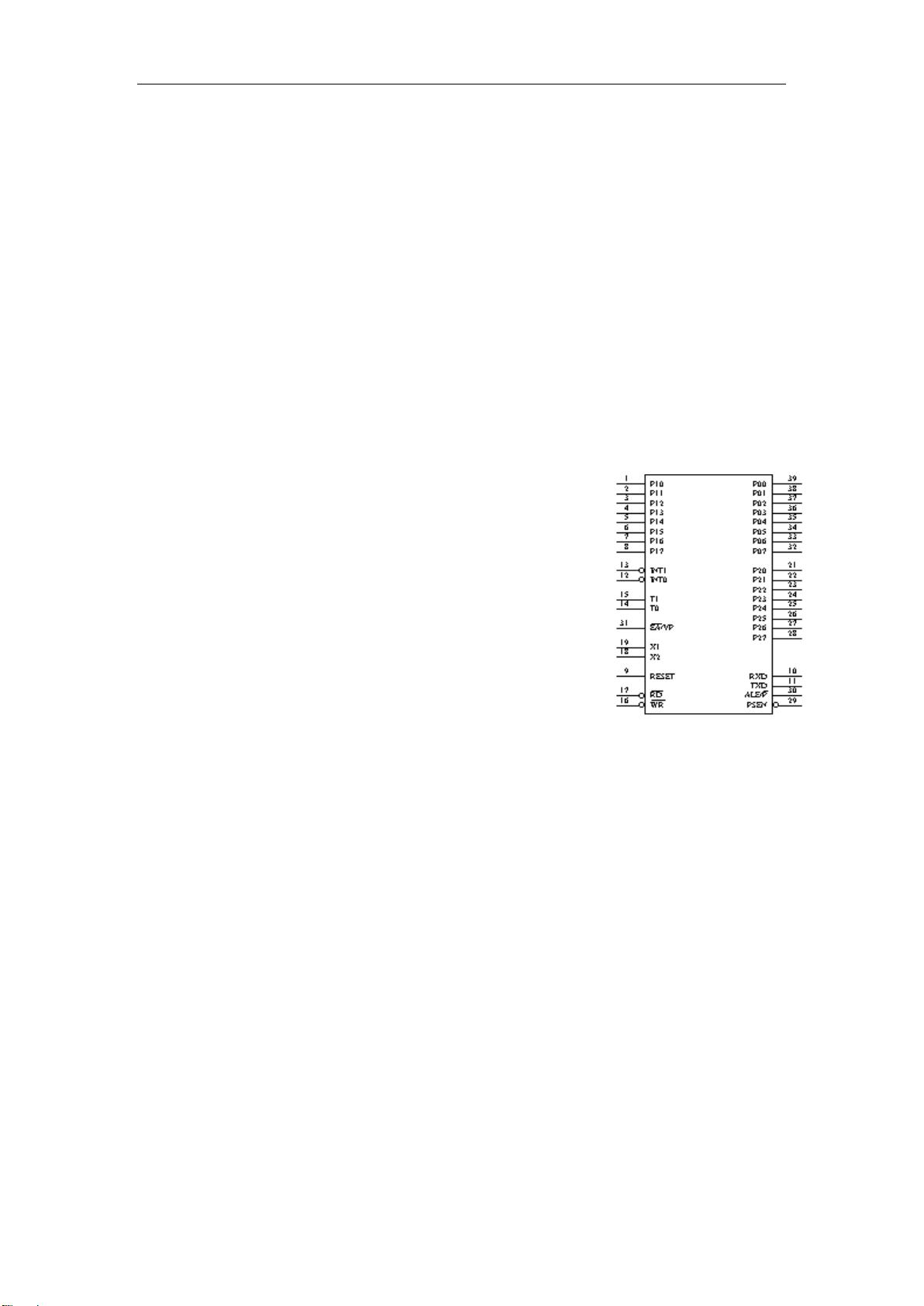

The graduation thesis "Frequency Synthesis Design Based on 51 Single Chip Microcomputer" is a comprehensive study on the design and implementation of a frequency synthesis system. The system is centered around the 51 single chip microcomputer and includes modules for sine signal generation, power amplification, amplitude modulation (AM), frequency modulation (FM), digital key control (ASK, PSK), and test signal generation. The system utilizes digital control to generate sine signals in the range of 0Hz to 30MHz using a DDS chip AD9850. The generated signal is then amplified and filtered to a 6V output with a certain driving capability. Additionally, the system is capable of modulating the 1kHz sine signal generated by the test signal module through AM and FM modules, as well as producing binary PSK or ASK signals through the digital key control module. It also includes the functionality for demodulating ASK signals to recover the original digital sequence. The system aims for simplicity, easy adjustment, and comprehensive functionality, and has achieved stable waveform output and high accuracy. It also features an LED display screen and keyboard to provide a user-friendly human-machine interface. The key technologies and components involved in the system are direct digital frequency synthesis (DDS), AD9850, phase-locked loop (PLL), and voltage-controlled oscillator (VCO). This thesis presents a detailed exploration of the system’s design, performance, and practical application. Overall, the system represents a significant accomplishment in the field of frequency synthesis and digital signal processing. Keywords: direct digital frequency synthesis (DDS), AD9850, phase-locked loop (PLL), VCO, amplitude modulation (AM), frequency modulation (FM), digital key control (ASK, PSK).

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-04 上传

2024-03-23 上传

2023-06-28 上传

2021-09-27 上传

2021-09-18 上传

2023-07-02 上传

黑色的迷迭香

- 粉丝: 787

- 资源: 4万+

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新