Verilog逻辑设计:有限状态机在ASIC中的应用

版权申诉

22 浏览量

更新于2024-07-03

收藏 504KB PPT 举报

"HDL语言与ASIC原理:Verilog逻辑设计实例系列五---有限状态机(1).ppt"

本文将深入探讨有限状态机(Finite State Machine, FSM)在电子设计自动化(EDA)中的应用,特别是在Verilog HDL语言中的实现。有限状态机是一种描述和设计时序逻辑电路的有效方法,它在计算机科学、硬件设计和工程领域中有着广泛的应用。

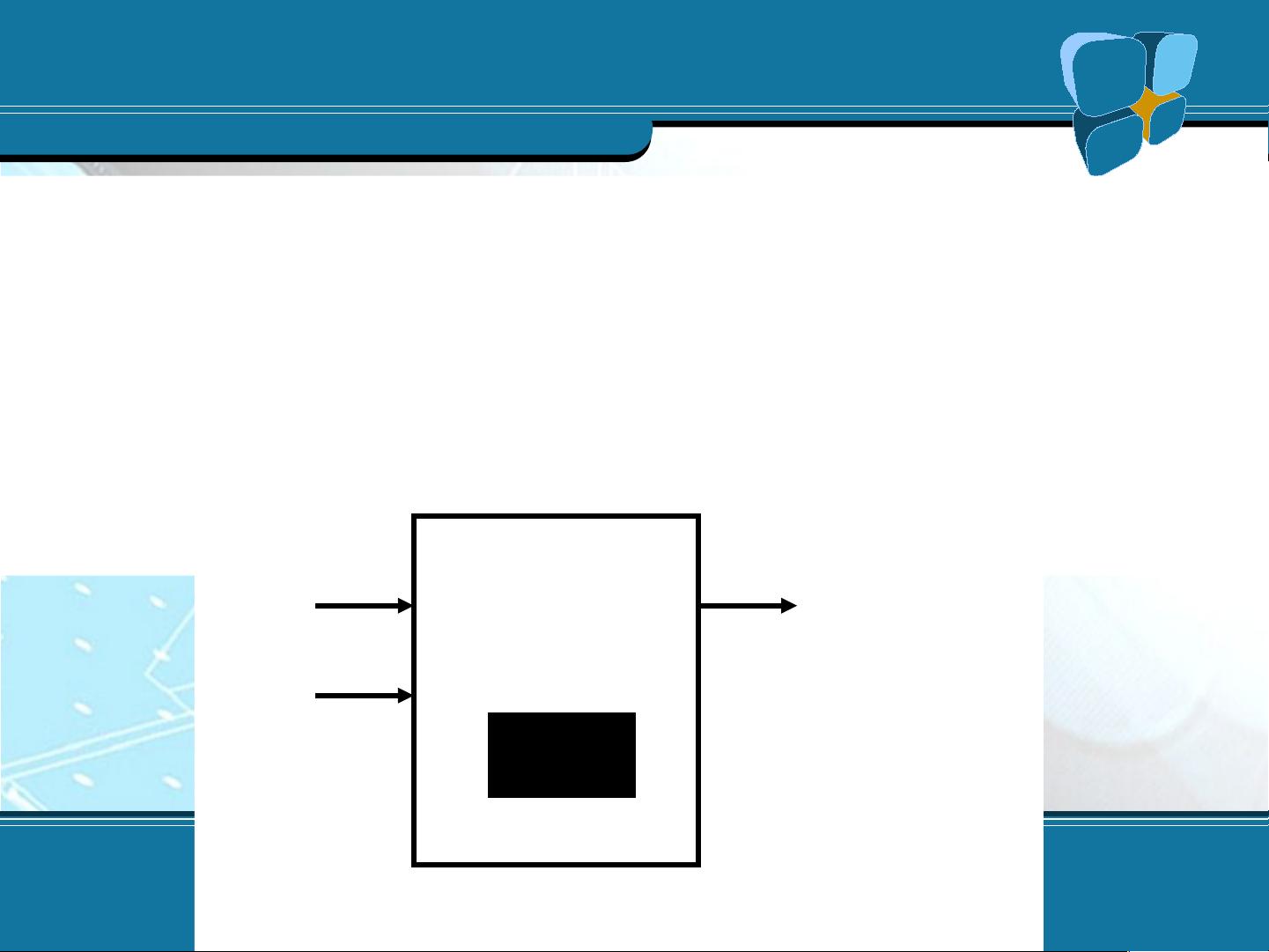

首先,有限状态机的基本概念是通过一系列状态来表示系统的动态行为。在设计时序电路时,状态机的当前状态和输入信号共同决定下一个状态,同时根据状态和/或输入产生相应的输出。状态机通常分为 Moore型和Mealy型。Moore型状态机的输出仅依赖于当前状态,而Mealy型状态机的输出则取决于当前状态和输入。

以一个简化的闹钟系统为例,这个系统可以被建模为一个三状态的状态机:Sleeping(睡眠中)、AwakeButInBed(醒了但还在床上)和Up(起床)。系统有两个输入:Alarm(闹钟)和IsWorkday(是否为工作日)。输出只有一个,即TurnOffAlarm(关掉闹钟)。这个例子展示了如何将现实生活中的情景转化为状态机模型。

在实际的设计流程中,状态机的行为首先通过状态图和状态表进行描述,随后使用HDL语言(如Verilog)将其编码为数字电路。Verilog是一种硬件描述语言,能够用来定义、仿真和综合数字逻辑电路,包括复杂的状态机。通过编写Verilog代码,可以精确地控制状态机的转换规则和输出逻辑。

在计算机架构中,有限状态机扮演着至关重要的角色,尤其是在微处理器的设计中。微处理器的控制单元就是一个典型的有限状态机,它接收指令和标志寄存器的值作为输入,根据这些输入产生控制信号,协调处理器的各个部分(如寄存器、算术逻辑单元)执行指令。控制单元的这种行为可以通过精心设计的状态机逻辑来实现。

有限状态机是理解和设计复杂时序系统的关键工具,它能够帮助工程师将抽象的行为描述转化为具体的硬件实现。无论是简单的电路还是复杂的微处理器,有限状态机都提供了一种高效且灵活的设计方法。在Verilog等HDL语言的支持下,设计者可以方便地将状态机模型转化为实际的数字电路,从而实现各种各样的电子系统。

2022-06-21 上传

2022-06-22 上传

2015-12-08 上传

273 浏览量

2018-08-17 上传

2022-11-13 上传

2012-10-30 上传

2008-10-07 上传

2010-03-03 上传

智慧安全方案

- 粉丝: 3834

- 资源: 59万+

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用