Vivado HLS视频课程学习关键点解析

需积分: 36 101 浏览量

更新于2024-07-16

1

收藏 8.84MB PDF 举报

“XILINX官方HLS视频课程学习总结.pdf”主要涵盖了Xilinx的Vivado High-Level Synthesis (HLS)工具的使用和优化技巧,旨在帮助软件工程师理解和应用FPGA设计。

该课程首先从软件工程师的角度出发,解释了FPGA(Field-Programmable Gate Array)架构的基本原理,帮助学员理解硬件描述语言(如Verilog或VHDL)与高级语言(如C/C++)在FPGA设计中的差异。FPGA的并行处理能力使得它在计算密集型任务中具有优势,而HLS工具则提供了将高级语言代码转化为FPGA逻辑的途径。

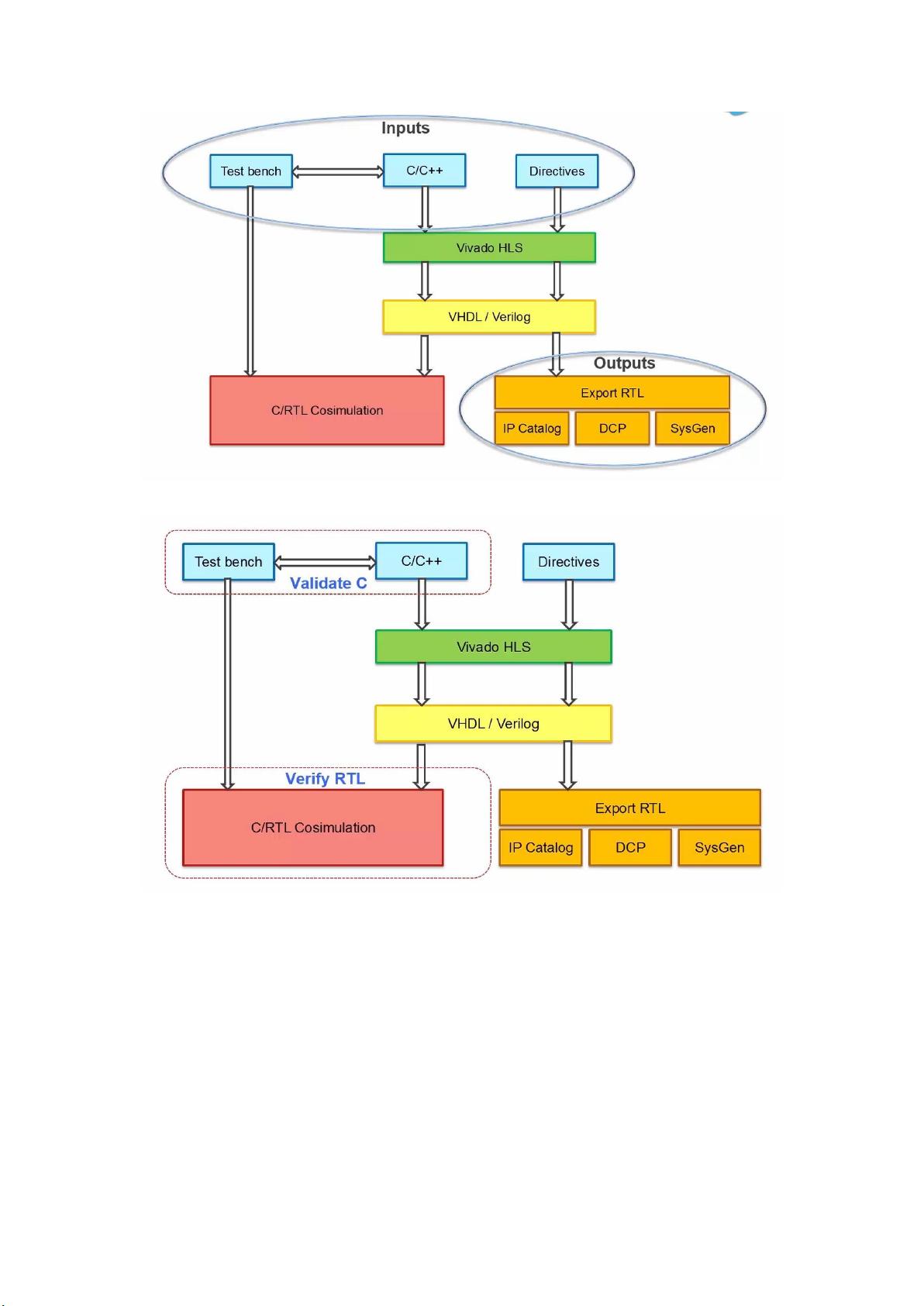

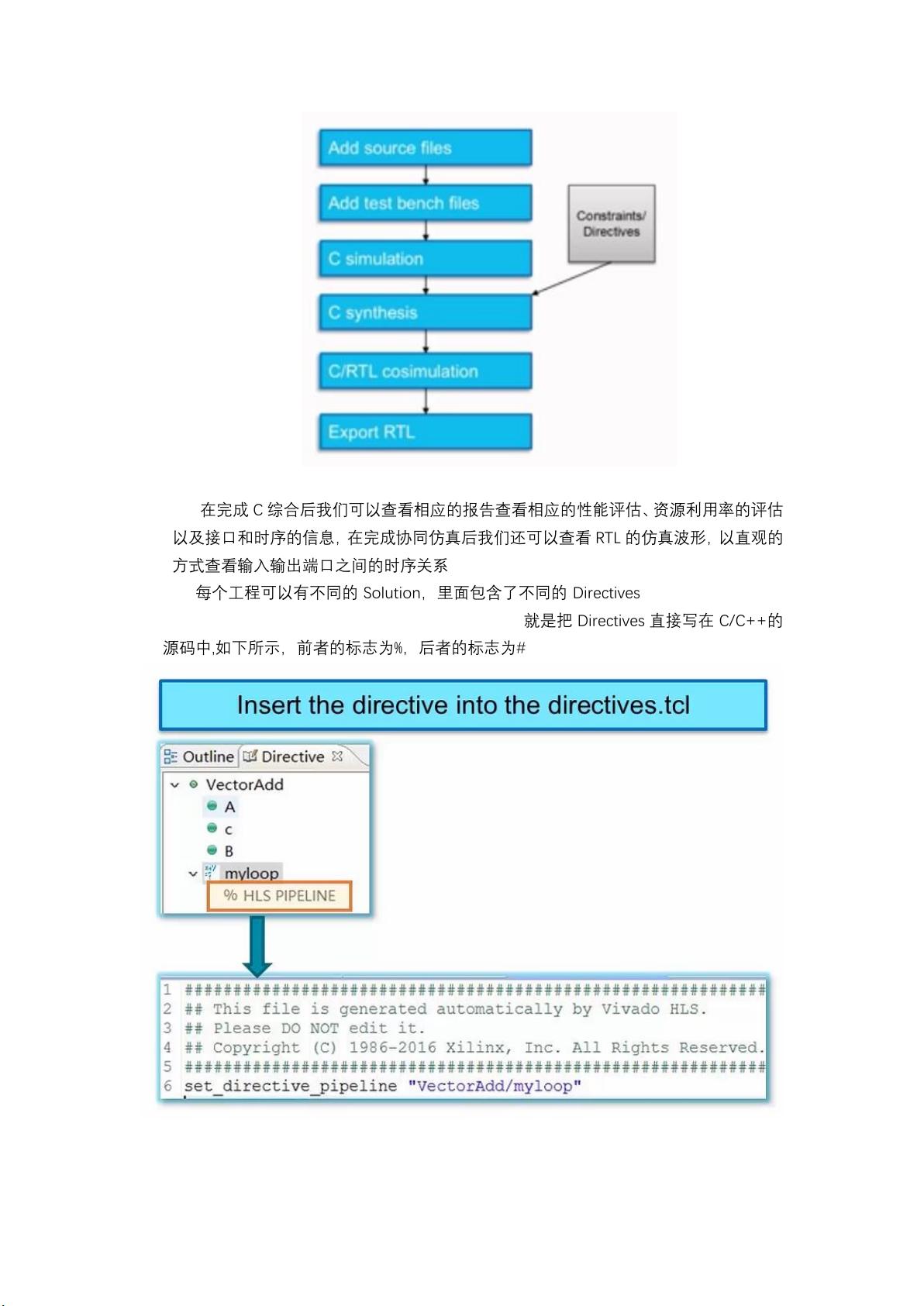

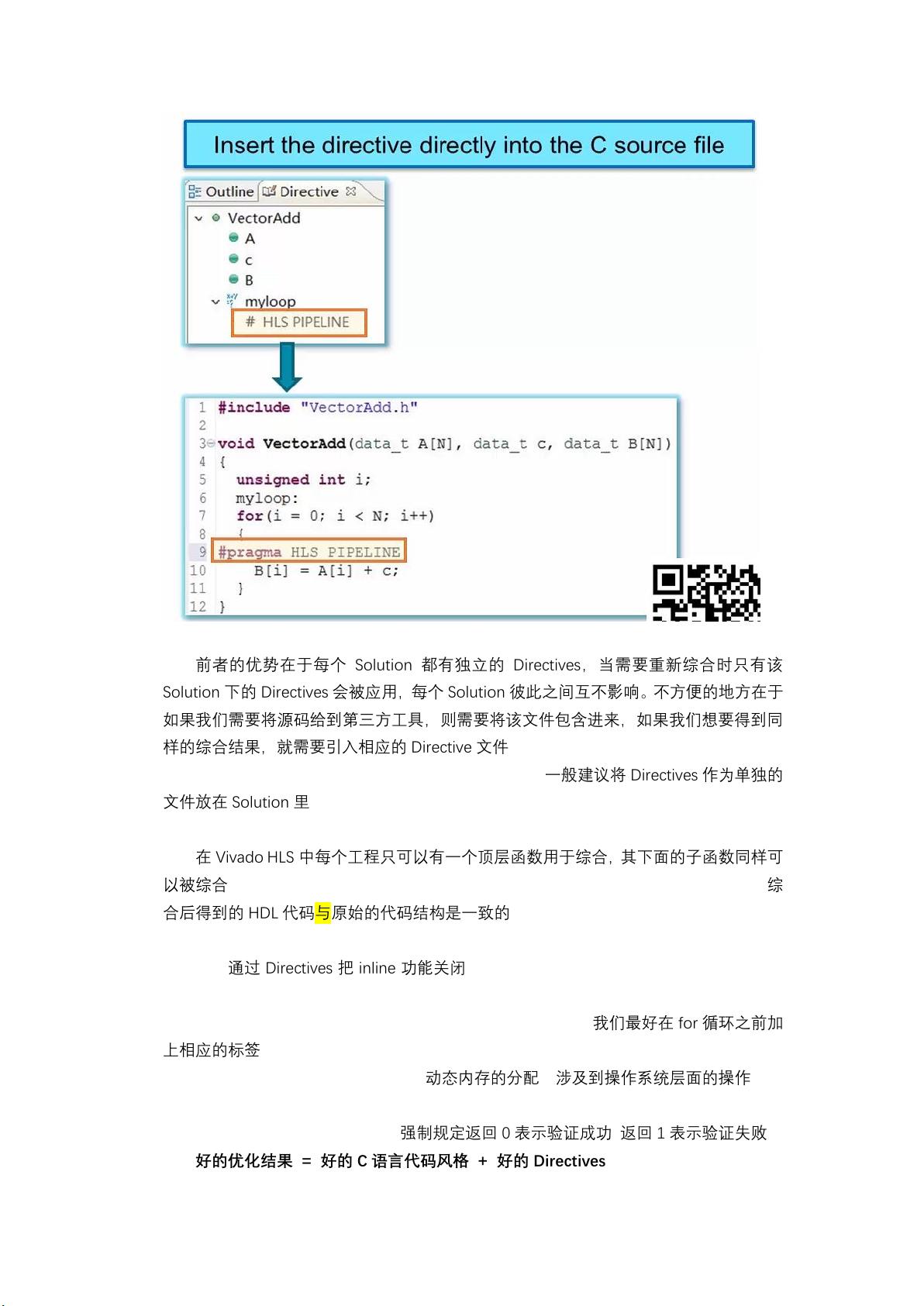

Vivado HLS的工作机制是将C/C++代码转换为硬件逻辑,这一过程包括了代码分析、优化和生成RTL(Register Transfer Level)代码。课程详细介绍了HLS设计流程,包括从创建项目、编写源代码、配置约束、执行合成到查看报告的各个步骤。

在数据类型部分,课程讲解了C语言支持的多种数据类型,如整型、浮点型以及任意精度数据类型,并讨论了如何在Vivado HLS中使用`sizeof()`函数来确定数据类型的大小。此外,还介绍了如何在Visual Studio中配置支持任意精度数据类型。课程还深入到数组类型转换,包括变量的定义、初始化,定点和浮点数据类型的使用,以及数据类型转换的规则,包括隐式和显式转换。

课程进一步探讨了Vivado HLS中的复合数据类型,如结构体和枚举类型,这些都是在进行复杂数据组织时非常重要的概念。接着,讲解了测试平台的基本架构,包括TestBench和CTestBench的创建和使用,以及如何生成测试激励和进行输出检测。

接口综合是HLS中的关键环节,课程讲解了从块级接口协议到端口级接口协议的基本概念,并通过实例展示了如何处理数组接口和进行指令优化。课程还详细讨论了for循环的各种优化技术,包括基本性能指标、流水线、展开、循环合并、数据流优化,以及处理嵌套for循环的方法。最后,课程提到了其他优化方法,如利用HLS的特性对for循环进行更高级别的调整。

通过这门课程,学员将掌握使用Vivado HLS进行高效FPGA设计的基本技能,了解如何将软件思维应用于硬件实现,从而提升FPGA设计的效率和性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-12-14 上传

2021-11-08 上传

2020-03-31 上传

2021-10-12 上传

2021-03-28 上传

2022-09-24 上传

long游天下

- 粉丝: 31

- 资源: 31

最新资源

- 土木工程毕业设计——【8层】8400平米综合办公楼毕业设计(含计算书,建筑、结构图,施组).zip

- 技术交底及其安全资料库-混凝土泵送安全操作规程技术交底

- mnist-original数据

- WWDC2015IntroPlayground:尝试使用Core Animation重新创建WWDC 2015简介视频

- AndroidFreetypeSample:Android Freetype示例

- 很不错的Java计算器源码.zip

- pyFormex-开源

- KendoUI-Admin-Site-master.zip

- 前端阿彬的站点。 各种工具的配置枚举列表; 各种好用的工具汇总; 一些小游戏,特效.zip

- 房地产工程-营销策划类-成都市五块石商业地产-赫杰斯顾问24DOC

- 土木工程毕业设计——【8层】5171.22㎡8层住宅建筑工程预算书及施组(建筑、结构图纸).zip

- react对SCLAlertView-Swift包的本地React-JavaScript开发

- Predicting-Lead-Score:在这里有一个python笔记本。 任务是预测公司营销团队产生的线索的得分或质量。 这有助于销售部门对销售线索进行排序,并可以分析他们必须首先击中哪些销售线索。 在此算法中,我使用了---> RandomForestRegressor(Accuracy = 0.678),Gradient Boosting Regressor(Accuracy = 0.699)

- code-together:实时在线网络应用

- watsonwork-dilbert-bot:搜索迪尔伯特漫画

- Python库 | indy_crypto-0.5.1-rc-1.tar.gz