使用Vivado HLS进行FPGA设计入门

下载需积分: 10 | PDF格式 | 1.31MB |

更新于2024-07-16

| 26 浏览量 | 举报

"ug998-vivado-intro-fpga-design-hls.pdf" 是一份介绍使用Vivado高层面综合(HLS)进行FPGA设计的文档,版本为v1.1,发布日期为2019年1月22日。这份文档主要面向软件工程师,帮助他们理解如何将软件模型或原型转换为适合不同硬件平台的实施项目,特别是FPGA(现场可编程门阵列)。

FPGA设计与Vivado HLS

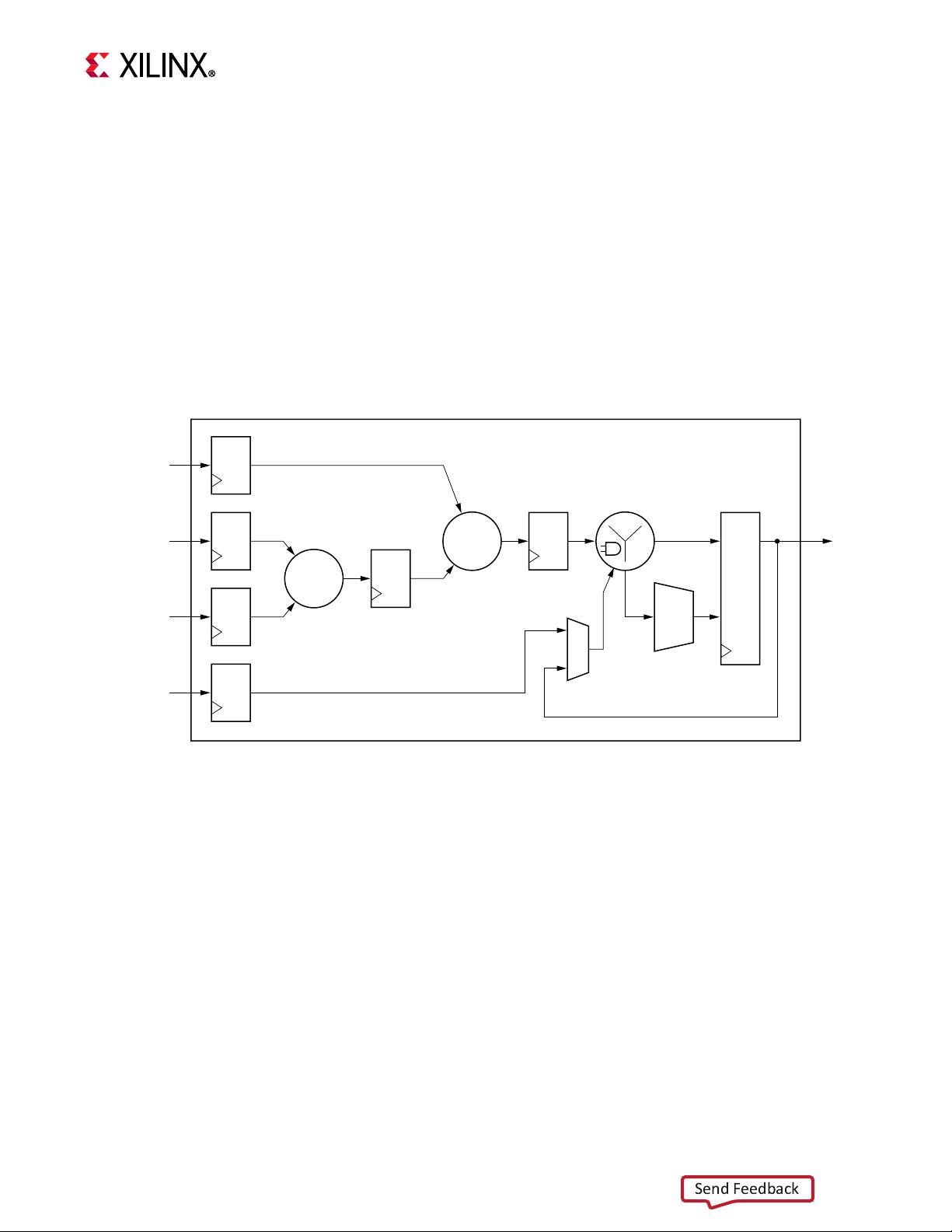

Vivado HLS是一种工具,它允许软件工程师以高级语言(如C、C++或SystemC)编写设计,并自动将其转换为硬件描述语言(如VHDL或Verilog),进一步用于FPGA的配置。这种技术称为高层面综合,它简化了传统硬件描述语言的复杂性,使得设计过程更加接近软件开发的流程。

文档的修订历史

文档的最新版本1.1在2019年1月22日发布,包含了编辑性的更新以及对DSP块的更新信息,新增了关于UltraRAM的内容。初版则在2013年7月2日发布。

主要内容概述

1. **介绍**:这部分提供了一个概述,解释了FPGA设计的基本概念,以及为什么软件工程师会考虑使用Vivado HLS。

2. **什么是FPGA?**:这部分深入介绍了FPGA的架构,强调其并行处理能力与处理器架构的区别。

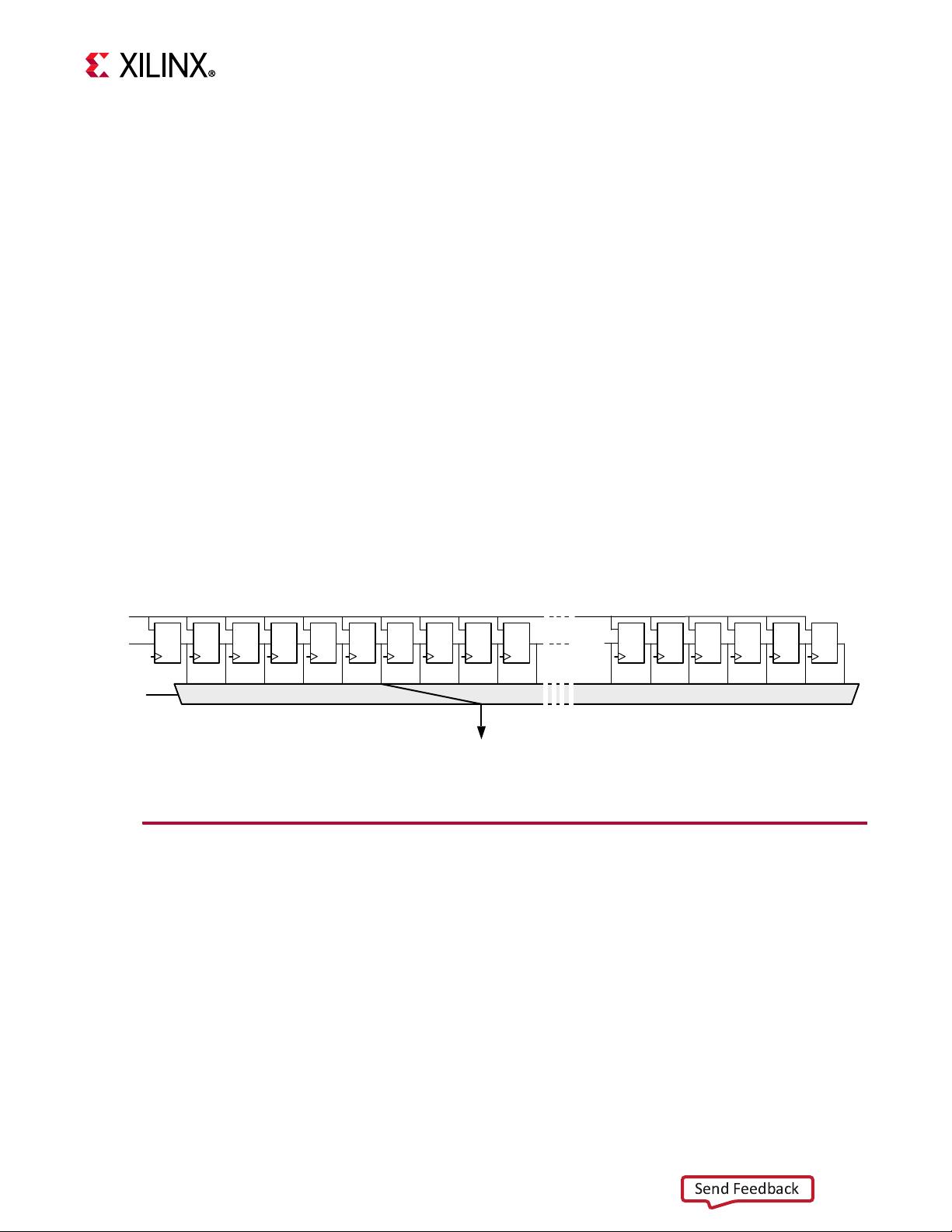

3. **硬件设计基础**:讨论了时钟频率、延迟和流水线、吞吐量以及内存架构和布局等关键硬件设计概念。

4. **Vivado HLS基础**:涵盖了Vivado HLS支持的操作,如条件语句、循环、函数以及动态内存分配等。

通过学习这份文档,读者可以了解到如何利用Vivado HLS来创建高效能的FPGA设计,以及如何利用软件工程的思维来优化硬件实现。这包括了理解如何处理控制流、数据流以及内存管理,这些都是在设计FPGA系统时至关重要的因素。同时,文档还介绍了FPGA架构的优势,例如其高度可配置性和并行处理能力,这些都是传统处理器无法比拟的。

在实际应用中,FPGA设计能够满足高性能、低延迟和定制化的需求,特别是在通信、娱乐、游戏和医疗等领域。通过Vivado HLS,软件工程师能够更快速地将软件原型转化为适用于FPGA的硬件实现,从而加速产品上市时间。

相关推荐

礼茶的贤

- 粉丝: 196

最新资源

- 编程精粹:打造无错C程序的微软技术

- 微软软件测试方法探索与实践经验

- Windows Sockets编程规范与实战指南

- MySQL 5.0中文参考手册:安装与升级指南

- Java Web Start技术详解与应用

- 嵌入式C/C++编程精华:从基础到实战深度解析

- Windows上配置PHP5.2.5+Apache2.2.8+MySQL5+phpMyAdmin详细教程

- 硬盘优化与故障处理全攻略:提升速度与寿命

- ArcGIS Engine入门教程:从基础到应用

- Spring入门:理解IoC与DI基础

- Linux Socket编程基础:接口、功能与实例

- 理解SDRAM内存:物理Bank与逻辑Bank详解

- 配置AD与Domino目录同步:步骤与指南

- Flex 2.0安装与开发环境搭建指南

- Subversion版控教程:从入门到高级操作详解

- 自制验证码生成器:简单实现与应用