Verilog 数字系统设计:RTL综合与验证

需积分: 9 113 浏览量

更新于2024-07-26

收藏 2.91MB PDF 举报

"《Verilog 数字系统设计》是一本由Zainalabedin Navabi博士编著的关于Verilog语言在数字系统设计中的应用书籍,涵盖了RTL级综合、测试平台构建以及验证等内容。该书是Verilog学习的经典之作,共402页,对于学习和掌握Verilog设计是必备的参考资源。"

本书详细介绍了Verilog硬件描述语言在数字系统设计中的应用,主要分为以下几个关键知识点:

1. **Verilog基础知识**:首先,书中会讲解Verilog的基本语法和结构,包括数据类型、运算符、赋值语句、进程(process)等,这些都是编写Verilog代码的基础。

2. **模块化设计**:Verilog强调模块化设计思想,书中会讲述如何通过定义模块来组织复杂的数字系统,包括输入输出接口、参数化模块、例化等概念。

3. **逻辑操作与组合电路**:书中会详细介绍如何使用Verilog描述组合逻辑电路,如门电路、函数表达式、条件生成等,帮助读者理解逻辑电路的工作原理。

4. **时序电路设计**:时序电路是数字系统的核心部分,书中将讲解寄存器、触发器、时钟同步、异步信号处理等,让读者学会创建时序逻辑。

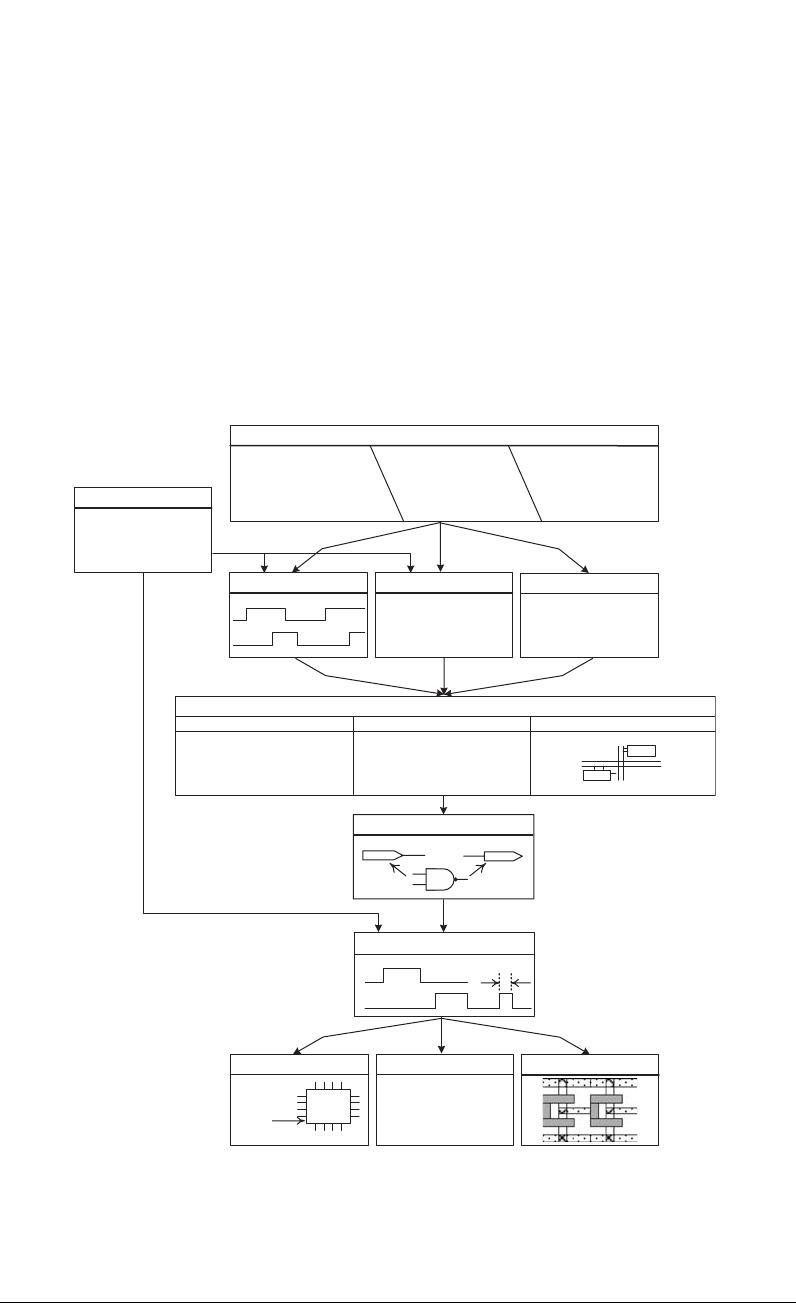

5. **RTL级综合**:RTL(Register Transfer Level)综合是将高级设计语言转换成门级网表的过程,书中会介绍这一过程及其优化策略,以提高设计效率和性能。

6. **测试平台与验证**:测试平台的构建是确保设计正确性的重要步骤,书中会教授如何编写测试向量、搭建仿真环境、使用断言进行形式验证等技术。

7. **IP核与系统级集成**:随着SoC(System on Chip)的发展,IP核的复用变得至关重要,书中可能涵盖IP核的导入、封装以及多模块系统的集成方法。

8. **实例分析**:书中会提供大量实例,从简单到复杂,帮助读者深入理解理论知识,并能将其应用到实际设计中。

9. **设计流程与工具**:介绍VHDL/Verilog设计流程,包括设计输入、综合、布局布线、仿真验证、FPGA/CPLD实现等步骤,以及相关的设计工具如Xilinx ISE或 Altera Quartus II的使用。

10. **版本控制与团队协作**:在工程实践中,版本控制工具如Git的应用和团队间的协作技巧也是重要的一环,可能会在书中有所提及。

这本书是Verilog学习者的宝贵资源,它不仅提供了扎实的理论基础,还强调了实践应用,帮助读者从理论到实践全面掌握Verilog数字系统设计。对于电子工程和计算机工程专业的学生以及从事硬件设计的工程师来说,这是一本不可或缺的参考书。

2009-04-23 上传

143 浏览量

2022-09-24 上传

102 浏览量

2021-10-03 上传

stanleywhliu

- 粉丝: 0

最新资源

- Cairngorm中文版:Flex应用设计指南

- ThinkPHP 1.0.0RC1 开发者手册:框架详解与应用构建

- ZendFramework中文手册:访问控制与认证

- 深入理解C++指针:从基础到复杂类型

- Java设计模式详解:从基础到高级

- JavaScript高级教程:深入解析基础与对象

- Qt教程:从Hello World到GUI游戏开发

- RealView编译工具链2.0:链接程序与实用程序深度解析

- Unicode编码与.NET Framework中的实现

- Linux内核0.11完全注释 - 赵炯

- C++ 程序设计员面试试题深入分析与解答

- Tomcat深度解析:配置、应用与优势

- 车辆管理系统:全面解决方案与功能设计

- 使用JXplorer连接Apache DS LDAP服务器指南

- 电子商务环境下的企业价值链分析及增值策略

- SAP仓库管理系统详解:灵活高效的库存控制